STMicroelectronics et la technologie photonique

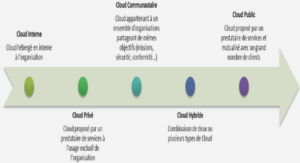

STMicroelectronics (ST) se positionne comme l’un des leaders mondiaux des fabricants de semi-conducteurs. ST fournit à ses clients des solutions innovantes pour tous les secteurs d’applications de l’électronique et couvre notamment les marchés du « nouvel Internet ». La société est impliquée dans le développement du « smart driving », « smart home and city », « smart things » et « smart industry» comme illustré à la Figure 0.1. Par exemple, des produits phares développés par ST incluent l’aide à la conduite des voitures, le contrôle du chauffage et de l’énergie des maisons, la gestion de l’éclairage d’une ville, le déploiement de la réalité virtuelle, les communications entre machines ou homme – machine d’une chaîne de production, etc… L’arrivée de ces nouvelles technologies est permise par l’évolution des datacenters et le développement du cloud computing. ST cherche donc également à apporter des solutions pour déployer les réseaux de communications efficacement. En effet, nous assistons actuellement à une explosion du trafic de données échangées, accompagnée d’une réorganisation de l’architecture des datacenters afin de supporter des densités de bande passante très élevées.

La technologie photonique consiste à générer, traiter, transmettre et détecter un signal de données où ce signal est porté par la lumière (les photons). La photonique sur silicium utilise les procédés standards de la microélectronique pour fabriquer les composants optiques en silicium. Cette technologie permet potentiellement d’apporter des solutions aux problématiques des datacenters car les communications optiques permettent de dépasser les limitations des interconnexions électriques. C’est dans ce cadre que STMicroelectronics développe depuis 2012 sa plateforme photonique, appelée PIC25G (Photonic Integrated Circuit 25 Gbps), à partir d’une collaboration avec Luxtera. L’offre en termes de composants élémentaires passifs et actifs est relativement large mais il s’agit maintenant d’assurer la montée en maturité de ces composants pour permettre la production de la technologie. Une seconde plateforme, nommée PIC50G (Photonic Integrated Circuit 50 Gbps), est également développée depuis 2017 en partenariat avec le CEA-LETI et Finisar. Elle permet d’adresser de nouvelles fonctionnalités ainsi que des vitesses de communications plus élevées . La technologie PIC50G permet plus de flexibilité sur le design des composants car elle intègre différentes formes de guides d’onde ainsi que des guides en nitrure de silicium. De plus, le couplage des fibres optiques peut être réalisé par couplage adiabatique ce qui permet un transfert de la lumière sur une large bande passante (100 nm) comparé au couplage par la surface avec des réseaux (GC grating coupler) (30 nm).

Les produits actuels développés par STMicroelectronics sont essentiellement des modules 100 Gb/s, basés sur les normes MSA (Multi Source Agreement) et le facteur de forme QSFP28 (Quad Small Form-factor Pluggable). Ils sont issus de la technologie PIC25G qui est depuis 2016 une réalité industrielle. La technologie PIC50G est, quant à elle, encore au stade de la R&D. Ces produits sont destinés aux communications longue distance présentes dans un datacenter. Mais, la photonique est également attendue pour d’autres types de communications avec l’introduction de l’interposeur photonique pour les équipements et infrastructures des réseaux de la prochaine génération. Si la stratégie d’intégration envisagée dès 2012 est un assemblage 3D entre les puces électrique et optique, l’intégration est amenée à se complexifier au fur et à mesure du développement de la technologie. En effet, les prochains modules embarqueront directement les IP photoniques (le circuit optique OIC et le circuit électrique associé EIC) au plus proche de l’ASIC (Application-Specific Integrated Circuit) ce qui permettra d’améliorer les performances globales des communications optiques.

Développement d’une IP pour les modules front panel

Les modules front panel basés sur les accords MSA constituent l’objectif à court – moyen terme de STMicroelectronics. Ces modules sont destinés aux communications à longue distance au sein d’un datacenter (de 100 m à 1 km environ) et sont composés d’un transceiver électro-optique permettant les conversions EO (électrique → optique) et OE (optique → électrique). L’architecture du module front panel est ainsi relativement simple et ne comprend qu’une puce optique (OIC : modulateur et photodiode) et une puce électrique (EIC : driver et amplificateur transimpédance (TIA)) servant au contrôle des composants photoniques. Les deux puces sont intégrées par une méthode 3D comme un assemblage flip-chip.

Actuellement ST produit et vend des modules 100G et 200G mais des modules 400G sont envisagés pour suivre l’évolution des standards et rester compétitif sur ce marché. Comme nous le décrirons dans le chapitre suivant, ces transceivers 400G nécessitent de développer des composants de base à un débit de 50 Gb/s, supportant des formats de modulation PAM4 (Pulse Amplitude Modulation) et du multiplexage spatial (PSM Parallel Single Mode) ou en longueur d’onde (WDM Wavelength Division Multiplexing).

Pour réaliser ses circuits optiques, ST base essentiellement son expérience sur les modulateurs de Mach-Zehnder. Ce sont donc ces composants qui seront développés également pour les modules 400G afin de capitaliser sur les conceptions précédentes. Quant aux circuits électriques, la technologie phare de ST est actuellement le BiCMOS 55 nm pour les applications photoniques. Mais elle sera certainement amenée à évoluer vers une technologie CMOS ou FDSOI (C28 ou 28FDSOI) pour les applications 400G afin de bénéficier d’une meilleure efficacité énergétique.

Applications I/O optiques et interposeur photonique

Le développement des I/O optiques et l’introduction d’un interposeur photonique constituent l’objectif à long terme de STMicroelectronics. Ces nouveaux modules seront également destinés aux communications intra-datacenter dans un premier temps. Mais ils pourront évoluer très facilement vers d’autres applications et notamment les communications à courte distance entre deux puces, toutes deux intégrées sur l’interposeur photonique (distance de quelques centimètres). Dans cette thèse, nous nous intéresserons tout particulièrement aux interconnexions chip-to-chip et nous prendrons l’exemple d’un lien entre un processeur et un bloc mémoire pour illustrer nos propos.

L’interposeur optique inclut un transceiver électro-optique pour les conversions EO et OE comme les modules front panel mais son architecture est celle d’un block multi-chip (MCM Multi-Chip Module) comprenant également l’ASIC principal, et éventuellement d’autres IP (Intellectual Property). L’intégration des différentes puces est toujours réalisée par une méthode 3D permettant d’empiler les puces. Deux architectures principales peuvent être envisagées. La première reprend l’architecture de base du module front panel et intègre l’ASIC au plus proche de l’EIC. La seconde intègre directement l’EIC au sein de l’ASIC pour ne constituer qu’une seule puce. Ce niveau d’intégration supérieur pourrait permettre d’améliorer les performances de l’interconnexion.

L’une des caractéristiques principales des I/O optiques est de pouvoir supporter des débits de transmission très élevés. L’optimisation de la bande passante des interconnexions est alors réalisée en fonctions des technologies optique et électrique disponibles afin de minimiser la dissipation de puissance. Actuellement, nous estimons que le débit optimal des composants en termes d’énergie est autour de 20 Gb/s mais les développements futurs pourraient permettre d’envisager à long terme un débit optimal de 50 Gb/s.

|

Table des matières

Introduction

0.1. STMicroelectronics et la technologie photonique

0.2. Motivations de la thèse

0.2.1 Développement d’une IP pour les modules front panel

0.2.2 Applications I/O optiques et interposeur photonique

0.3. Objectifs de la thèse

Chapitre 1 Etat de l’art

1.1. Modules MSA – Communications à longue distance

1.2. I/O optiques – Communications chip-to-chip

1.2.1 I/O optiques

1.2.2 Interposeur photonique : exemple des technologies HMC et HBM

1.3. Transmetteurs 50 Gb/s

1.3.1. Modulateur optique

1.3.2. Driver électrique

1.3.3. Système de transmission à débit élevé

1.4. Intégration hybride

Chapitre 2 Modélisation des modulateurs électro-optiques

2.1. Modélisation de la jonction PN

2.2. Le modulateur de Mach-Zehnder

2.2.1. Présentation générale du MZM

2.2.2. Exemple de caractérisation d’un MZM

2.3. Le modulateur en anneau

2.3.1. Présentation générale du composant

2.3.2. Modélisation de l’anneau : équations du résonateur

2.3.3. Modèle analytique du modulateur en anneau

2.3.4. Validation du modèle – Caractérisation du spectre de transmission

2.4. Modèle électrique des modulateurs électro-optiques

Chapitre 3 Conception des modulateurs en anneau

3.1. Optimisation de la bande passante pour des débits de 50 Gb/s

3.2. Conception des structures de tests

3.3. Caractérisation expérimentale

3.3.1. Caractérisation optique statique

3.3.2. Mesures dynamiques

3.3.3. Caractérisation RF et mesure de la bande-passante électro-optique

Chapitre 4 Conception du driver

4.1. Optimisation du compromis vitesse-énergie

4.1.1. Architecture

4.1.2. Dimensionnement

4.1.3. Choix de la technologie

4.1.4. Conception et layout des circuits

4.1.5. Simulations

4.2. Mesures et rétro-simulations

4.2.1. Structures de test

4.2.2. Montage expérimental

4.2.3. Diagrammes de l’œil

4.2.4. Performance des drivers et comparaison avec l’état de l’art

4.3. Implémentation de protections ESD

Chapitre 5 Co-intégration électro-optique : Assemblage par wire-bonding

5.1. Etude système – Optimisation d’une interconnexion optique SDM

5.1.1. Architecture du lien SDM

5.1.2. Contraintes de bande passante et de surface

5.1.3. Optimisation de la consommation de puissance en fonction des performances du modulateur

5.2. Réalisation d’un transmetteur hybride à base de MZM

5.2.1. Intégration hybride du driver et d’un modulateur de Mach-Zehnder

5.2.2. Cosimulations électro-optiques du transmetteur

5.2.3. Caractérisation expérimentale

5.3. Application des modules à l’étude de la fiabilité

Chapitre 6 Vers le développement d’un démonstrateur WDM, 20G, 3D

6.1. Etude système – Optimisation d’une interconnexion optique

6.1.1. Cadre de l’étude – Architecture du lien

6.1.2. Exemple du bilan de consommation d’énergie à 10 Gb/s

6.1.3. Optimisation du système de transmission en fonction du débit unitaire

6.2. L’assemblage par micro-piliers en cuivre

6.2.1. Analyse des phénomènes thermomécanique et photo-élastique

6.2.2. Description du modèle COMSOL

6.2.3. Résultats des simulations COMSOL

6.2.4. Conception des structures de tests

6.3. Simulations et conception des liens WDM

6.3.1. Théorie sur les liens WDM

6.3.2. Simulation électro-optique des liens WDM : Estimation de la pénalité de diaphonie

6.3.3. Conception des liens WDM pour le démonstrateur WDM

6.4. Conception du démonstrateur

Conclusion