Télécharger le fichier pdf d’un mémoire de fin d’études

L’instrument reconfigurable

L‟instrument reconfigurable a une carte mère (la principale carte mère du RVI) et deux cartes filles. La carte mère est faite d‟un FPGA à capacité moyenne ou grande et quatre blocs : le bloc de communication de port, extension mémoire, outils de débogage, et d‟autres outils variés.

Le logiciel est une collection des modules indépendants organisés hiérarchiquement. Chaque module opère sur des fichiers indépendants contenant les informations relevées : données, commandes, messages d‟erreur. Dans le système RVI, les opérations gourmandes en temps d‟exécution sont à la charge de l‟instrument reconfigurable tandis que les autres opérations sont exécutées par le logiciel.

Généralement, le logiciel fournit :

– Une interface graphique du RVI

– Une librairie des instruments virtuels avec ses propres interfaces.

– Des possibilités de stockage des données

– L‟établissement de la communication automatique avec l‟instrument virtuelle à chaque fois que l‟utilisateur choisit un instrument (driver).

Le code de la description matérielle est écrit en langage VHDL. Une description matérielle est divisée en quatre blocs de base :

Un module de communication ;

Une mémoire et des registres pour communiquer avec les cores ;

Les cores de l‟instrument;

Une description des utilisations des ports.

Optionnellement, le système peut disposer des modules SDRAM extérieurs, des circuits logiques analyseurs et générateur stimuli pour déboguer l‟exécution.

Le module de communication par port supporte les protocoles de base de connexion à un protocole haut niveau RVI spécifique pour manier l‟instrument virtuel. La communication entre le PC et le core de l‟instrument s‟effectue de deux manières :

La première est par lecture et écriture des données dans la mémoire dual port. Le PC accède la mémoire par un port et le core de l‟instrument par l‟autre port.

La deuxième manière est par lecture et écriture dans les registres. Certains registres sont en lecture seule pour le core de l‟instrument et certains autres en lecture seule pour le PC. Quelques registres sont réservés pour contrôler le protocole de communication de l‟RVI, donc ne sont pas disponibles pour des usages généraux.

Suivant la nature des ports et du core de l‟instrument, l‟instrument reconfigurable peut envoyer une demande d‟interruption au PC pour déclencher une action particulière. Aussi le PC peut vérifier des registres spécifiques pour savoir s‟il y a une requête pour une certaine action. Le PC peut aussi utiliser des registres pour passer des commandes et des paramètres aux cores de l‟instrument. L‟échange des données par registres peut être utilisé pour implémenter un mécanisme permettant à des accès simultanés de la mémoire dual port. Cet échange peut aussi être utilisé pour contrôler l‟accès à la mémoire externe.

Afin d‟intégrer un core d‟un instrument reconfigurable dans un système RVI, ce core doit se conformer à l‟interface standardisée du bloc de communication PC-FPGA et le bloc d‟interfaçage des matériels extérieurs. Il doit aussi se conformer à un mécanisme commun d‟interaction. Quand les trois blocs principaux (le bloc de communication PC-FPGA, le core de l‟instrument, l‟interface des matériels extérieurs) respectent ces conditions, alors chaque bloc pourra être modifié ou mis à jour indépendamment et pourra être réutilisé dans des contextes différents. Les interfaces et le mécanisme d‟interaction dépendent de la complexité et la performance du système entier.

Afin de définir un standard pour un système RVI basé sur le FPGA, plusieurs facteurs importants doivent être considérés :

Les évolutions estimées des circuits FPGA en termes et capacités, performance et des ressources spéciales.

Les matériels extérieurs comme les cartes filles, CAN, CNA, câbles, connecteurs

Les communications possible avec le PC (port parallèle, port série, USB, Ethernet.)

Les outils logiciels : synthétiseurs, outils de programmation des FPGA, les outils de simulation et débogage, des outils Ad Hoc.

Les FPGA à anti-fusibles

Commercialisés à partir de 1990, ce FPGA, programmable une seule fois, est basé sur la technologie des interconnexions à anti-fusibles. Sa structure dispose de cellules élémentaires organisées en rangées et en colonnes. Les lignes d’interconnexions programmables traversent le circuit, horizontalement et verticalement, entre les diverses cellules. La technologie à anti-fusibles permet de réduire considérablement la surface prise par les interconnexions programmables, par rapport aux interconnexions à base de SRAM. La cellule élémentaire diffère d’un fabricant à un autre, mais elle est généralement composée de quelques portes logiques. Le nombre de ces cellules est généralement très important.

Alors que le FPGA SRAM est utilisé pour des prototypes ou des petites séries, le FPGA à anti-fusibles est destiné pour des plus grandes séries, en raison de son coût de fabrication moins élevé. Il est généralement conçu avec des outils de synthèse de type VHDL que nous allons voir dans le chapitre suivant.

LA PROGRAMMATION MATERIELLE

D‟après ce qui précède, nous connaissons déjà la technologie des circuits FPGA et leurs performances en matière d‟instrumentation virtuelle. Maintenant, nous allons présenter les outils et moyens permettant le développement et la réalisation de différentes implémentations sur les systèmes reconfigurables type FPGA. Pour cela, commençons par apprendre la conception sur la base d‟un langage spécifique à des fins de programmation de composants FPGA, puis en se basant sur des outils de conception graphique et textuel convenables aux circuits FPGA que nous avons sur les mains.

Les langages de description matérielle

Généralités

Auparavant pour décrire le fonctionnement d‟un circuit électronique programmable les techniciens et les ingénieurs utilisaient des langages de bas niveau (ABEL, PALASM, ORCAD/PLD) ou plus simplement un outil de saisie de schémas.

Actuellement la densité de fonctions logiques (portes et bascules) intégrée dans les FPGAs est telle (plusieurs milliers de portes voire millions de portes) qu‟il n‟est plus possible d‟utiliser les outils d‟hier pour développer les circuits d‟aujourd‟hui.

Les sociétés de développement et les ingénieurs ont voulu s‟affranchir des contraintes technologiques des circuits. Ils ont donc créé des langages dits de haut niveau à savoir VHDL« Very high speed integrated circuits Hardware Description Langage » et VERILOG. Ces deux langages font abstraction des contraintes de technologies des circuits FPGAs. Ils permettent au code écrit d‟être portable, c‟est à dire qu‟une description écrite pour un circuit peut être facilement utilisée pour un autre circuit. Ces langages dits de haut niveau permettent de matérialiser les structures électroniques d‟un circuit. En effet les instructions écrites dans ces langages se traduisent par une configuration logique de portes et de bascules qui est intégrée à l‟intérieur des circuits FPGAs. Dans ce travail de mémoire, nous nous intéressons seulement à VHDL et aux fonctionnalités de base de celui-ci lors des phases de conception ou synthèse des FPGAs.

VHDL et normalisation

Développé dans les années 80 aux États-Unis, le langage de description VHDL est ensuite devenu une norme IEEE (Institut of Electrical and Electronics Engineers) numéro 1076 en 1987. Révisée en 1993 pour supprimer quelques ambiguïtés et améliorer la portabilité du langage, le langage VHDL est un standard IEEE (IEEE 1076-1993) pour la modélisation, la simulation et la synthèse de systèmes matériels logiques [5]. La norme qui définit la syntaxe et les possibilités offertes par le langage de description VHDL est très ouverte. Il est par exemple possible de spécifier les temps de propagations et de transitions des signaux d’une fonction logique, c’est à dire créer une description VHDL du système que l’on souhaite obtenir en imposant des temps précis de propagation et de transition. Or les outils actuels de synthèses logiques sont incapables de réaliser une fonction avec de telles contraintes. Seuls des modèles théoriques de simulations peuvent être créés en utilisant toutes les possibilités du langage.La situation peut donc se résumer de la façon présentée dans les Figures .2.1 et 2.2.

Relation entre une description VHDL et les circuits logiques programmables comme les circuits FPGAs

L‟implantation d‟une ou de plusieurs descriptions VHDL dans un FPGA va dépendre de l‟affectation que l‟on fera des broches d‟entrées / sorties et des structures de base du circuit logique programmable. Cette affectation peut se faire de plusieurs manières:

L’affectation automatique.

On laisse le synthétiseur propre au fondeur du circuit implanter la structure correspondante à la description VHDL. Les numéros de broches seront choisis de façon automatique.

L’affectation manuelle.

On définit les numéros de broches dans la description VHDL ou sur un schéma bloc définissant les liaisons entre les différents blocs VHDL ou dans un fichier texte propre au fondeur. Les numéros de broches seront affectés suivant les consignes données.

Utilité du VHDL

Le VHDL est un langage de spécification, de simulation et également de conception. Contrairement à d‟autres langages comme ABEL qui se trouvaient être en premier lieu des langages de conception, VHDL est d‟abord un langage de spécification. La normalisation a d‟abord eu lieu pour la spécification et la simulation (1987) et ensuite pour la synthèse (1993). Cette notion est relativement importante pour comprendre le fonctionnement du langage et son évolution. Grâce à la normalisation, on peut être certain qu‟un système décrit en VHDL standard est lisible quel que soit le fabricant de circuits.

Spécification

Le VHDL est un langage de spécification. C‟est dans ce domaine que la norme est actuellement la mieux établie. Il est tout à fait possible de décrire un circuit en un VHDL standard pour qu‟il soit lisible de tous. Certains fabricants (de circuits ou de CAO : Conception Assistée par Ordinateur) adaptent ce langage pour donner à l‟utilisateur quelques facilités supplémentaires, au détriment de la portabilité du code [6]. Heureusement, il y a une nette tendance de la part des fabricants à revoir leurs positions et à uniformiser le VHDL. Il est donc probable que l‟on s‟approche d‟un vrai standard VHDL et non plus d‟un standard théorique. Il y aura toujours des ajouts de la part des fabricants, mais il ne s‟agira plus d‟une modification du langage, mais de macros offertes à l‟utilisateur pour optimiser le code VHDL en fonction du circuit cible (en vue de la synthèse).

Simulation

Le VHDL est également un langage de simulation. Pour ce faire, la notion de temps sous différentes formes y a été introduite. Des modules, destinés uniquement à la simulation, peuvent ainsi être créés et utilisés pour valider un fonctionnement logique ou temporel du code VHDL. La possibilité de simuler avec des programmes VHDL devrait considérablement faciliter l‟écriture de tests avant la programmation du circuit et éviter ainsi de nombreux essais sur un prototype qui sont beaucoup plus coûteux et dont les erreurs sont plus difficiles à trouver. Bien que la simulation offre de grandes facilités de test, il est toujours nécessaire de concevoir les circuits en vue des tests de fabrication, c‟est-à-dire en permettant l‟accès à certains signaux internes.

Conception

Le VHDL permet la conception de circuits avec une grande quantité de portes. C‟est cette utilité de VHDL qui nous concerne le plus dans ce projet de mémoire. Il est à noter que les circuits FPGA actuels comprennent entre 500 et 1 000 000 portes et que ce nombre augmente très rapidement, comme dans notre conception d‟instruments virtuels, nous utilisons un circuit FPGA d‟Actel comprenant 1 500 000 portes. L‟avantage d‟un langage tel que celui-ci par rapport aux langages précédents de conception matérielle est comparable à l‟avantage d‟un langage informatique de haut niveau (C, Pascal, Ada) vis-à-vis de l‟assembleur. Ce qui veut dire que malgré l‟évolution fulgurante de la taille des circuits, la longueur du code VHDL n‟a pas suivi la même courbe. Le VHDL bien que facilement accessible dans ses bases, peut devenir extrêmement compliqué s‟il s‟agit d‟optimiser le code pour une architecture de circuit. C‟est pour cette raison que de plus en plus de fabricants offrent des macros, gratuites pour les fonctions sans grandes difficultés et payantes pour les autres. Donc avant de concevoir un processeur RISC (Reduced Instruction Set Computer), une ALU (Arithmetic Logic Unit), une interface PCI (Peripheral Component Interconnect) ou d‟autres éléments de cette complexité, il peut être judicieux de choisir un circuit cible en fonction des besoins et d‟acheter la macro offerte par le constructeur. Dans notre cas d‟instrumentation virtuelle, nous avons choisi le circuit FPGA d‟Actel (déjà mentionné précédemment) mais nous n‟avons pas acheté chez eux les macros qui nous conviennent puisqu‟il y a aussi des versions gratuites destinées aux recherches pédagogiques. Il est donc bien évident qu‟il faudra évaluer les besoins (performance du code nécessaire, quantité d‟instruments à produire) et le coût d‟une telle macro.

Méthodologie de développement matériel

Analyse des besoins

Lorsqu‟on commence un développement matériel, il est utile de se demander de quelle manière celui-ci sera réalisé. Faut-il attaquer les problèmes les uns après les autres ou en parallèle ? Quel type de description faut-il utiliser pour telle ou telle partie du circuit à concevoir ? Et il y en a d‟autres encore. Ce chapitre tente d‟y répondre par une méthode de travail. Celle-ci minimisera les erreurs de développement en VHDL et facilitera la compréhension du code VHDL écrit par quelqu‟un d‟autre (pour autant que ce quelqu‟un ait suivi cette méthode).

Ensuite, la prochaine étape de développement matériel sera la spécification et la synthèse. Mais avant d‟entamer ce paragraphe, l‟organigramme représenté par la Figure 2.3 nous donne trois informations nécessaires à notre phase de conception matérielle : les diverses étapes du projet, puis l‟ordre qu‟on va les traiter et enfin le type de structure VHDL qu‟il faut employer pour les différentes parties du développement.

Spécification et synthèse

Deux étapes particulières apparaissent dans la Figure 2.3, celle de la spécification et de la synthèse. En VHDL, il convient de bien distinguer ces deux étapes, car le code écrit pour l‟une ou l‟autre n‟est pour l‟instant pas complètement identique.

La spécification est la partie d‟un développement qui consiste à valider par la simulation ce qui a été demandé par le mandataire. Elle permet de corriger un cahier des charges incorrect ou de compléter celui-ci. La spécification en VHDL permet de créer une sorte de maquette qui a, vu de l‟extérieur, le comportement du système désiré.

La synthèse permet de gérer automatiquement à partir du code VHDL un schéma de câblage permettant la programmation du circuit cible. La description du code pour une synthèse est, en théorie, indépendante de l‟architecture du circuit. En pratique, le style utilisé aura une influence sur le résultat de la synthèse, influence liée au type de circuit et au synthétiseur utilisé.

II.2.3. Interface VHDL et codage

Avant d‟écrire un programme en VHDL, il faut définir l‟interface entre l‟intérieur du circuit et le monde extérieur comme présenté à la Figure 2.4. Il ne suffit pas d‟avoir un programme qui décrit un certain comportement. Ce comportement réagit selon des entrées et agit sur des sorties (ou des entrées-sorties) et tous ces ports seront connectés à une carte externe au circuit. Toutes ces connexions correspondent à cette interface.

Les outils de développement matériel

Les principaux outils sur le marché

Avant de savoir les outils que nous avons utilisés dans cette phase de développement matériel de la conception d‟instruments virtuels, décrivons successivement les principaux outils présents sur le marché. Notons que les noms en caractères gras qui suivent représentent des noms d‟entreprises de semi-conducteurs les plus connus à travers le monde, et que les noms en italique correspondent à leurs propres outils de développement :

Actel:Libero (environnement de conception intégré), SmartTime (analyse des délais), SmartPower (analyse de la consommation), SmartGen,.

Altera:Quartus II (environnement de conception intégré), SOPC Builder (développement de systèmes), DSP Builder, TimeQuest (analyse des délais), PowerPlay (analyse de la consommation),

Lattice:ispLever (environnement de conception intégré), ispLeverDSP,

Mentor Graphics:Precision RTL (synthèse logique), Precision Physical (synthèse physique), ModelSim (simulation numérique), CatapultC (synthèse de haut niveau),.

Synplicity:Synplify Pro (synthèse logique), Synplify Premier (synthèse physique), Synplify DSP, Certify (prototypage des circuits spécifiques), Identify (instrumentation embarquée et débogage),

Xilinx:ISE (environnement de conception intégré), System Generator for DSP et AccelDSP, ChipScope Pro (débogage embarqué), PlanHead,

En effet, nous remarquons que chaque entreprise de semi-conducteurs a ses propres outils. Pourtant, la plupart de ces entreprises se coopèrent afin de répondre aux besoins de leurs clients.

L’environnement intégré de conception Actel Libero

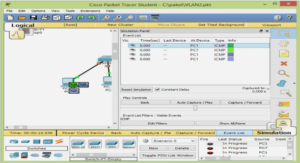

Actel est une entreprise américaine de semi-conducteurs, elle fait partie des plus grandes entreprises spécialisées dans le développement et la commercialisation de composants logiques programmables, et des services associés tels que les logiciels de CAO électroniques, les blocs de propriété intellectuelle réutilisables ou « IP Cores » (Intellectual Property Cores) [6]. Le logiciel Libero IDE (Integrated Design Environment) est un logiciel complet et puissant en matière de développement des FPGAs, développée par Actel. Dans ce projet de mémoire, nous avons utilisés l‟environnement intégré de développement «Actel

Libero IDE» fonctionnant sous Windows et une carte FPGA produite par cette société dont la description sera détaillée ci-après. En fait, Libero IDE nous permet de programmer ce FPGA, en d‟autres termes de concevoir, simuler, synthétiser, placer-router et valider facilement des blocs décrits en VHDL (ou autre langage) dans un seul environnement.

|

Table des matières

CHAPITRE I. GENERALITES SUR L’INSTRUMENTATION VIRTUELLE

I.1. Introduction à l‟instrumentation virtuelle

I.1.1. De l‟instrumentation à l‟instrumentation virtuelle

I.1.2. Notion sur les instruments virtuels

I.1.3. Analyse des coûts

I.2. Conception d‟un instrument virtuel

I.2.1. Architecture d‟un système Instrument Virtuel Reconfigurable

I.2.2. L‟instrument reconfigurable

I.3. Introduction aux circuits FPGA

I.4. Le logiciel

CHAPITRE II. LA PROGRAMMATION MATERIELLE

II.1. Les langages de description matérielle

II.1.1. Généralités

II.1.2. VHDL et normalisation

II.1.3. Relation entre une description VHDL et les circuits logiques programmables comme les circuits FPGAs

II.1.4. Utilité du VHDL

II.2. Méthodologie de développement matériel

II.2.1. Analyse des besoins

II.2.2. Spécification et synthèse

II.2.3. Interface VHDL et codage

II.2.4. Simulation

II.3. Les outils de développement matériel

II.3.1. Les principaux outils sur le marché

II.3.2. L‟environnement intégré de conception Actel Libero

II.3.3. La suite Soft Console IDE

II.4. Les circuits utilisés

II.4.1. La carte d‟acquisition d‟Actel « Fusion Embedded Development Kit »

II.4.2. Caractéristiques de Fusion Embedded Development Kit

II.4.3. Le low-cost programming stick ( LCPS) »

CHAPITRE III. LA PROGRAMMATION LOGICIELLE

III.1. Les langages et compilateurs

III.1.1. Le langage C++

III.1.2. Visual C++ et MFC

III.2. Méthodologie de développement logiciel

III.2.1. L‟analyse des besoin

III.2.2. Spécification et conception

III.2.3. Codage

III.2.4. Test du logiciel

III.2.5. Maintenance

III.3. Interfaçage matériel de l‟Instrument Reconfigurable avec le PC

III.3.1. Le port USB

III.3.2. Principe de communication avec le port USB

III.4. Les contraintes du logiciel

CHAPITRE IV. REALISATION D’UN OSCILLOSCOPE VIRTUEL

IV.1. Généralités

IV.2. Conception et développement de la partie matérielle

IV.2.1. Synoptique du système à concevoir

IV.2.2. Le flot de conception de l‟oscilloscope (Hardware design flow)

IV.2.3. Conception de la carte fille pour l‟oscilloscope

IV.3. Conception et développement de la partie logicielle

IV.3.1. Synoptique du système à concevoir

IV.3.2. Présentation de l‟interface utilisateur de l‟oscilloscope virtuel

CHAPITRE V. REALISATION D’UN GENERATEUR DE FORME D’ONDE

V.1. Généralité

V.2. Conception et développement de la partie matérielle

V.2.1. Synoptique du système à concevoir

V.2.2. Le flot de conception du générateur de forme d‟onde (Hardware design flow)

V.2.3. Conception de la carte Fille pour le générateur de forme d‟onde

V.3. Conception et développement de l‟interface utilisateur de la partie logicielle

V.3.1. Synoptique du système à concevoir

V.3.2. Présentation de l‟interface utilisateur du générateur de forme d‟onde

CONCLUSION

ANNEXE I: PRESENTATION DU FUSION EMBEDDED DEVELOPMENT KIT

ANNEXE II : STRUCTURE GENERALE D’UN PROGRAMME VHDL

ANNEXE III : FLOT DE CONCEPTION MATERIELLE

A.3.1. Flot de conception de l’oscilloscope

A.3.2. Flot de conception du générateur de forme d’onde

A.3.3. Présentation du programme exécutable via l’outil SoftConsole IDE

ANNEXE IV : ALGORITHME GENERAL DE LA PARTIE LOGICIELLE

A.4.1. Algorithme de l’oscilloscope

A.4.2. Algorithme pour le générateur de forme d’onde

REFERENCES

Télécharger le rapport complet