Les différents types de formats de données

Le choix d’une représentation binaire relève d’une problématique qui concerne toute plateforme numérique actuelle. Faire un choix d’une représentation ou d’une arithmétique représente une étape primordiale dans le développement d’une application numérique. Les arithmétiques virgule fixe et virgule flottante sont généralement utilisées dans un but de stockage ou de calcul. En général, les algorithmes de traitement numérique de signal demandent des capacités de calcul intensif. Par conséquent, le choix du bon format de représentation des nombres joue un rôle crucial pour une implémentation efficace de n’importe quel algorithme de traitement numérique de signal. Dans le calcul numérique, le système de numération spécifie la méthode selon laquelle les nombres sont représentés comme étant une séquence de chiffres binaires et il spécifie également les règles pour effectuer les opérations arithmétiques (ex. addition, multiplication etc.) entre ces nombres. Dans la plupart du temps, les calculs scientifiques donnent seulement une approximation de la valeur exacte qui serait obtenue avec une précision infinie. Ceci est une conséquence du nombre limité de bits utilisés dans le système de numération. Quel que soit l’arithmétique virgule fixe ou l’arithmétique virgule flottante utilisée, seulement un nombre fini de bits est utilisé pour la représentation des nombres réels. La précision limitée des standards de codage peut être évaluée selon deux perspectives différentes. La première concerne la précision des calculs déterminée par l’étape de quantification du système de numération (la distance entre deux nombres). Le second aspect est relatif à la variation de la dynamique maximale permise par la représentation. Cette variation de la dynamique d’un système de numération est donnée par l’ensemble des valeurs possibles qui peuvent être représentées

Notation Signe – Valeur Absolue (SVA)

La notation en numération simple d’un nombre signé correspond à la représentation de la valeur absolue de ce nombre en numération simple de position en ajoutant un symbole spécifiant le signe du nombre à représenter. L’inconvénient de cette représentation se manifeste par les opérations mathématiques effectuées sur des nombres respectant cette notation. En effet, à titre d’exemple, l’addition de deux nombres nécessite l’utilisation de deux algorithmes : un algorithme d’addition si les deux nombres possèdent le même signe et un algorithme de soustraction dans le cas contraire.

Comparaison de point de vue implémentation matérielle et logicielle

Chaque implémentation logicielle ou matérielle possède ses propres contraintes qui déterminent le choix de l’arithmétique la plus adaptée. Dans le cas d’une implémentation logicielle, les longueurs du mot de code sont fixées ou bien alors elles possèdent un nombre limité de représentations dans le format virgule flottante ou virgule fixe. Cependant, le format de la représentation en virgule fixe est flexible dans la mesure où le point binaire n’est pas fixe. Dans les plateformes logicielles typiques, les tailles d’un mot de code en arithmétique virgule fixe sont généralement d’un octet (8bits), moitié d’un mot (16 bits), un mot (32 bits) et aussi longue que mot double (64 bits). Les nombres en virgule flottante sont habituellement selon deux formats : soit la précision simple ou la précision double. De plus, il convient de préciser que les plateformes processeurs supportent les opérations des vecteurs de données SIMD (Single Instruction Multiple Data) [35]. De telles instructions fonctionnent sur un ensemble de données de même taille et de même type rassemblées en un bloc de données, d’une taille fixe, appelé vecteur. Il est alors possible de configurer le chemin de données selon une taille normalisée (le nombre de bits est généralement multiple de quatre ou huit) afin de contrôler plus précisément les longueurs des mots de code en arithmétique virgule fixe. L’implémentation matérielle ouvre également des horizons pour des unités en virgule flottante personnalisées [25] [27]. Dans [40], les spécifications des opérateurs en virgule flottante sont décrites en utilisant une bibliothèque C++ paramétrée d’opérateurs en virgule flottante. Il en résulte une génération automatique des implémentations optimales des opérateurs en virgule flottante dans le matériel de telle sorte que le temps de calcul est suffisamment petit pour atteindre la fréquence désirée de l’opération. L’impact du nombre de bits accordés à l’opérateur en virgule flottante sur le niveau de la dynamique et la précision de l’opération n’est pas aussi simple que dans le cas de système des nombres en virgule fixe. En définitive, il s’avère difficile de faire un choix entre le format virgule fixe et le format virgule flottante sans explorer explicitement toutes les opérations.

Simulation virgule fixe

Nous présentons dans cette partie différentes méthodes statistiques fondées sur un outil de simulation en virgule fixe. Cet outil émule les mécanismes de la représentation virgule fixe en termes de dépassement et de quantification sur un poste de travail utilisant l’arithmétique virgule flottante. Pour effectuer l’émulation de ces mécanismes, les méthodes existantes utilisent les propriétés de la surcharge des opérateurs. Cette dernière technique, présentée par Kim [61], permet une spécification virgule fixe à travers le type gFix [59] [60]. Lors d’une assignation, une conversion du format entre la donnée de droite et celle de gauche est réalisée en suivant les règles spécifiées au sein d’attributs. La spécification en entrée du simulateur correspond au programme source écrit en C++, où le type des données en virgule flottante est remplacé par le type gFix. Dans ce cas, la surcharge des opérateurs conduit à un temps d’exécution de l’algorithme plus long qu’une simulation virgule flottante. Pour avoir une idée sur les temps d’exécution, nous pouvons citer l’exemple du temps de simulation de la librairie SystemC qui est en moyenne 540 fois supérieur à celui obtenu en virgule flottante [33]. Dans [61], un nouveau type pFix a été proposé pour réduire le temps de simulation de la méthode précédente. Cette méthode est basée sur l’optimisation de l’utilisation des chemins des données de l’unité de calculs en virgule flottante. Par conséquent, ce type enregistre les données en virgule fixe en utilisant la mantisse des données en virgule flottante ce qui réduit le temps de simulation. Dans le cas d’un filtre IIR d’ordre 4, le temps de simulation est supérieur de 7,5 fois à celui de la virgule flottante. Une des limitations du type pfix réside dans la taille maximale de la mantisse dont le nombre de bits accordés est 53. Dans [18], une technique similaire est utilisée pour l’accélération des bibliothèques en virgule fixe du SystemC. Pour réduire le temps de simulation, une autre technique, proposée par Coster [34], conduit à un codage efficace des données de l’algorithme en exploitant tous les types d’entiers disponibles sur la machine. La performance du type de données en virgule fixe peut être également accélérée en utilisant une architecture convenable du processeur (comme dans le cas du DSP). Ainsi, les techniques proposées dans [64][48], conçues initialement pour la génération automatique du code en virgule fixe, peuvent être réutilisées pour accélérer l’exécution en ciblant une affectation du format de données en virgule fixe sur les plateformes DSP. Dans cet esprit, l’outil System Generator de Xilinx [94] fournit un ensemble de modules personnalisés en virgule fixe pouvant être utilisés sous Matlab-Simulink, et permettant un prototypage rapide sur le matériel d’algorithmes de traitement du signal.

|

Table des matières

Introduction

Contexte de l’étude

Problématique de la thèse

Contributions

Organisation de la thèse

1 Arithmétique virgule fixe

1.1 Les différents types de formats de données

1.1.1 Représentation des nombres entiers

1.1.2 Le format virgule fixe

1.1.3 Le format virgule flottante

1.1.4 Comparaison arithmétiques virgule flottante et virgule fixe

1.2 Modélisation du bruit de quantification

1.2.1 Processus de quantification

1.2.2 Signal à amplitude continue

1.2.3 Signal à amplitude discrète

1.2.4 Conclusion

1.3 Évaluation de la précision

1.3.1 Les métriques de précision

1.3.2 Les méthodes d’évaluation de la précision par simulation

1.3.3 Les approches analytiques de l’évaluation de la précision

1.3.4 Autres effets de la quantification

1.3.5 Bilan des deux approches

1.3.6 Les approches hybrides

1.4 Conclusion

2 Évaluation analytique de la précision des algorithmes de décodage sphérique

2.1 Les opérateurs lisses et non lisses

2.1.1 Introduction

2.1.2 Les opérateurs lisses et non-lisses

2.1.3 La quantification d’un opérateur non lisse

2.1.4 Identification d’un opérateur non lisse

2.2 Modèle analytique pour l’opérateur de décision

2.2.1 Modélisation de l’opérateur de décision

2.2.2 La réponse à la perturbation

2.2.3 La probabilité d’erreur de décision

2.3 Cascade d’opérateurs de décision

2.3.1 Propagation de l’erreur de quantification

2.3.2 Détermination analytique de la probabilité d’erreur en sortie de la cascade

2.3.3 Analyse de la complexité du modèle analytique

2.4 Application du modèle à l’algorithme SSFE

2.4.1 Modèle du système MIMO

2.4.2 Présentation de l’algorithme

2.4.3 Application du modèle analytique proposé

2.4.4 Première approche

2.5 Conclusion

3 Évaluation de la précision de l’itération d’opérateur de décision

3.1 Problématique

3.1.1 Caractéristiques de la propagation du bruit

3.2 Modèle analytique proposé

3.2.1 Approche basée sur la résolution d’un système non linéaire à l’aide de l’algorithme de Newton-Raphson

3.2.2 Borne supérieure de la probabilité d’erreur

3.3 Évaluation de la précision de l’égaliseur à retour de décision

3.3.1 Présentation de l’algorithme DFE

3.3.2 Résultat pour le cas non adaptatif

3.3.3 Solution proposée pour le cas adaptatif

3.4 Optimisation du format virgule fixe pour l’implémentation matérielle

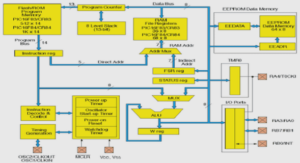

3.4.1 Présentation de l’architecture

3.4.2 Implémentation sur FPGA

3.4.3 Les contraintes du choix du format de représentation

3.5 Conclusion

4 Évaluation de la précision du turbo décodage

4.1 L’optimisation de la largeur des données en virgule fixe

4.1.1 Variantes du problème

4.1.2 Variable d’optimisation

4.1.3 Solution au problème d’optimisation de la longueur du mot de code

4.2 Optimisation du turbo décodage

4.2.1 Présentation de l’algorithme

4.2.2 Modélisation et design en virgule fixe

4.2.3 Réduction de la taille de mémoire

4.2.4 Performance du turbo décodeur

4.3 Optimisation du décodage LDPC

4.3.1 Modélisation et design en virgule fixe d’un décodeur LDPC

4.3.2 Réduction de la taille de mémoire

4.3.3 Performance en virgule fixe du décodeur LDPC

4.4 Conclusion

Conclusion et Perspectives

Perspectives

A Quantification uniforme et quantification double

A.1 Quantification uniforme

A.1.1 Quantification dans le domaine de la fonction caractéristique

A.2 La quantification double

B La méthode de Newton-Raphson pour la résolution des systèmes non linéaires

B.1 Les systèmes non linéaires

![]() Télécharger le rapport complet

Télécharger le rapport complet