PARAMÉTRISATION D’UN PROGRAMME À DOUBLE BOUCLES IMBRIQUÉES

Revue des connaissances

En 1993, Hernandez et al. [9] ainsi que Callaway et Swartzlander [4], sont les premiers à proposer des modèles d’estimation de la consommation de puissance des puces VLSI au niveau des circuits et des portes logiques. Pour la première fois, en 1995, Tiwari et al. [25] ainsi que Mike et al. [17] proposent des modèles basés sur les instructions utilisées d’un programme. En 1996, Wang et Roy [30] se concentrent sur la consommation maximale instantanée de puissance dissipée dans les puces VLSI. Leurs travaux guideront la conception future des circuits VLSI. Durant la même période, Ishiara et Yasuura [11] [12], évalueront les diverses méthodes d’estimation de consommation de puissance proposées jusqu’à ce jour.

L’année 1998 voit Katkoori et Vemuri [16] prendre en considération l’analyse de consommation de puissance dans la conception de circuit VLSI. Wang et Roy [31] ainsi que Russell et Jacome [21] proposent des logiciels de tests automatisés complétant la simulation afin d’en déterminer la consommation de puissance. En 1998, l’apparition d’algorithmes de conception de circuits VLSI touchant la réduction de consommation d’énergie nous est présentée par Nguyen, Chatterjee et Roy [18]. En 1999, Chen, Irwin et Bajwa [5] nous présentent de nouvelles techniques d’estimation de consommation de puissance basées sur la non connaissance des structures internes des circuits logiques. Les années 2000 et 2001 voient les diverses techniques d’estimation de consommation de puissance atteindre un niveau avancé de développement ; que ce soit avec les processeurs superscalaires, Conte et al. [6], au niveau de l’ensemble de circuits VLSI, Hsiao, Rudnick et Patel [10] ou encore au niveau des réseaux logiques avec Theodoridis et al. [24].

En 2001, Ascia et al. [2] étudieront l’impact du logiciel sur la consommation de puissance d’un circuit. Rita, Irwin et Bajwa [20] amélioreront les méthodes d’estimation de la consommation énergétique avant et pendant la conception des circuits. L’année 2002 verra Guitton-Ouhamou, Belleudy et Auguin [8] développer une bibliothèque de l’impact énergétique des différentes instructions en langage d’assembleur d’un processeur. C’est à Tran, Kim et Kim [28] en 2005 et Shin et Lee [22] en 2006 que l’on doit l’apparition de méthodes avancées d’estimation énergétique qui divise le processeur en sections distinctes dont chacune est étudiée séparément et dont la somme énergétique donne la consommation totale du processeur. Les années 2007 à 2010 verront le développement de plusieurs systèmes d’estimation énergétique prenant en compte le système complet avec son logiciel, sans toutefois connaître la composition intrinsèque des circuits. Plusieurs chercheurs participent à cette évolution. Kang et al. [15] en 2007, Jevtic et Carreras [13] ainsi que Cai et al. [3] en 2010 et Gonzalez et al. [7] en 2011.

De plus, les années 2010 et 2011 verront apparaître des méthodologies complètes d’estimation de consommation de puissance directement orientées vers la conception complète des processeurs ou des circuits VLSI. C’est à Jevtic et Carreras [14] ainsi que Rethinagiri et al. [19] que l’on doit la création de telles méthodologies de conception. En parallèle avec tous ces travaux sur les processeurs synchrones essayant d’éliminer les problèmes de distribution d’horloge, de variation de paramètres, de consommation de puissance et de complexité de conception, quelques groupes de chercheurs se sont penchés sur la conception des processeurs asynchrones visant à éliminer ces problèmes. C’est depuis le milieu des années 80 que les microprocesseurs asynchrones ont vu le jour. Rappelons qu’un processeur asynchrone n’utilise pas d’horloge centrale pour exécuter ses instructions.

Il utilise plutôt un protocole simple de signaux indiquant l’achèvement des instructions. Les méthodologies de conception de ces processeurs ont été abondamment documentées. Pensons aux travaux riches en innovations et abondamment cités de Bainbridge et al. [33] utilisant une approche asynchrone basée sur les délais critiques afin de satisfaire les longs chemins d’interconnections. Woods et al. [38] réalisent un microprocesseur asynchrone utilisant une approche basée sur le micro-pipeline de Sutherland [39]. Ces travaux sont repris par Furber et al. [34] et [35] qui proposent dans un premier temps un micro-pipeline à quatre phases visant à réduire les coûts fixes et dans un deuxième temps, ils conçoivent une puce comprenant un contrôleur asynchrone de 32 bits complet très efficace. Martin et al. [36] présente le design asynchrone d’un clone du processeur synchrone MIPS R3000. Stevens et al. [37] font une étude décrivant les avantages et les pièges des designs asynchrones appliqués aux architectures de pointe des microprocesseurs. . Bien que tous ces travaux contournent d’une certaine manière les problèmes de consommation de puissance des processeurs synchrones, aucune technique de mesure de cette même consommation énergétique des instructions de processeurs asynchrones n’a été développée à ce jour. Aucun des efforts de recherche mentionné jusqu’ici n’a porté sur l’étude de la consommation énergétique des processeurs asynchrones. Les présents travaux proposent de faire la caractérisation en puissance et en énergie, des instructions d’un processeur multicoeur asynchrone.

CONCLUSION

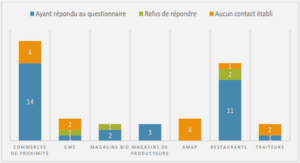

Le premier chapitre consiste en une revue des connaissances du sujet traité et positionne les présents travaux. Le second chapitre porte sur l’environnement de test utilisé dans le cadre de ce projet, y compris la carte VEB sur laquelle les travaux sont effectués. Au troisième chapitre, un programme simple à 2 boucles imbriquées a été paramétré. Ceci impliquait la paramétrisation de la boucle externe, de la boucle interne et des instructions contenu dans la boucle interne du programme. Dans le cas de la paramétrisation de Nmac, il a été démontré que Texéc est linéaire pour Nmac > 5. Dans le cas des paramétrisations de Bint et Bext, il a été démontré que Texéc est entièrement linéaire. Ceci suggère que les coûts fixes en termes de temps d’exécution deviennent alors négligeables. Au chapitre 4, la modélisation avec des équations mathématiques de la paramétrisation de notre programme à 2 boucles imbriquées est présentée. Cette modélisation nous amène à calculer une vitesse d’exécution distincte ainsi qu’un temps d’exécution propre à chaque instruction pour un processeur asynchrone.

La précision de notre modèle a été établie en comparant le temps d’exécution mesuré au temps d’exécution théorique calculé. Dans chacun des cas, une excellente précision avec un grand nombre d’itérations ou d’instructions a été obtenue. Le cinquième chapitre montre qu’il est possible de produire des fréquences d’exécution d’instructions et de boucles en exécutant un programme en boucle. La période de ces fréquences d’exécution représente le temps d’exécution propre de ces instructions pour un processeur asynchrone. L’hypothèse selon laquelle un programme fonctionnant en boucle provoque une demande de courant à la source d’alimentation à chaque fois qu’une instruction est exécutée et que cette répétition va se traduire par l’apparition, dans le spectre fréquentiel de la consommation de courant, de la fréquence d’exécution de l’instruction et des boucles internes et externes est donc validée. Concernant la boucle externe de notre programme, notre modèle indique une fréquence spécifique d’exécution alors que l’expérience reproduit sa deuxième harmonique. À ce jour, nous n’avons pas d’explication à ce phénomène. Plusieurs hypothèses sont envisagées, dont l’influence des mécanismes internes de transfert de données dans le contexte de l’insuffisance de ressources internes des coeurs mais la validation de celles-ci dépasse le cadre de ce travail.

Au chapitre 6, le temps propre d’exécution des instructions typiques servant à former un programme pour filtre FIR est calculé. La consommation moyenne en puissance de chaque coeur pour chaque type d’instructions est estimée. La consommation énergétique moyenne de chaque instruction est également estimée. Du temps d’exécution des instructions, il est possible de calculer le temps d’exécution théorique total de chaque programme. Enfin, l’erreur relative entre le temps calculé d’exécution des programmes et leur temps réel mesuré a été montrée. Ces erreurs relatives sont faibles pour toutes les instructions en assembleur, ce qui confirme la validité du modèle mathématique du chapitre 4. Le chapitre 7 montre l’application de notre modèle à un filtre réel de type « FIR ». L’énergie théorique totale consommée par le programme est de 1.97E-02 Joules, alors que l’énergie totale mesurée par le programme est de 2.18E-02 Joules. Une erreur relative de 9.6% les sépare. D’autre part, le temps d’exécution théorique total du programme est de 10.5 sec alors que le temps d’exécution total mesuré du programme de 11.2 sec. Une erreur relative de 6.1% les sépare.

|

Table des matières

INTRODUCTION

CHAPITRE 1 L’ÉTAT DE L’ART

1.1 Revue des connaissances

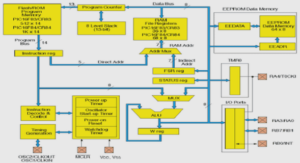

CHAPITRE 2 ENVIRONNEMENT DE TEST

2.1 Introduction

2.2 Carte Vocallo

2.3 Amplificateur

2.4 Environnement physique de test

2.5 Environnement de développement logiciel

2.6 Conclusion

CHAPITRE 3 PARAMÉTRISATION D’UN PROGRAMME À DOUBLE BOUCLES IMBRIQUÉES

3.1 Introduction

3.2 Méthodologie

3.3 Paramétrisation

3.3.1 Paramétrisation des instructions

3.3.2 Paramétrisation de la boucle interne

3.3.3 Paramétrisation de la boucle externe

3.4 Conclusion

CHAPITRE 4 MODÉLISATION DU TEMPS D’EXÉCUTION DES INSTRUCTIONS

4.1 Introduction

4.2 Méthodologie

4.3 Équations mathématiques de modélisation

4.4 Application des équations aux données

4.5 Conclusion

CHAPITRE 5 IDENTIFICATION ET ESTIMATION DES FRÉQUENCES D’EXÉCUTION DES INSTRUCTIONS

5.1 Introduction

5.2 Méthodologie

5.3 Identification et estimation des fréquences d’exécution de l’instruction « ADD » pour un seul coeur

5.3.1 Identification et estimation de la fréquence d’exécution de l’instruction « ADD »

5.3.2 Identification et estimation de la fréquence d’exécution de la boucle interne

5.3.3 Identification et estimation de la fréquence d’exécution de la boucle externe

5.4 Identification et estimation des fréquences d’exécution de l’instruction « ADD » pour l’ensemble des coeurs

5.5 Conclusion

CHAPITRE 6 CARACTÉRISATION DES INSTRUCTIONS D’UN FILTRE « FIR »

6.1 Introduction

6.2 Méthodologie

6.3 Caractéristiques fréquentielles

6.4 Caractéristiques de puissance

6.5 Caractéristiques énergétiques

6.6 Caractéristiques temporelles

6.7 Conclusion

CHAPITRE 7 CARACTÉRISATION D’UN FILTRE « FIR »

7.1 Introduction

7.2 Méthodologie

7.3 Caractéristiques énergétiques théoriques

7.4 Caractéristiques énergétiques pratiques

7.5 Conclusion

CHAPITRE 8 INTERMODULATION DES COEURS

8.1 Introduction

8.2 Méthodologie

8.3 Présentation globale du spectre de fréquences d’intermodulation

8.4 Présentation détaillée du spectre de fréquences d’intermodulation

8.4.1 Fréquences d’intermodulation des coeurs

8.4.2 Fréquences d’intermodulation d’enveloppe des « ALU »

8.4.3 Spectre des fréquences de 8 @ 13 MHz

8.4.4 Spectre des fréquences de 60 @ 100 MHz

8.4.5 Fréquence isolée de 150 MHz

8.4.6 Fréquences isolées 200 MHz

8.4.7 Spectre des fréquences d’enveloppes des « ALU »

8.4.8 Spectre de fréquences des coeurs

8.4.9 Spectre de fréquences 5ième harmonique d’enveloppe des « ALU »

8.4.10 Spectre de fréquences 6ième harmonique d’enveloppe des « ALU »

8.5 Vitesse d’exécution des coeurs

8.6 Conclusion

CONCLUSION

RECOMMANDATIONS

ANNEXE I EXEMPLE DE PROGRAMME UTILISÉ POUR CARACTÉRISER LES INSTRUCTIONS

ANNEXE II EXEMPLE DE PROGRAMME UTILISÉ POUR CARACTÉRISER UN FILTRE FIR

ANNEXE III PLAN DE L’AMPLIFICATEUR

LISTE DE RÉFÉRENCES BIBLIOGRAPHIQUES

![]() Télécharger le rapport complet

Télécharger le rapport complet