Télécharger le fichier pdf d’un mémoire de fin d’études

Alimentation du circuit de commande rapprochée

L’alimentation en énergie d’un driver de grille peut être réalisée par un convertisseur isolé faible puissance ou un circuit bootstrap pour les applications low-cost/basse tension [16]. Quelques études ont été menées sur l’alimentation isolée par voie optique ou par prélèvement sur la tension de bus dans le cadre de l’application driver. Des détails sont fournis à la section III.C.1. D’une part, les composants MOSFET SiC pouvant fonctionner à fréquence plus élevée, l’alimentation en énergie des drivers doit permettre d’acheminer plus d’énergie que leurs équivalents IGBT (quelques Watts supplémentaires). D’autre part, la problématique des courants de mode commun est beaucoup plus contraignante de par la rapidité de commutation des composants SiC, une vigilance particulière doit donc être accordée aux capacités parasites introduites par les éléments nécessaires à l’alimentation.

Dans les cartes driver, le circuit secondaire est la plupart du temps alimenté en énergie depuis le circuit primaire par l’intermédiaire d’un convertisseur DC-DC isolé. Cette structure exploite dans tous les cas un transformateur, la plupart du temps associé à un pont de diode (faible puissance requise). Une association de type push-pull non-régulée permet un fonctionnement stable en boucle ouverte de l’alimentation. En effet, une régulation de la tension de sortie nécessite un élément d’isolation additionnel (ex : optocoupleur), ce qui n’est pas avantageux dans le cas des circuits drivers. Deux exemples de circuit d’alimentation sont donnés à la figure I-26.

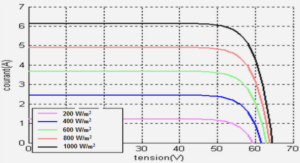

La consommation en énergie du circuit secondaire est fortement tributaire de la fréquence de commutation du composant de puissance et l’énergie nécessaire à la charge de la grille. En effet, l’étage de sortie permet d’injecter des courants de grille impulsionnels importants sur les phases transitoires afin de permettre une commutation rapide du transistor de puissance. Les courants impulsionnels étant fournis par des capacités de découplage, l’étage de sortie présente cependant une consommation relativement faible en régime statique (< 5W). Dans le circuit driver, on peut donc qualifier le circuit d’alimentation de faible puissance, ce qui permet quelques souplesses architecturelles car le rendement n’est pas un facteur limitant en regard des niveaux de puissance mis en jeu dans le composant de puissance adressé. Les structures présentées à la figure I-26 sont très largement utilisées dans les circuits drivers malgré l’aspect non-conventionnel de ces convertisseurs d’énergie.

Dans notre notation, la borne COM (VCOM = 0V) indique toujours le potentiel de référence des circuits logiques. Vp et Vn désignent respectivement une tension d’alimentation positive et négative, VS désignera toujours le potentiel de source du transistor de puissance (cas du MOSFET).

La tension de sortie de l’alimentation isolée d’un driver correspond à l’excursion maximale en tension nécessaire à la commande de grille du composant de puissance (VGS). Le potentiel COM peut être référencé à la source du MOSFET de puissance (COM=VS) ou être choisi au potentiel le plus bas du circuit (COM=Vn). Les caractéristiques de ces deux topologies sont détaillées dans la première partie du tableau 3. Dans les deux cas, la tension de commande VGS est la même (classiquement pour un MOSFET SiC : VGS,on = +20V et VGS,off = -5V VDD = 25V).

D’un fabricant à l’autre, les niveaux de tension d’alimentation des circuits logiques varient également. Les circuits drivers pour composants IGBT sont munis d’alimentation symétriques +15V/-15V et ont donc déjà la possibilité d’alimenter la partie logique en 15V (Vp). La logique 5V est une logique plus rapide avec des temps de propagation plus faibles (portes logiques faiblement capacitives) mais elle nécessite l’implémentation d’un régulateur supplémentaire spécifique aux circuits logiques. Le tableau 3 présente les résultats d’analyse de quelques drivers de grille étudiés par l’équipe de l’IETR.

Protections additionnelles

Détection de court-circuit

Dans tous les drivers présents dans le commerce, la détection de court-circuit par désaturation (DESAT) ou OCP (Over Current Protection) est réalisée par la surveillance de la tension drain-source (VDS) du MOSFET de puissance. En effet, un court-circuit de bras se traduit par une augmentation de la tension VDS des MOSFETs de la cellule de commutation dû à l’impédance de câblage du composant de puissance [29], [30]. La tension de drain peut être bloquée par l’utilisation d’une diode haute tension ou d’une résistance de grande valeur [31]. Des exemples de circuits de détection de court- circuit par diode de désaturation (DESAT) sont donnés à la figure I-31. La diode Dm est passante uniquement si le transistor T est passant car VDS < VL, VL étant la tension d’alimentation des circuits logiques. Lorsqu’une surtension apparaît sur la tension drain-source lors de la phase de conduction, un signal dit « de désaturation » informe le driver d’un dysfonctionnement.

La diode Dm doit être capable de supporter de fortes tensions à ses bornes car elle est exposée à la tension d’alimentation du circuit de puissance (pouvant aller jusqu’à plusieurs kV). Le dimensionnement et l’intégration de cette diode sont très contraignants. En effet, les fortes variations de tension à ses bornes peuvent générer des perturbations CEM ainsi que des risques de claquage. Il est donc nécessaire d’éloigner physiquement cette diode des circuits logiques du circuit secondaire. Généralement, on retrouve cette diode en bout de carte à proximité de la connectique de drain.

PROBLEMATIQUE CIBLEE

Fiabilité des MOSFET SiC

Les performances électriques des MOSFET SiC rendent ces transistors extrêmement prometteurs pour le futur de l’électronique de puissance. Cependant, la faible maturité de cette nouvelle technologie n’est pas sans poser de problèmes de fiabilité. De nombreuses études de robustesse sont donc actuellement menées pour définir les limites de la technologie SiC en termes de durée de vie pour améliorer la fiabilité de ces composants. Ces recherches, réalisées par vieillissement accéléré, doivent également permettre de définir des indicateurs de vieillissement. Au cours de ces essais, les composants sont soumis à des cycles de stress électrique et/ou thermique répétés et leur comportement à la défaillance est analysé.

Les composants à semi-conducteurs de puissance apparaissent comme l’un des facteurs de défaillance les plus critiques au sein d’une chaîne de conversion d’énergie [36]. Une première source de défaillance concerne le packaging et notamment le raccordement de la puce par « wire-bonding ». En effet, la rupture ou le décollement de ces fils de câblage est un problème bien connu des spécialistes de la fiabilité. Heureusement, de plus en plus d’alternatives existent pour fiabiliser la connectique [37]. Toutefois, le wire-bonding est encore très utilisé pour minimiser les coûts de fabrication. D’autre part, la résistance de canal des MOSFET SiC est plus importante que celle des MOSFET Si à géométrie équivalente. Ceci est dû à la faible mobilité des porteurs de charge (µn, µp : tableau 5) à l’interface SiC/SiO2 et au phénomène de piégeage de charges à l’interface des mailles cristallines. Dans le but de minimiser la résistivité du canal, les MOSFET SiC ont donc été conçu avec une épaisseur d’oxyde de grille plus faible que leurs concurrents Silicium (≤ 50nm) [38]. Toutefois, cette caractéristique engendre un effet tunnel plus important à travers l’oxyde de grille [38]–[41] et accroît le phénomène de piégeage de charges à proximité de la grille [42], [43]. Le phénomène de piégeage de charge est sans aucun doute lié à l’introduction de Carbone et à l’interfaçage des mailles cristallines SiC/SiO2. La qualité de l’interface entre l’oxyde de grille et le Carbure de Silicium semble donc être l’un des enjeux majeurs de cette nouvelle technologie. Propriétés physiques de plusieurs matériaux semi-conducteurs utilisés dans les composants de puissance [44]

L’utilisation optimale de composants SiC passe par le développement de circuits de commande adaptés et tenant compte des spécificités de cette nouvelle technologie [45]–[48]. Les premiers drivers pour MOSFET SiC disponibles sur le marché intègrent des fonctions déjà présentes dans les drivers d’IGBT ou MOSFET Si. L’implémentation de la surveillance de la tension drain-source (VDS) est fréquente dans les drivers et permet d’assurer l’intégrité du semi-conducteur dans le cas d’un court- circuit peu inductif. Les méthodes de détection usuelles présentent l’inconvénient d’être relativement lentes, supérieures à 600ns. Durant le court-circuit, la croissance du courant est extrêmement rapide et ce délai est potentiellement problématique pour des applications où les modules de puissance SiC sont dimensionnés au plus juste. D’autres paramètres, témoignant du vieillissement du composant à semi-conducteur de puissance, peuvent être identifiés à travers les recherches académiques existantes. La dérive de ces paramètres devrait permettre de définir des indicateurs de vieillissement que le driver pourra surveiller. Ces mesures devraient permettre d’anticiper certaines défaillances pour des applications de haute fiabilité. Les solutions d’implémentation proposées doivent être compatibles avec la forte contrainte d’intégration du circuit driver et l’environnement sévère qui l’entoure.

Contraintes de compatibilité électromagnétique (CEM)

Les contraintes de compatibilité électromagnétiques représentent un problème majeur dans la conception des drivers de grille. Ces contraintes sont d’autant plus importantes avec l’introduction de composants grands Gap tels que le SiC. En effet, la diminution des pertes dans ces composants nécessite des commutations de plus rapides. La commutation d’un composant à semi-conducteur de puissance s’accompagne donc d’une forte variation de potentiel drain-source en un temps très court (dv/dt jusqu’à 100kV/µs) [49]. L’électronique du circuit secondaire étant référencé par rapport à la source du composant piloté, cette forte variation de potentiel peut se retrouver entre les masses primaire et secondaire, selon l’état du transistor voisin. Comme le montre la figure I-38, les dv/dt ainsi générés lors de la commutation induisent le passage de courants de mode commun (IMC) à travers les capacités parasites des éléments d’isolation [50]–[53]. Ces capacités parasites doivent donc être minimisées et/ou les chemins de circulation des courants doivent être maitrisés. La qualité de l’isolation électrique est donc un point essentiel dans la validation d’une carte driver. L’immunité aux bruits de mode commun peut-être validée par vérification de l’intégrité des signaux en présence d’une forte variation de potentiel (dv/dt) [14].

Contraintes sécuritaires / aspect normatif

Même s’il ne s’agit que d’un évaluateur technologique, le démonstrateur présenté au chapitre IV a été conçu en tenant compte d’un certain nombre de contraintes liées aux normes d’isolation. Les modules ciblés sont de type MOSFET SiC 1200V, le terme 1200V (ou 1.2kV) fait référence à la tension maximale supportée par le composant de puissance. Les tensions nominales appliquées sur ce type de composant dépassent rarement 850V. La haute densité d’intégration nécessaire dans notre démonstrateur a été obtenue au prix de certaines concessions : des diodes d’isolement haute tension de type CMS ont permis un gain d’espace non négligeable mais la tension supportée par ces diodes est limitée à 1kV. Lors de la conception de l’évaluateur technologique, une tenue en tension de drain minimale de 1kV a donc été ciblée. Un isolement électrique est qualifié par deux grandeurs : les distances d’isolement (chemin le plus court dans l’air) et les lignes de fuites (lignes de circulation du courant en cas de dépôt de poussière sur la carte).

A cela s’ajoute l’isolement entre les couches internes du PCB notamment dans le cas de transformateurs d’isolation planaires, cet isolement est en général peu contraignant grâce à la bonne tenue en tension des diélectriques de type Epoxy FR-4. Cette tenue en tension est définie par la rigidité diélectrique (FR-4 : >20kV/mm). Toutefois, les normes d’isolation imposent des restrictions beaucoup plus contraignantes pour tenir compte du phénomène de décharges partielles en environnement aéronautique entre autres. Par exemple, les normes imposent une épaisseur de FR-4 de l’ordre de 500µm pour des tensions de bus DC de l’ordre de 1500V. Le design d’une carte driver est aussi contraint par les distances d’isolement liées au claquage dans l’air ou « clearance ». Selon la norme IPC-2221, les distances d’isolement à respecter sont données dans le tableau de la figure I-40.

Autres contraintes

À bord d’un avion, on distingue deux grandes familles d’actionneurs : les systèmes propulsifs et les fonctions non-propulsives (pressurisation, dégivrage, démarrage des moteurs, commandes de vol, actionnement des trains d’atterrissage, etc.). Avant les années 2000 et l’arrivée sur le marché de l’Airbus A320, la totalité de ces systèmes faisaient appels à des circuits mécaniques, hydrauliques ou pneumatiques. De nos jours, la tendance à l’électrification des systèmes non-propulsifs est de rigueur. L’électrification des systèmes permet effectivement des gains en termes de maintenance et de poids. En outre, la propulsion électrique est un axe de recherche majeur dans un contexte de prise de conscience écologique.

Toutefois, en aéronautique, l’accroissement des performances ne peut se faire au détriment de la fiabilité des systèmes. En effet, les problématiques liées à la maintenance d’un aéronef sont nombreuses. D’autre part, les contraintes d’encombrement et de poids sont omniprésentes. Dans un aéronef, il y a corrélation directe entre la masse et la consommation de carburant.

En électronique de puissance, le refroidissement des composants est relativement coûteux en termes d’encombrement et de poids, c’est pourquoi les caractéristiques thermiques des MOSFET SiC sont très intéressantes dans le cadre d’une application aéronautique. En effet, ces derniers permettent un fonctionnement à haute température (>100°C), ce qui nécessite moins de refroidissement. Les dissipateurs thermiques peuvent alors être sous-dimensionnés, un refroidissement par convection naturelle peut être envisagé… Cependant, la proximité des circuits de commande rapproché (drivers de grille) impose également une bonne tenue en température de la carte driver. Plusieurs exemples d’intégration de carte driver sont donnés à la figure I-42. Dans le cas de notre évaluateur technologique, cette dernière contrainte n’a été que partiellement prise en compte (T ≤ 85°C).

STRATEGIE PROPOSEE

Identification des indicateurs de vieillissement

De nombreuses études sur la fiabilité des composants MOSFET SiC [55]–[60] ont été menées pour identifier les mécanismes de dégradation et définir des indicateurs de vieillissement. Ces recherches sont basées sur des méthodes de vieillissement accéléré en environnement sévère. Le composant testé est alors soumis à des cycles de stress thermique et/ou électrique (cyclages en court-circuit ou en mode d’avalanche) dans le but d’étudier son comportement à la défaillance. Concernant les tests de vieillissement, la répétition de courts-circuits est certainement l’un des plus sévères pour les composants de type MOSFET SiC. Dans [61], la température de destruction d’un composant SiC a été estimée à approximativement 650°C ±100°C, très proche de la température de fusion de l’aluminium, confirmant une excellente tenue en température des composants à Carbure de Silicium. Comme décrit dans [62], deux mécanismes de défaillance ont été identifiés sur les essais par répétition de courts-circuits. Le premier mécanisme est lié à l’augmentation de courants de fuite à la mise en conduction du transistor NPN parasite. Le second porte sur la dégradation de l’interface substrat/oxyde de grille (SiC/SiO2) et de la métallisation de source. Ces dégradations sont liées aux niveaux de température atteints pendant les cycles de courts-circuit et peuvent mener à des dommages permanents [63]. D’autre part, les modes de défaillance liés au packaging doivent être également considérés.

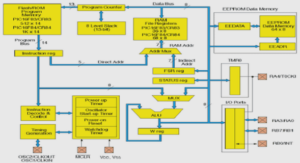

Conception d’un démonstrateur de driver de grille intelligent

Afin de répondre à la problématique de suivi de vieillissement en utilisant le circuit de commande de grille, un évaluateur technologique est proposé. Ce démonstrateur intègre un certain nombre de fonctions de base ainsi que diverses fonctionnalités de protections classiques : gestion des temps morts, détection de court-circuit, mise en protection en cas de court-circuit, renvoi de message d’erreur. A cela, s’ajoute de nouvelles fonctions de communication et les fonctions de surveillance du vieillissement telles que définies précédemment. L’intégration de composants programmables devient donc une évidence dans le cadre de ce démonstrateur. Le choix de composants de type FPGA a été réalisé pour fiabiliser au maximum le circuit driver qui devient dès lors de plus en plus complexe d’une part et maîtriser parfaitement la synchronisation temporelle des signaux d’autre part. En effet, les FPGA se caractérisent par leur grande polyvalence ainsi qu’une configuration interne basée sur des portes logiques élémentaires, ils offrent donc la possibilité de paralléliser les actions à effectuer dans la structure implémentée. Cette grande polyvalence et cette structure interne basée sur de la logique câblée se paient généralement par un coût relativement important de ces composants mais permettent en général d’identifier l’architecture numérique nécessaire au fonctionnement d’un système afin d’envisager à termes une version plus optimisée en ré-exploitant l’architecture numérique proposée par la composant FPGA. Une conception sous forme d’ASIC peut ensuite être considérée : composant intégré sur Silicium spécifiquement conçu pour l’application considérée.

Néanmoins, l’utilisation de composants programmables pose de nombreuses contraintes en termes d’encombrement sur notre démonstrateur qui comporte des circuits d’électronique analogique et dont on souhaite pouvoir vérifier le fonctionnement par oscilloscope. En effet, s’agissant d’un système isolé que l’on souhaite à double sortie (fonctionnement demi-pont), trois parties isolées peuvent être distinguées : le circuit primaire et les deux circuits secondaires. Chacun de ces circuits possédant un potentiel de masse qui leur est propre, l’ajout de plusieurs composants programmables parait inévitable.

SY STEME DE MESURE EMBARQUE

Les modules de puissance sont soumis à de fortes contraintes thermomécaniques et électriques induisant des dégradations. Ces dégradations peuvent à terme endommager le circuit de puissance voire conduire à sa destruction. Dans un contexte aéronautique, cette problématique est d’autant plus critique. Jusqu’à présent, les circuits drivers ne permettent pas d’assurer un diagnostic en temps réel du circuit de puissance. La défaillance d’un module de puissance peut causer de sévères dommages au système. La surveillance du composant de puissance a pour but la prédiction de défaillances et une maintenance simplifiée pour une meilleure fiabilité des systèmes de conversion d’énergie.

Les études de fiabilité présentées dans le chapitre I ont montré une évolution de la résistance à l’état passant ainsi qu’une augmentation significative des courants de fuite de grille en fonction des cycles de vieillissement accéléré sur des composants MOSFET SiC. Les causes de ces dérives sont principalement la détérioration de l’oxyde de grille et le décollement des fils de câblage (bondings) au sein du composant. Il est donc proposé d’implémenter sur le système driver de nouvelles fonctions permettant le suivi des paramètres critiques tels que les courants de fuite ou encore la résistivité à l’état passant du module subissant les dégradations. Un suivi précis de ces paramètres doit ainsi permettre un diagnostic en temps réel du composant de puissance.

MESURE DE LA TENSION DRAIN-SOURCE A L’ETAT PASSANT VDS(ON)

É tat de l’art

La première source de défaillance des modules de puissance concerne le packaging et notamment le raccordement de la puce par « wire-bonding » tel que décrit à la section I.C.1. Les forces de Laplace exercées dans les fils ainsi que la différence de température de part et d’autre des bondings induisent des contraintes thermomécaniques qui peuvent provoquer à terme un décollement ou des fissures sur ces fils de câblage [72]. La métallisation de surface des puces peut aussi subir des modifications par cyclage thermique [73]. Les études présentées à la section I.D.1. ont ainsi démontré une évolution de la résistivité à l’état passant au cours du vieillissement des composants de puissance. En supposant un courant invariant à température fixée, la mesure de la résistance à l’état passant du composant peut être réalisée par mesure de la chute de tension à l’état passant. Les contraintes engendrées par la mesure en ligne (online monitoring) à courant et température variables sont détaillées dans les sections II.A.2. et II.A.5.

Des méthodes de surveillance de la chute de tension à l’état passant en cours de fonctionnement ont été rapportées sur des composants IGBT [73]–[79]. Smet et al. [73] ont conclu que la mesure de VCE(on) peut être utilisée comme un indicateur de vieillissement pertinent à condition de réaliser un échantillonnage adapté. En effet, comme expliqué dans [74], le déphasage du courant par rapport à la tension appliquée est dépendant de la nature de la charge. Il est donc important de bien choisir l’instant de mesure. La figure II-1 présente l’évolution de la chute de tension à l’état passant au cours du vieillissement d’un transistor IGBT. On remarque dans un premier temps un accroissement régulier puis une augmentation rapide en fin de vie. Ce dernier phénomène est vraisemblablement dû à une casse ou à un décollement d’un ou plusieurs bondings.

Un circuit de mesure de la chute de tension à l’état passant peut aisément s’intégrer sur un driver de grille en exploitant les connectiques de drain/collecteur et source/émetteur. La connectique de drain ou collecteur (dans le cas des IGBT) est nécessaire au circuit de protection en court-circuit tel que décrit dans le chapitre I. Elle est donc préexistante sur la plupart des cartes de commande rapprochée. La principale contrainte ici est l’isolement du bus haute tension tout en garantissant une précision de mesure suffisante à l’état passant. En effet, le potentiel de référence du driver étant imposé par la connectique de source/émetteur, lorsque le composant à semi-conducteur de puissance est bloqué, le potentiel de drain/collecteur vu par le driver est maximal.

Afin de réaliser une mesure fiable de la chute de tension à l’état passant VDS(on), deux types de mesure peuvent être envisagées : la mesure en fonctionnement (« online ») ou la mesure à vide (« offline ») [79]. La mesure « offline » est la plus simple à réaliser techniquement mais nécessite un arrêt du système ou une phase à vide pour être opérée. La mesure « online » est physiquement plus complexe à mettre en œuvre mais permet un suivi en temps réel. Nous nous intéresserons uniquement aux solutions permettant un suivi des paramètres critiques du composant de puissance lors de son fonctionnement.

Ghimire et al. [75]–[79] ont proposé un circuit permettant de répondre à cette problématique dans le cas de l’IGBT. Un schéma de la solution est présenté à la figure II-2. La mesure est basée sur le principe de compensation de la chute de tension liée à la diode d’isolation D1. En effet, si D1 et D2 sont identiques ou similaires, tant que le même courant id1 circule dans D1 et D2, la tension de sortie est l’image de la tension VCE(on). Lorsque le composant est bloqué, la diode D1 n’est plus passante. La solution illustrée à la figure II-2 intègre une double mesure sur un bras de pont entier. Une source de courant est utilisée pour la polarisation des diodes D1 et D2. Une analyse de ce circuit est proposée à la figure II-3. Les diodes D3 et D4 permettent de protéger le circuit de mesure lors des variations rapides de potentiels. La chaîne d’acquisition comporte un signal CNVST permettant la synchronisation de la mesure en concordance avec la loi de commande appliquée.

|

Table des matières

CHAPITRE I : INTRODUCTION

A. ARCHITECTURE DES CONVERTISSEURS D’ENERGIE

A.1 TOPOLOGIES

A.1.1 Généralités sur les convertisseurs de puissance

A.1.2 Bras de pont

A.1.3 Onduleur triphasé

A.1.4 Structures multi-niveaux

A.2 LA CELLULE DE COMMUTATION

A.2.1 Composants à semi-conducteurs de puissance

A.2.2 Technologies

A.2.3 Modules de puissance

B. CIRCUIT DE COMMANDE DE GRILLE CONVENTIONNEL

B.1 DESCRIPTION FONCTIONNELLE

B.2 TRANSMISSION DES ORDRES DE COMMUTATION PAR VOIE ISOLEE

B.3 ALIMENTATION DU CIRCUIT DE COMMANDE RAPPROCHEE

B.4 AMPLIFICATION DE SORTIE

B.5 PROTECTIONS ADDITIONNELLES

B.5.1 Détection de court-circuit

B.5.2 Blocage en douceur (SSD)

B.5.3 Active Clamping

B.5.4 Autres circuits de protection fréquemment utilisés

C. PROBLEMATIQUE CIBLEE

C.1 FIABILITE DES MOSFET SIC

C.2 CONTRAINTES DE COMPATIBILITE ELECTROMAGNETIQUE (CEM)

C.3 CONTRAINTES SECURITAIRES / ASPECT NORMATIF

C.4 AUTRES CONTRAINTES

D. STRATEGIE PROPOSEE

D.1 IDENTIFICATION DES INDICATEURS DE VIEILLISSEMENT

D.2 MISE AU POINT DE SYSTEMES DE MESURE EMBARQUES

D.3 AJOUT DE MOYENS DE COMMUNICATION SPECIFIQUES

D.4 CONCEPTION D’UN DEMONSTRATEUR DE DRIVER DE GRILLE INTELLIGENT

E. CONCLUSIONS

F. BIBLIOGRAPHIE

CHAPITRE II : SYSTEME DE MESURE EMBARQUE

A. MESURE DE LA TENSION DRAIN-SOURCE A L’ETAT PASSANT VDS(ON)

A.1 ÉTAT DE L’ART

A.2 SYNCHRONISATION DE LA MESURE

A.3 CIRCUIT IMPLEMENTE

A.4 SIMULATIONS

A.5 DIFFICULTES RENCONTREES

A.6 ESSAIS

B. ESTIMATION DU COURANT DE FUITE DE GRILLE IGSS

B.1 ÉTAT DE L’ART

B.2 CIRCUIT DE COMMANDE RAPPROCHEE USUEL POUR MOSFET SIC

B.3 METHODE PROPOSEE

B.4 ESSAIS

B.4.1 Emulation du courant de fuite de grille par ajout d’une résistance grille-source

B.4.2 Validation de l’hypothèse d’un comportement résistif en utilisant un composant « vieilli »

B.4.3 Essais en configuration onduleur

B.4.4 Influence de la température de fonctionnement

C. COMPATIBILITE DES CIRCUITS DE SURVEILLANCE

D. CONCLUSIONS

E. BIBLIOGRAPHIE

CHAPITRE III : SYSTEME DE COMMUNICATION ADAPTE

A. ÉTAT DE L’ART SUR LA COMMUNICATION DE DONNEES DANS LES DRIVERS DE GRILLE

B. TRANSMISSION DE REQUETES SYNCHRONES

B.1 PRINCIPE DE TRANSMISSION DE REQUETES PAR IMPULSIONS COURTES

B.2 SIMULATIONS

B.2.1 Modèle comportemental du transformateur d’impulsions

B.2.2 Modélisation des courants de mode commun

B.3 ESSAIS

B.3.1 Conformité des signaux

B.3.2 Tests d’immunité aux dv/dt

B.4 ROLE DES ECRANS ELECTROSTATIQUES

C. ALIMENTATION ISOLEE COMMUNICANTE

C.1 ANALYSE DE QUELQUES CIRCUITS D’ALIMENTATION ISOLEE FREQUEMMENT UTILISES DANS LES CARTES DRIVER

C.2 PRINCIPE DE COMMUNICATION BIDIRECTIONNELLE SUR LE CANAL D’ALIMENTATION

C.3 SIMULATIONS

C.4 ESSAIS

C.4.1 Conformité des signaux

C.4.2 Tests d’immunité aux dv/dt

D. PROTOCOLE DE COMMUNICATION

E. CONCLUSIONS

F. BIBLIOGRAPHIE

CHAPITRE IV : CONCEPTION DU DEMONSTRATEUR

A. INTEGRATION DE COMPOSANTS PROGRAMMABLES

A.1 CHOIX DU FPGA

A.2 DIMENSIONNEMENT DU CIRCUIT D’ALIMENTATION DU FPGA

A.3 MEMORISATION DU PROGRAMME

A.4 BOUCLE DE SECURITE

B. DESIGN DU DEMONSTRATEUR

B.1 CARTE « MERE »

B.2 CARTE « FILLE »

C. CARACTERISTIQUES TECHNIQUES DU DEMONSTRATEUR

D. DEVELOPPEMENT LOGICIEL

E. VALIDATION FONCTIONNELLE DU DEMONSTRATEUR

E.1 ESSAIS A VIDE

E.2 ESSAIS EN DOUBLE PULSE

E.3 ESSAIS EN MODE ONDULEUR

E.4 MECANISME DE PROTECTION RAPIDE

F. CONCLUSIONS

CONCLUSION GENERALE ET PERSPECTIVES

PUBLICATIONS

ANNEXES

Télécharger le rapport complet