Télécharger le fichier pdf d’un mémoire de fin d’études

Fiabilité des circuits SMARTPOWER

Les circuits SMARTPOWER doivent répondre à certaines exigences requises pour fonctionner dans leur environnement. Les conditions les plus strictes sont celles auxquelles nous allons nous intéresser, c’est-à-dire celles du secteur automobile. En effet, une défaillance peut avoir une incidence sur la sécurité des occupants. Il est donc très important de garantir un fonctionnement sans faille de tous les composants dans des conditions extrêmes, aussi bien climatiques qu’électriques, pendant au moins toute la durée de vie du véhicule, c’est-à-dire une dizaine d’années.

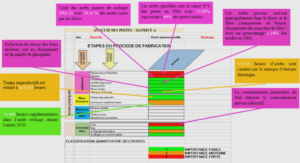

Pendant son développement, le produit doit donc suivre un parcours de qualification pour garantir les conditions exigées. Il subira des tests fonctionnels (présents de la conception jusqu’à la fabrication) et des tests accélérés. Les tests fonctionnels sont menés à trois températures (-40°C, 25°C, 125°C ou 150°C pour les modules près du moteur) qui correspondent aux conditions de fonctionnement extrêmes. Dans les tests accélérés, deux sont couramment utilisés : il s’agit du « High Temperature Operating Life » qui se fait à 150°C pendant 408h ou à 125°C pendant 1000h pour une polarisation maximale du produit et du « Highly Accelerated Stress Test » qui s’effectue à une température de 130°C, avec un taux d’humidité de 80%, sous une pression de 2 Bars pendant 96 heures. Ces deux tests permettent de simuler l’effet des années et des intempéries. L’objectif de ces tests est aussi d’analyser les types de défaillances afin de pouvoir améliorer la conception pour que le produit soit plus robuste ou d’assurer une meilleure qualité des étapes de fabrication et ainsi d’améliorer les rendements.

Une fois en production, les produits ne subissent que les tests fonctionnels au niveau wafer et sur composants montés en boîtier, en température ou à température ambiante. Seuls les échantillons prélevés régulièrement pour un contrôle qualité subissent alors tous les tests accélérés.

Malgré ces nombreux contrôles, quelques composants défaillants peuvent encore être livrés aux clients, ils se comptent en dizaine de parties par million (ppm) ; ce chiffre est évidemment trop élevé car les circuits SMARTPOWER concernent principalement les organes de sécurité. Aujourd’hui, les clients exigent un niveau de 0ppm. Pour cela, les tests accélérés au niveau wafer (Wafer Level Reliability) sur 100% des produits deviennent indispensables.

Les mémoires non volatiles dans les produits SMARTPOWER

La présence de mémoires est devenue nécessaire lorsque les clients ont voulu configurer eux-mêmes certains produits notamment pour entrer des numéros de série. Ce type de composant ne faisant pas partie des librairies SMARTPOWER, les besoins générés par l’application l’ont défini. Par la suite, la présence de mémoires a permis d’élargir le champ des applications. Enfin, la possibilité d’utiliser les mémoires non volatiles, s’est révélée être un atout vis-à-vis de la concurrence. Actuellement, ce composant se trouve par exemple dans la majorité des produits de Motorola «division automobile » et « produits standards ». On prévoit d’ailleurs une forte croissance des ventes sur les 5 prochaines années.

Les exigences sont technologiques et fonctionnelles. Technologiquement, la compatibilité avec les autres composants doit être totale ; en effet, tout ajout d’étape supplémentaire engendre un coût sur le produit final. Quant aux propriétés fonctionnelles, la mémoire remplace les composants de type « fusible » dans tout ce qui est ajustage des paramètres ; ensuite, à la demande du client, elle va servir à entrer des codes (par exemple le code pin pour un téléphone ou un numéro de série). Pour ces utilisations, peu de bits sont nécessaires : la mémoire sera très peu cyclée mais, elle devra par contre garder l’information pendant toute la durée de vie du produit.

Généralités et position des problèmes

La mémoire est donc une mémoire non volatile (NVM) que l’on peut qualifier de « Few Times Programming » dont la densité d’intégration n’est pas très grande et ne nécessite pas forcément une configuration matricielle.

Aujourd’hui, elle sert à d’autres applications et sert de paramètres fonctionnels c’est-à-dire que son état programmé ou effacé va déterminer la configuration du circuit. Par exemple, dans un air-bag, c’est l’état de la mémoire qui ordonne le repos ou la mise à feu de l’explosif qui va gonfler le coussin.

Situation de la mémoire étudiée par rapport aux structures classiques

Type de mémoire

Les mémoires se classent en deux grandes catégories : les volatiles et les non volatiles. La mémoire étudiée est une mémoire non volatile. De plus, elle est programmable et effaçable électriquement. Elle se classe donc, au niveau du principe, parmi les EEPROM basées sur les technologies FLOTOX (FLOating gate Thin OXide) ou SIMOS (Stacked gate Injection MOS).

Technologie des mémoires EEPROMs

Historiquement, la structure Stacked gate Injection MOS (Figure 2), s’appuyant sur le concept de la grille flottante a été inventée par Sze en 1969 [5]. Cette mémoire n’a pas été réalisée à cette époque car la technologie d’alors ne permettait pas de fabriquer des oxydes de bonne qualité, rendant ainsi la structure trop volatile. Pour pallier les problèmes de rétention de données, la structure a été modifiée en ménageant une petite surface pour laquelle l’oxyde est mince alors que le reste de l’oxyde est très épais. La technologie employée a été appelée FLOating gate Thin OXide ; elle a permis de réaliser et de commercialiser la première mémoire non volatile EEPROM.

Les premières mémoires utilisaient deux niveaux de polysilicium ce qui rendait le procédé technologique complexe et non compatible avec toutes les technologies. C’est pour cette raison que des mémoires à un seul niveau de polysilicium ont été créées.

Dans ce qui suit, ces deux types de technologies seront présentées, ainsi que leur avantages et inconvénients respectifs : cela permettra de justifier la structure de la mémoire étudiée.

Technologie à double polysilicium

La technologie SIMOS est représentée sur la Figure 2. Les deux couches conductrices sont du polysilicium, les diélectriques sont de l’oxyde. L’épaisseur de l’oxyde se trouvant entre le drain et le premier niveau de polysilicium est plus faible que l’oxyde situé entre les deux couches conductrices. Les charges négatives sont stockées dans la grille flottante après la programmation. La grille de contrôle sert à polariser le MOS pour lire la mémoire ou pour programmer la mémoire par effet tunnel à travers l’oxyde mince.

L’avantage d’avoir un oxyde plus mince est de pouvoir programmer la mémoire par effet tunnel de type Fowler-Nordheim sans avoir à utiliser de très fortes tensions. L’accès au drain, à la source et à la capacité de couplage permet de pouvoir effacer électriquement la mémoire par simple inversion des polarisations, ce qui est un avantage par rapport aux EPROMS.

Les méthodes de programmation et d’effacement seront abordées ultérieurement.

La technologie SIMOS a supplanté la technologie FLOTOX (Figure 3) car il n’était plus nécessaire d’avoir deux épaisseurs d’oxyde de grille. De plus, la mémoire SIMOS permet d’atteindre une plus grande densité d’intégration lorsqu’on l’utilise sous forme matricielle du fait qu’elle ne nécessite pas de transistor de sélection.

Structure de la mémoire étudiée

La mémoire étudiée est destinée à être intégrée dans une technologie SMARTMOSTM développée par Motorola. Cette technologie utilise un seul niveau de polysilicium et une seule épaisseur d’oxyde pour la capacité de couplage, la grille du transistor et la zone d’injection. La structure choisie est donc une structure de type simple poly, équivalente à la technologie SIMOS « dépliée ». Sa particularité est d’avoir un oxyde de grille de 350Å d’épaisseur. La Figure 6a représente une vue de dessus de la cellule mémoire sur laquelle nous distinguons la partie de la capacité de couplage et la partie NMOS, toutes deux reliées par un polysilicium flottant qui représente la grille flottante. Une vue en coupe (Figure 6b) montre les différentes couches technologiques. Les couches nécessaires à la mémoire sont : les puits PWell (l’un sert au transistor NMOS et l’autre à la capacité de contrôle), les couches NSD (qui sont les drain et source du NMOS et de la source de porteurs minoritaires dans la capacité de contrôle), la couche PSD (contact sur la capacité de contrôle et du puit du NMOS), l’oxyde de grille, le polysilicium et la couche de métal qui assure le contact. Les autres couches servent à isoler le composant : NBL (couche enterrée), l’ISO et le Fox (oxyde de champ), tandis que la couche épitaxiée (N-epi) assure la tenue en tension du composant.

|

Table des matières

Introduction générale

Chapitre 1 : Généralités et position des problèmes

Introduction

A. Les circuits SMARTPOWER

1. Définition et domaines d’applications

2. Fiabilité des circuits SMARTPOWER

3. Les mémoires non volatiles dans les produits SMARTPOWER

4. Situation de la mémoire étudiée par rapport aux structures classiques

4.1. Type de mémoire

4.2. Technologie des mémoires EEPROMs

4.3. Structure de la mémoire étudiée

5. Programmation des mémoires à grille flottante

5.1. Ecriture

5.2. Effacement

B. Fiabilité des mémoires

1. Généralités

2. Critères de fiabilité des mémoires non volatiles

2.1. Endurance en cycles d’effacement et de programmation.

2.2. Rétention de données

3. Test en rétention de données

3.1. Accélération thermique

3.2. Accélération électrique

4. Extrapolation de la rétention de données : Fiabilité prédictive

4.1. Modèle en 1/T

4.2. Modèle en T

4.3. Approche statistique

Conclusion

Chapitre 2 : Etude du comportement thermique de la mémoire

1.Introduction

2.Mémoire non volatile dans les technologies SMARTMOS

3. Conduction dans la couche d’oxyde de grille

3.1 Caractéristique de conduction à fort champ

3.2 Etude sur les cellules mémoires

3.3 Observations communes à toutes les distributions

3.4 Gain de charge durant le recuit

3.5 Mécanisme de conduction pour les cellules de la zone intrinsèque

3.6 Analyse des cellules extrinsèques

4. Conclusion

Chapitre 3 : Mise en oeuvre d’un nouveau test de rétention de données

1. Introduction

Table des matières

2. Absorption de la lumière

3. Mécanismes de conduction sous illumination

3.1 Caractéristiques courant tension sous illumination des cellules intrinsèques

3.2. Caractéristiques courant tension sous illumination des cellules extrinsèques

3.3. Influence de la puissance du faisceau lumineux sur la température du composant

4. Illumination d’une population de cellules mémoires programmées

4.1 Homogénéité de la transmission optique

4.2 Corrélation entre vieillissements thermiques et vieillissement optique (λ1 = 514,5 nm)

5. Faisabilité d’un test sous accélération lumineuse

6. Conclusion

Conclusion générale

Références bibliographiques

Télécharger le rapport complet