Les algorithmes de la Stéréovision dense par corrélation SAD et SSD :

Méthodologie de travail

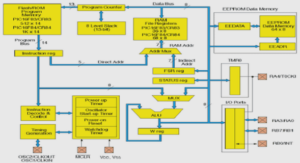

Ce travail se concentre sur le dimensionnement d’un système embarqué pour l’optimisation des capacités de stockage du système de vidéosurveillance. La figure suivante illustre les phases du flot de conception adopté dans ce projet. Notre projet se focalise, après l’étude de l’algorithme de stéréoscopie, sur l’implémentation qui se base sur la réalisation de deux étapes importantes : partie matérielle et autre logicielle. Nous commençons en premier temps par la partie matérielle: faire le dimensionnement de notre système en utilisant l’architecture graphique « OpenBus » permettant de placer les IPs (Intellectual Property) nécessaires pour l’application cible. Puis, nous sommes passés à la phase logicielle en commençant par la création d’un nouveau projet embarqué qui contient deux parties. La première partie nous permettra de générer la liste des drivers pour chaque IP utilisée dans l’architecture matérielle. Concernant la deuxième partie nous sommes arrivés à la phase intéressante qui place l’intelligence du programme écrit en langage C embarqué vers des composants électroniques en exploitant les différentes bibliothèques de fonctions disponibles dans la plate-forme logicielle. Enfin, nous compilons tous les documents que nous avons construits dans les deux parties de la conception matérielle et logicielle et le tout est envoyé vers la NanoBoard 3000 via JTAG.

•La schématique: cela comprend le câblage entre les périphériques et les broches physiques du dispositif FPGA (représentées par les composants du port). Il permet de transformer l’architecture prédéfinie dans l’OpenBus en un bloc vert qui a pour objectif de connecter chaque périphérique au composant physique qui existe réellement sur la carte de NanoBoard 3000. La figure 4.4 illustre cette division : La solution matérielle est nommée aussi solution programmable de type logique, les étapes de conception matérielle sont détaillées dans ce qui suit. Nous avons utilisé (figure 4.3) un processeur embarqué TSK3000A de 32bits parce que le processeur TSK3000 est un «open source » offert par Altium. Par contre les autres processeurs embarqués nécessitent l’achat de la licence (le processeur Nios II de l’ALTERA, Microblaze,…), puis nous avons choisi deux mémoires de taille maximale de 1M ; elles sont connectées au processeur via le port « MEM ». Les autres périphériques d’entrées / sorties tels que les LEDs, l’écran TFT, les buttons poussoirs sont connectés au processeur via le port I / O.

Afin d’interconnecter les différents IPs entre eux, nous avons utilisé deux composants d’interconnexion, l’un est appelé « Interconnect component » et est utilisé pour connecter le processeur aux mémoires et l’autre est appelé « component Arbitre » pour le connecter aux autres périphériques d’entrées / sorties. Par la suite, nous devons posséder le schéma « Top level » (figure 3.8) qui consiste à lier les blocs à l’intérieur de FPGA de l’étape précédente par les différent es ressources qui existent à l’extérieur de FPGA et disponibles sur la carte NanoBoard 3000. Ils sont modélisés sur « schématique » cette connexion est faite soit en utilisant les broches pins) qui lient les LEDs, l’horloge et les interruptions de commande, soit en utilisant le signal Harness qui sert à lier les mémoires et les écrans. Il ne nous reste maintenant qu’à définir les fichiers de contraintes qui permettent de mapper la conception dans FPGA en spécifiant le nom de chaque entrée / sortie à son correspondant dans la carte. Altium Designer met à la portée de tous les utilisateurs de NanoBoard un fichier qui regroupe l’ensemble des connexions possibles (voir annexe 4)

La plate-forme logicielle

OpenBus permet d’assembler rapidement et efficacement le processeur et le matériel du système d’E/S pour les conceptions destinées à être mises en oeuvre dans un FPGA. La NanoBoard constitue alors une plate-forme matérielle physique sur laquelle on peut rapidement mettre en oeuvre la conception, la tester et la déboguer. Pour pouvoir rapidement construire l’application qui constitue une partie essentielle du test de notre projet, on dispose également de la plateforme logicielle« Software Platform », il constitue une solution simple qui vient de compléter la construction du système matériel par OpenBus, il permet en effet au concepteur d’assembler visuellement l’ensemble du code et des pilotes de bas niveau nécessaires aux différents périphériques utilisés dans la conception, en rassemblant automatiquement tout le code de pilotes fourni avec Altium Designer. La plateforme logicielle nous permet de générer les différents drivers pour chaque IP utilisé dans le dimensionnement du système et d’ajouter d’autres fonctionnalités selon le besoin de l’application. Dans les systèmes embarqués nous ne disposons pas d’un système d’exploitation auquel on peut accéder à nos données facilement, alors que dans notre application nous avons besoin d’afficher une image sur l’écran, Altium Designer offre un éditeur de lien «–import-object= « image1.bmp »» qui nous permettra d’importer les fichiers nécessaires. La figure suivante montre le portage d’une image :

Conclusion générale

Ce stage a été réalisé au sein du Laboratoire Signaux Systèmes et Composants (L.S.S.C) du département génie électrique à la Faculté des Sciences et Techniques de Fès. Les objectifs de ce stage étaient doubles : dans un premier temps réaliser la conception d’un programme de vision 3D pouvant servir de modèle et réaliser la caractérisation de ce modèle et dans un second temps étudier et implémenter un certain nombre d’algorithmes et de techniques d’appariement. L’objectif final était d’étudier la possibilité de s’orienter vers une implémentation silicium d’un dispositif de vision 3D stéréoscopique. La vision stéréoscopique, technique simple de vision qui rejoint par le principe la vision humaine possède en effet un large champ d’applications potentielles, du jeu vidéo à l’aide à la conduite en passant par la robotique et la domotique. Ce champ est actuellement limité par le coût élevé des dispositifs. L’étude de faisabilité des algorithmes choisis était une phase transitoire vers la conception et l’implémentation sur la NanoBoard3000. La réalisation et l’implémentation des fonctions de base de stéréoscopie sur une image, était réussie malgré que nous avons encore des améliorations à faire au niveau optionnel. Vue la contrainte de temps. Finalement, ce stage présente une grande expérience pour ma future carrière, et nous espérons que notre travail témoigne de notre bonne volonté et que les membres de jury trouvent l’expression du grand honneur qu’ils nous font en acceptant de l’évaluer.

|

Table des matières

Remerciements

Liste des figures

Liste des tableaux

Liste des terminologies

Glossaire

Introduction générale

Département Génie Electrique

Chapitre I : Présentation du lieu de stage et contexte du projet

I. Présentation du laboratoire d’accueil

I-1. Axes de recherche et de développement

II. Présentation du sujet et problématique

II-1. Contexte global du projet

II-2. Interprétation de la problématique

III. Cahier des charges

Conclusion

Chapitre II: La vision stéréoscopique

I. Principe de la stéréoscopie

I.1. Principe de la vision stéréoscopique

I.2. Principe de la rectification épi-polaire

I.2.1. Rappels sur la géométrie épi-polaire

I.2.2 Rectification épi-polaire

I.2.3. Contrainte épi-polaire

II. Les algorithmes d’appariement :

II.1. Mesures de similitude

II.1.1. Principe

II.1.2. Algorithmes de similitude

III. Les algorithmes de la Stéréovision dense par corrélation SAD et SSD :

III.1. Principe :

III.2. Les étapes de décomposition de l’algorithme

Conclusion

CHAPITRE III:CONCEPTION ET REALISATION DE L’APPLICATION

I. Outils de conception et réalisation

I.1. Outils de Validation fonctionnelle

I.1.1. Logiciel DEV C++

I.1.2. Logiciel Matlab

I.2 Outils de validation Solution et Performances

I.2.1. Spécification matériel

I.2.2. Spécification logicielle

II. Etude de faisabilité des algorithmes choisis

II.1. Programmation en Matlab

II.2. programmation en C

III. Implémentation de l’algorithme sur la carte NanoBoard 3000

III.1. Méthodologie de travail

III.2. Hiérarchie des projets

III.3. Les différents types de projet

III.4. Etapes de conception de notre projet dans Altium Designer

III.4.1. Architecture matérielle

III.4.1.2. La plate-forme logicielle

IV. Résultats et interprétations

IV.1. soustraction de deux images

IV.2. image de reconstruction 3D

IV.3. Résultat

Conclusion

Conclusion générale

![]() Télécharger le rapport complet

Télécharger le rapport complet