Avec la continuelle diminution des dimensions critiques des composants de la microélectronique, les contraintes locales sont devenues une problématique incontournable. Cette problématique a fait l’objet de nombreux travaux de thèse, notamment [Rom06] et [Clé06]. En effet les contraintes affectent directement les propriétés des matériaux et donc les performances des dispositifs. Pendant longtemps, les contraintes ont été considérées comme un phénomène néfaste car elles peuvent générer des dislocations, qui provoquent généralement des courants de fuite. Lorsque les contraintes sont très élevées, elles peuvent également être responsables de délaminations, de fissurations ou même de l’apparition de cavités (phénomène de ‘stress voiding’) [Gal03]. Mais les contraintes savent aussi se montrer bénéfiques puisqu’elles améliorent sensiblement la mobilité des porteurs de charges, notamment dans le silicium [Wel94], ainsi que la retention des données dans les mémoires non-volatiles [Arg07]. Dans ce contexte, la connaissance des contraintes à l’échelle la plus locale possible devient un enjeu de taille. Afin d’augmenter la densité d’intégration des composants en microélectronique, de nombreuses applications telles que les mémoires non volatiles, se sont orientées vers le procédé d’isolation appelé STI (‘Shallow Trench Isolation’) [Faz93, Bry94]. Cette technique d’isolation consiste à graver des tranchées dans un substrat de silicium monocristallin par photolithographie puis à les remplir d’oxyde de silicium. Cela permet d’isoler physiquement et électriquement les composants (mémoires, transistors…) qui seront fabriqués dans les lignes de silicium non gravées, appelées régions actives. Les nombreuses étapes de ce procédé engendrent des contraintes mécaniques très importantes, qui avec la réduction de la taille des composants peuvent devenir critiques pour la fiabilité des dispositifs. L’objectif de ce travail de thèse a été d’évaluer les déformations et contraintes locales, c’est-à-dire à l’échelle submicronique, induites par le procédé STI.

Le procédé STI : Fabrication et contraintes mécaniques induites

Les structures étudiées durant ces travaux de thèse proviennent toutes de la société ATMEL. Atmel Corporation est un leader industriel dans le design et la fabrication de semiconducteurs avancés et plus particulièrement de microcontrôleurs, de mémoires non-volatiles (NVM), de composants pour les radio-fréquences et de détecteurs. Ces fonctionnalités sont commercialisées sous forme de produits standards, de produits standards à applications spécifiques (ASSPs) et de produits sur mesure (ASICs). Ces produits sont communément appelés circuits intégrés. Une des spécificités d’ATMEL est la fabrication de mémoires nonvolatiles à forte densité d’intégration. Ce type de produit présente des dimensions particulièrement agressives (petites par rapport au nœud technologique auquel elles appartiennent), afin de stocker un maximum d’informations sur un minimum de place. La diminution des dimensions des mémoires les rend très sensibles aux contraintes mécaniques. Si les contraintes deviennent trop élevées, on peut voir apparaître des dislocations (Figure I1) qui sont néfastes à la fiabilité des mémoires.

♦ Qu’est qu’un circuit intégré ?

C’est un composant constitué d’un boîtier muni de broches de connexions électriques. Dans ce boîtier se trouve un circuit de silicium constitué d’un réseau de transistors interconnectés entre eux, constituant des fonctions logiques ou analogiques.

Le temps de fabrication d’un circuit intégré varie de un mois à plus de deux mois (jusqu’à 500 étapes) et le coût de fabrication d’un circuit intégré est très élevé (> 500 euros pour un wafer de 200 mm). Pour s’affranchir des contaminations (par des poussières présentes dans l’air ou de produits organiques par exemple) on travaille dans un lieu d’une grande propreté concernant l’eau, l’air et les produits chimiques : la salle blanche. On parle souvent dans ce cas de ‘Clean Concept’, il s’agit de l’ensemble des règles qui visent à maintenir cet environnement propre et contrôlé.

♦ Comment cela fonctionne ?

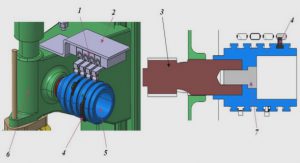

Le transistor MOS (Metal Oxyde Semiconducteur) est la brique de base de tous les circuits. Il est constitué, de trois éléments : La source, le drain et la grille. La grille est composée, d’un oxyde de grille (isolant), et de polysilicium fortement dopé (conducteur) (voir Figure I- 3). La dimension latérale de cette grille sert de référence pour indiquer le nœud technologique utilisé (par exemple 90nm). C’est grâce à leur nombre et à leur agencement que l’on obtient des circuits plus ou moins complexes. Ils sont fabriqués par la succession de multiples dépôts de matériaux conducteurs, semi-conducteurs ou isolants. Le transistor est dit passant lorsque la tension appliquée sur la grille permet le passage d’un courant entre le drain et la source. La tension minimum à appliquer pour que le transistor soit passant est appelée tension de seuil. Lorsque ce courant est nul, le transistor est dit bloqué.

Pour obtenir un circuit fonctionnel, il faut relier les transistors entre eux. C’est là qu’interviennent les différentes connections : les ‘contacts’ relient les trois composants du transistor au premier niveau de métal (transistor→ Métal) et les ‘vias’ assurent les liaisons entre les bandes de métal (Métal→ Métal). Une fois le circuit terminé, il sera protégé des agressions extérieures (rayures, humidité,..) par un dépôt d’une couche de passivation (couche isolante d’oxyde et oxynitrure de silicium). Cette partie de la fabrication est appelée ‘BackEnd Of the Line’ ou usuellement BEOL.

♦ A quoi sert une mémoire ?

L’intérêt d’une mémoire est de stocker une information sous forme binaire. Elle peut avoir deux états distincts : l’état 1 ou l’état 0. On distingue plusieurs types de mémoires : les mémoires volatiles (nécessitant d’être constamment alimentées) type SRAM (Static Random Access Memory) ou DRAM (Dynamic Random Access Memory) et les mémoires non volatiles qui gardent l’information même sans alimentation. Il existe différentes mémoires non volatiles :

– ROM : Read Only Memories. La programmation de la mémoire est faite pendant la fabrication. L’information ne peut être modifiée ultérieurement.

– EPROM : Electrically Programmable and UV erase ROM. Ces mémoires peuvent être programmées électriquement mais elles sont uniquement effaçables au rayonnement UV.

– EEPROM : Electrically Erasable and Programmable ROM. Ces mémoires sont programmables et effaçables électriquement. Ce type de mémoire est utilisé par ATMEL et se trouve dans les applications de type carte SIM (System In Module) pour téléphone portable, ‘télé payante’, carte à puce sécurisée (carte bleue, carte vitale), etc…

La mémoire de type EEPROM peut être réalisée de plusieurs manières. La plus utilisée jusqu’à présent étant la mémoire à grille flottante. Le principe de la grille flottante est de piéger les charges dans une grille non-interconnectée. Les charges restent sur la grille même sans aucune source de courant. Pour réaliser cette grille flottante, on utilise couramment un dépôt de poly-silicium supplémentaire, encapsulé par un diélectrique. Sur la Figure I- 4, on peut voir son principe de fonctionnement.

La tension de seuil devient haute (Voltage Threshold High : VTH) lorsque les électrons sont stockés dans la grille flottante. Si les électrons ont été retirés de la grille flottante, la tension de seuil de ce transistor devient beaucoup plus basse (Voltage Threshold Low : VTL). La différence de comportement de la tension de seuil permet alors d’obtenir deux états distincts (état 1 et état 0) lorsque l’on se place à une tension intermédiaire « sense threshold ». On peut ainsi ‘lire’ l’état sans le modifier.

Il y a également des essais en cours (notamment au sein d’ATMEL) pour réaliser des grilles flottantes discrètes ; il s’agit par exemple de nano-cristaux de silicium encapsulés par un diélectrique [Jac07]. Il existe aussi des mémoires de type SONOS (Silicium-Oxyde-Nitrure-Oxyde-Silicium) ou les charges seraient stockées dans une couche de nitrure [Cho06, Sch04]. D’autres types de mémoires émergentes, qui n’utilisent plus l’approche de la grille flottante, sont également en cours de développement [Mul04, Pri05] : FeRAM (Ferro électrique), MRAM (magnétique) ou PCM (Phase Change Memory). Ces dernières utilisent la différence de résistivité du matériau entre son état amorphe et cristallin [Ott04].

♦ Quand interviennent les tranchées STI ?

Les tranchées STI (Shallow Trench Isolation), ou tranchées d’isolation peu profondes en français, interviennent au tout début du procédé de fabrication des dispositifs. Ce sont les étapes de ‘Front End’, par opposition au ‘Back End’. La fabrication des tranchées STI consiste à graver des tranchées dans le silicium puis à les remplir d’oxyde afin d’isoler des zones de silicium entre elles (appelées zones actives) sur lesquelles seront faits les transistors ou mémoires dans la suite du procédé [Faz93, Bry94]. La fabrication de ces tranchées se fait indifféremment du type de composant. Depuis quelques années maintenant, le procédé STI s’est imposé pour l’isolation des dispositifs de la microélectronique au détriment du procédé LOCOS (LOCal Oxidation of Silicon) [App70, App71, Koo71]. Ce procédé a permis d’obtenir un gain important en densité d’intégration et de mieux contrôler les contraintes mécaniques. Les travaux présentés dans ce manuscrit ont été réalisés sur des structures spécifiques et représentatives des technologies mémoires non-volatiles en développement et en production à ATMEL ROUSSET.

Procédé de fabrication

Les principales étapes

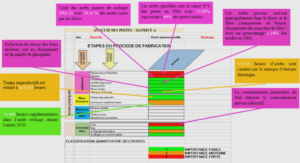

Le procédé de fabrication des tranchées STI est constitué de nombreuses étapes. Nous allons dans ce paragraphe détailler les étapes ‘clés’ intervenant dans le procédé. Ces différentes étapes peuvent être classées suivant 6 grandes catégories:

1) Les étapes de diffusion : elles regroupent principalement les oxydations thermiques, les recuits et certains dépôts. Elles se font dans des fours (tubes de quartz). Les étapes de diffusion sont toujours précédées d’une étape de nettoyage par gravure d’un oxyde sacrificiel fin.

2) Les dépôts de couches minces : ces étapes consistent à déposer divers matériaux: les oxydes de remplissage des tranchées, les couches d’isolation, les couches de ‘nitrure’, etc…

Il est à noter que les couches de nitrure de silicium sont de composition non nécessairement stoechiométrique, elles seront nommées nitrure ou SixNy dans le reste du manuscrit.

3) La photolithographie : Le but de la photolithographie est d’insoler une résine photosensible avec des radiations lumineuses à travers un masque représentant le motif à reproduire sur la plaquette de silicium. La photolithographie se passe en 3 étapes : le dépôt de la résine, l’insolation et le développement (couchage d’un solvant sur la plaquette) .

|

Table des matières

Introduction générale

CHAPITRE I : Le procédé STI : Fabrication et contraintes mécaniques induites

Introduction

1. Procédé de fabrication

1.1 Les principales étapes

1.2 La fabrication des tranchées

1.2.1 STI Standard

1.2.2 Self Aligned-STI

1.2.3 Les variables du procédé

1.2.4 En conclusion

2. Mécanique des milieux continus

2.1 Déformations et contraintes

2.1.1 La loi de Hooke

2.1.2 Représentation matricielle de VOIGT

2.1.3 Système cubique

2.1.4 Les matériaux isotropes

2.1.5 Exemples de sollicitations particulières

2.2 Changement de repère

2.3 Contraintes thermo-élastiques et intrinsèques

2.4 Déformation plastique dans le silicium monocristallin

3. Les éléments finis pour l’analyse des déformations et des contraintes

3.1 Le logiciel FEMLAB

3.2 Simulation d’un réseau de lignes

3.3 Effet de bord dans un réseau de lignes

3.4 Effet de l’anisotropie du silicium sur les déformations

3.5 Comparaison d’un modèle composite aux simulations FEMLAB

3.6 Etude par éléments finis de l’influence des dimensions des tranchées STI sur les contraintes

3.7 Comparaison des profils de déformations FEMLAB et ISE

Conclusion

Références

CHAPITRE II : Description des méthodes de détermination des déformations mécaniques locales

1. Méthodes Optiques

1.1 Raman / Micro Raman

1.2 Vers le ‘Nano- Raman’

2. Méthodes ‘électroniques’

2.1 La microscopie électronique à transmission

2.1.1 CBED

2.1.2 HR-TEM

2.2 EBSD

3. Méthodes de diffraction des rayons X

3.1 Diffraction de Kossel

3.2 Microdiffraction

3.2.1 Microdiffraction monochromatique

3.2.2 Microdiffraction en faisceau ‘blanc’

3.3 Diffraction haute-résolution sur un système périodique

3.4 Inversion directe

3.5 Diffraction Cohérente

Conclusion

CHAPITRE III : La diffraction des rayons X en haute-résolution : Application à l’étude des déformations locales dans des réseaux STI

1. La diffraction de rayons X

1.1 Amplitude diffusée dans l’approximation cinématique

1.2 Représentation de l’espace réciproque

1.3 Cas d’un système périodique

1.4 Cas d’un cristal déformé

1.4.1 Déformations homogènes

1.4.2 Déformations inhomogènes

1.5 Exemple de calcul d’intensité par transformée de Fourier

2. Mesures expérimentales

2.1 Acquisition des cartographies de l’espace réciproque

2.2 Montages expérimentaux

2.2.1 Mesures en laboratoire

2.2.2 Mesures en rayonnement synchrotron (ESRF BM 32)

2.2.3 Présentation et fonctionnement d’un synchrotron

2.2.4 Intérêt des mesures en rayonnement synchrotron

2.3 La préparation des échantillons

3. Simulation des cartographies de l’espace réciproque

3.1 Méthodologie

3.2 Calcul de l’intensité diffractée

4. Résultats expérimentaux

4.1 Interprétation des cartographies de l’espace réciproque

4.2 Etude des profils de déformations

4.3 Répétabilité des mesures

5. Cartographies simulées et comparaison aux mesures HR-XRD

5.1. Choix de la profondeur de silicium à prendre en compte

5.2. Critère de comparaison des cartographies

5.3. Résultats

5.3.1. Ajustement à un paramètre

5.3.2. Ajustement à deux paramètres

5.3.3 Conclusion

Conclusion

References

CHAPITRE IV : Etude par Diffraction X Haute-Résolution de l’influence des paramètres de fabrication sur les déformations et les contraintes générées par le procédé STI

1. Etude de deux procédés STI : comparaison SA-STI / STI Std

2. Etude des étapes individuelles du procédé SA-STI

3. Etude du matériau de remplissage des tranchées

3.1 TEOS/O3 pour des périodes de 580 nm

3.2 Mise en tension du silicium

3.2.1 Remplissage des tranchées avec l’oxyde TEOS/O3 de type HARP

3.2.2 Remplissage des tranchées avec W

4. Variations géométriques

4.1 Largeur des lignes (b)

4.2 Profondeur des tranchées (h) et épaisseur du ‘liner’ (e)

5. Variations de procédé

5.1 Orientation des lignes

5.2 Etude comparative de différents ‘liners’

Conclusion générale