Langage de programmation Java

Énergie et puissance électrique

Pour comprendre les mécanismes d’alimentation et de gestion de l’énergie, il est essentiel de clarifier la terminologie. Le courant électrique est le flux de charge électrique mesuré en ampères (Ampère A définie la quantité de charge électrique transférée par un circuit par seconde) bien que la puissance et l’énergie peuvent être définies en termes de travail qu’un système effectue. La puissance électrique est le débit auquel le système effectue une tâche, tandis que l’énergie représente la quantité totale des travaux effectués pendant une période de temps. Puissance et énergie sont mesurées, respectivement, en watts (W) et watt-heure (Wh). Une tâche est effectuée à un débit de 1W lorsque 1A est transféré à travers une différence de potentiel électrique de 1V. Un kilowatt-heure (kWh) est la quantité d’énergie équivalente à une puissance de 1 kW (1 000 W) appliquée pendant une heure. Formellement, la puissance et l’énergie peuvent être définis comme indiqué dans ci-dessous :

Où P est la puissance électrique, T est une période temps, E est la quantité totale de travaux effectués durant cette période de temps. La différence entre la puissance et l’énergie électrique est très importante car une réduction de la consommation de la puissance électrique ne réduit toujours pas l’énergie consommée. Par exemple, la consommation de puissance peut être réduite en abaissant les performances du CPU, et dans ce cas, un programme ou une tâche peut prendre plus de temps pour terminer son exécution en consommant la même quantité d’énergie. D’un côté, une réduction d’un pic de consommation de puissance entraîne une diminution des coûts d’approvisionnement de l’infrastructure, comme les coûts liés aux capacités des onduleurs (UPS), les unités de distribution d’alimentation (PDU), des générateurs électriques, les systèmes de refroidissement, et des équipements de distribution d’énergie. D’un autre côté, une baisse de la consommation d’énergie réduit les factures d’électricité. La consommation d’énergie peut être réduite temporairement via les techniques de gestion dynamique de puissance électrique (Dynamic Power Management (DPM)) ou de façon permanente via une gestion statique de puissance électrique (SPM). DPM utilise la connaissance, en temps réel, de l’utilisation des ressources et des charges de travail pour optimiser la consommation d’énergie. Toutefois, il ne diminue pas nécessairement les pics de la consommation de puissance électrique. En revanche, SPM impose l’utilisation des composants matériels les plus efficaces, tels que les processeurs, les disques de stockage, les périphériques réseau, UPS, et les alimentations électriques. Ces changements structurels réduisent généralement l’énergie consommée et les pics de la consommation de puissance Beloglazov (2013).

Consommation statique et dynamique de la puissance électrique

La majeure partie de la consommation de puissance électrique dans les circuits CMOS (Complementary Metal-Oxyde-Semiconductor) comprend une puissance électrique statique et dynamique. La consommation de puissance statique est causée par des courants de fuite qui sont présents dans n’importe quel circuit actif indépendamment des scénarios d’usage et de la fréquence de l’horloge. Cette consommation de puissance statique est, principalement, déterminée par le type de transistors et de la technologie des procédés. La réduction de la consommation de puissance statique nécessite des améliorations dans la conception de bas niveau du système. La consommation de puissance électrique dynamique est créée par l’activité des circuits (les commutateurs des transistors, les changements des valeurs dans les registres, etc.) et dépend, principalement, d’un scénario d’usage, de la fréquence de l’horloge et des opérations d’E/S. La source de la consommation de puissance électrique dynamique est le courant des court-circuit et les capacitances commutées Beloglazov (2013). Le Courant de court-circuit génère seulement 10 à 15% de la consommation électrique totale et jusqu’à présent, aucun moyen n’a été trouvé pour réduire cette valeur sans compromettre les performances.

La capacitance commutée est la principale source de consommation dynamique de puissance électrique ; par conséquent, la consommation dynamique de puissance peut être définie comme suit : Pd = aCV2 f (1.3) Où a est l’activité de commutation, C est la capacitance physique, V est la tension d’alimentation, et f est la fréquence d’horloge. Les valeurs d’activité de commutation et la capacitance sont déterminées par la conception de bas niveau du système. La réduction combinée de la tension d’alimentation et la fréquence d’horloge réside dans les racines d’une technique DPM largement utilisée appelée l’adaptation dynamique de la tension et de la fréquence « Dynamic Voltage and Frequency Scaling (DVFS) ». L’idée principale de cette technique est de réduire, intentionnellement, les performances du processeur, lorsqu’il n’est pas totalement utilisé, en diminuant la tension et la fréquence du CPU. Dans le cas idéal, il devrait en résulter une réduction cubique de la consommation électrique dynamique. DVFS est soutenu par la plupart des processeurs modernes, y compris mobile, ordinateurs de bureau, et les serveurs Pouwelse et al. (2001).

Dépendance « utilisation CPU/consommation de puissance » Le processeur (CPU) est l’élément le plus énergivore du serveur. Un modèle de CPU efficace avec une gestion d’énergie efficace peut donc jouer un rôle important dans l’efficacité globale. La consommation du processeur dépend de la tension et de la fréquence de l’horloge. La gestion d’énergie au niveau du CPU ou du coeur repose donc sur l’adaptation dynamique de la tension et de la fréquence (DVFS) ou le fait d’éteindre des coeurs Beloglazov (2013). Les données fournies par Intel Labs Minas et Ellison (2009) Beloglazov (2013) confirment que le CPU est l’élément le plus gourmand en puissance électrique suivi par la mémoire et les pertes dues à l’inefficacité d’alimentation (voir Figure1.3). Les données montrent, aussi, que le CPU ne domine plus la consommation électrique dans un serveur. Ceci résulte de l’amélioration continue de l’efficacité de puissance électrique du CPU associée à des techniques d’économie de puissance électrique (comme le DVFS) qui permettent au CPU de fonctionner dans des modes à faible consommation. Dans ces modes, un CPU consomme une fraction de la puissance totale tout en préservant la possibilité d’exécuter des programmes. Par conséquent, les CPUs des ordinateurs de bureau et des serveurs actuels peuvent consommer moins de 30% de leurs puissances totales dans des états de faible activité, ce qui conduit à des intervalles dynamiques de plus de 70% de leurs puissances électriques totales (forte activité) Venkatachalam et Franz (2005) Beloglazov (2013).

En revanche, les intervalles de puissances électrique des autres composants sont beaucoup plus étroits : moins de 50% pour les mémoires vice dynamiques (DRAM), 25% pour les lecteurs de disques, 15% pour les commutateurs de réseau, et négligeable pour le autres composants Fan et al. (2007a) Beloglazov (2013). La raison en est que seule le CPU prend en charge des modes actifs de faible consommation, alors que les autres composants ne peuvent être que complètement ou partiellement mis hors tension. Toutefois, la dégradation des performances d’une transition entre les modes actifs et inactifs est importante. Par exemple, un lecteur de disque en mode sommeil profond consomme presque pas de puissance électrique, mais une transition vers le mode actif encourt une latence mille fois plus élevée que la latence d’accès régulier. En résumé, le CPU se distingue comme étant le composant le plus influent sur la consommation de puissance électrique. Par conséquent, tous les techniques qui cherchent à améliorer la consommation électrique, se basent principalement sur la réduction du taux d’utilisation des CPUs. Pour élaborer de nouvelles politiques pour DPM et comprendre leurs impacts, il est nécessaire de créer un modèle de consommation dynamique du puissance électrique. Un tel modèle devrait être en mesure de prédire la valeur effective de la consommation électrique par un système basé sur quelques caractéristiques d’un système en cours d’exécution. Une des façons d’y parvenir est d’utiliser les fonctions de surveillance de puissance électrique qui sont intégrées dans les serveurs informatiques modernes.

Ces fonctionnalités permettent le suivi de la consommation de puissance par un serveur en temps réel et la collecte de statistiques précises de la consommation électrique. D’après les données, il est possible d’obtenir un modèle de consommation d’énergie pour un système particulier. Cependant, cette approche nécessite la collecte de données pour chaque système ciblé. Fan et al. (2007a) ont trouvé une forte corrélation entre l’utilisation du processeur et de la consommation totale de puissance électrique par un serveur. L’idée derrière le modèle proposé est que la consommation électrique par un serveur croît linéairement avec la croissance du taux d’utilisation du CPU de la valeur de la consommation d’énergie en mode veille jusqu’à la puissance consommée lorsque le serveur est pleinement utilisée. Cette relation peut être exprimée comme suit : P(u) = Pidle + (Pbusy ? Pidle)u (1.4) Tel que P est la consommation de puissance électrique estimée, Pidle est la consommation électrique d’un serveur inactif et Pbusy d’un serveur pleinement utilisé, et u est le taux d’utilisation actuel du CPU. Les auteurs ont également proposé un modèle non linéaire empirique : P(u) = Pidle + (Pbusy ? Pidle)(2u ? ur) (1.5) Où r est paramètre de calibrage qui minimise l’erreur quadratique et doit être obtenue expérimentalement : pour chaque catégorie de machines, un ensemble d’expériences de calibrages doit être effectué pour affiner ce modèle. Des expériences approfondies sur plusieurs milliers de noeuds avec différents types de charges de travail (voir Figure 1.5) ont montré que les modèles dérivés peuvent prédire avec exactitude la consommation électrique par des systèmes de serveurs avec un taux d’erreur inférieure à 5% pour le modèle linéaire et 1% pour le modèle empirique.

|

Table des matières

Table des matières

Liste des figures

Liste des tableaux

Introduction générale

1 Consommation d’énergie et qualité de service dans le Cloud Computing

1.1 Introduction

1.2 Consommation d’énergie dans le Cloud Computing

1.2.1 Énergie et puissance électrique

1.2.2 Consommation statique et dynamique de la puissance électrique

1.2.3 Dépendance « utilisation CPU/consommation de puissance »

1.2.4 Dépendance « consommation de puissance/consommation d’énergie »

1.3 Qualité de service dans le Cloud Computing

1.3.1 Définition du SLA (Service Level Agreement)

1.4 Le paradoxe « Amélioration de la qualité de service/Réduction de la

consommation d’énergie »

1.5 Conclusion

2 Virtualisation et migration des entités dans le Cloud Computing

2.1 Introduction

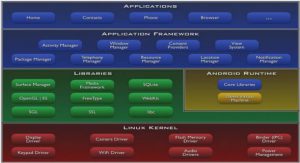

2.2 Virtualisation dans le Cloud Computing

2.2.1 Types de virtualisation

2.2.2 Hyperviseurs

2.2.3 Rôle de la virtualisation dans le Cloud Computing

2.2.4 Avantages de la virtualisation

2.3 Migration des entités dans le Cloud Computing

2.3.1 Types de migration

2.3.2 Avantages et inconvénients de la migration dans le Cloud Computing

2.4 Conclusion

3 Etat de l’art sur les approches de migration des machines virtuelles dans le Cloud Computing

3.1 Introduction

3.2 Classification des approches de migration des VMs dans le Cloud

Computing

3.2.1 Première catégorie : Optimisation du processus de migration

3.2.2 Deuxième catégorie : Optimisation de la consommation d’énergie et la qualité de service

3.3 Aperçu de l’approche proposée dans cette thèse

3.4 Etudes comparatives

3.5 Conclusion

4 Description et modélisation de la stratégie proposée de migration

4.1 Introduction

4.2 Préliminaires et vue d’ensemble

4.2.1 Problème de correspondance/allocation stable

4.2.2 Types du problème de correspondance stable

4.2.3 Procédure d’acceptation différée

4.2.4 Polarisation des correspondances stables

4.2.5 Théorème de Coase

4.3 Architecture du Cloud Computing pour la stratégie de migration proposée

4.4 Stratégie proposée de migration des machines virtuelles

4.4.1 Phase de surveillance

4.4.2 Phase de pré-négociation ou de préparation

4.4.3 Phase de négociation

4.4.4 Phase de séléction des VMs

4.5 Conclusion

5 Implémentation et interprétation des résultats

5.1 Introduction

5.2 Environnement de développement

5.2.1 Langage de programmation Java

5.2.2 Le simulateur CloudSim

5.3 Implémentation de l’approche proposée dans CloudSim

5.4 Expérimentations et résultats

5.4.1 L’impact du nombre de machines physiques et de l’utilisation du théorème de Coase

5.4.2 L’impact du nombre de machines virtuelles et de l’utilisation du théorème de Coase

5.4.3 L’impact du nombre de cloudlets

5.4.4 Discussion

5.5 Conclusion

Conclusion générale

Bibliographie

![]() Télécharger le rapport complet

Télécharger le rapport complet