Télécharger le fichier pdf d’un mémoire de fin d’études

TYPE D’UTILISATIONS DE DMOS

De manière générale, les circuits produits par l’industrie des semiconducteurs voient leurs fonctionnalités, leurs performances et leur autonomie augmenter alors que leur poids et leur taille diminuent continuellement. L’innovation de l’industrie a été particulièrement stimulée par le développement du secteur des microprocesseurs.

Depuis l’explosion des applications d’échanges d’informations, les technologies radiofréquences (R.F.) et analogiques permettent une croissance rapide du marché des communications sans-fil et représentent des technologies essentielles et critiques pour de nombreux manufacturiers. Les produits communicants remplacent désormais les ordinateurs comme levier pour la production de volume. Ainsi les produits grand public représentent la moitié de la demande de semiconducteurs. Par exemple, les téléphones cellulaires de troisième génération (3G) contiennent beaucoup plus de composants semiconducteurs qu’auparavant et constituent ainsi près de 50% du marché des cellulaires, comparé seulement à 5% il y a quelques années.

Cette partie grand public du marché des produits sans-fil sont très sensibles aux coûts. Ainsi le choix entre plusieurs technologies, comparables en termes d’impératifs techniques, se fera sur la capacité à être mature rapidement pour une production de masse.

La tendance vers une intégration et des performances plus importantes des circuits, mixant logique et analogique, développe la capacité de traitement de l’information.

La miniaturisation des composants évoluant plus rapidement que les standards d’alimentation, les tensions d’alimentation des technologies logiques, analogiques et de puissance utilisées sont différentes. Ainsi pour les technologies logiques, la réduction agressive de la taille des puces permet une réduction drastique de la tension d’alimentation (de l’ordre actuellement de 1,2V). Pour les technologies analogiques, le niveau de tension diminue modérément avec la miniaturisation (entre 2,5V et 5V). Pour les technologies de puissance, la tension d’alimentation est pratiquement constante avec l’introduction de nouvelles technologies (dépend fortement de l’application visée). (Figure I-3, [Pen05]).

Fonctionnement à l’état bloqué

A l’état bloqué, c’est-à-dire lorsque la tension grille-source est inférieure à la tension de seuil, la tension appliquée entre drain et source est soutenue principalement par la zone de déplétion qui apparaît dans la région de drift. À l’état bloqué le transistor LDMOS peut donc être assimilé à une diode PN-N+ polarisée en inverse.

Ainsi, la tension de claquage dépend des propriétés de la zone N- (dopage, longueur), de la jonction zone de canal/extension de drain mais aussi de la position et de l’épaisseur de l’oxyde de grille. Elle est aussi fondamentalement liée à la forme de la jonction : une jonction plane soutient une tension plus importante qu’une jonction cylindrique ou sphérique (Figure I-21). Cette hiérarchie peut être expliquée par un phénomène proche d’un phénomène de « pointe » où il y a une compression du champ électrique ([Cha90][Bon05]).

Transistor M.O.S. à îlots flottants (FLIMOS)

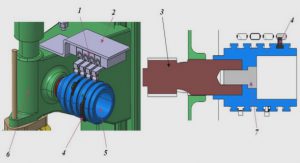

Le principe MOS à îlots flottants ou Floating Island (FLI) MOS (Figure I-26) consiste à insérer une (ou plusieurs) couche(s) dopée(s) P entre le drain et l’extrémité de la grille d’un transistor LDMOS conventionnel [Céz01]. L’insertion de cet îlot dopé de manière opposée à celle de l’extension de drain va permettre d’améliorer la répartition du potentiel et donc d’augmenter la tenue en tension du transistor.

Figure I-26 : Coupe schématique d’une cellule élémentaire d’un transistor FLIMOS de puissance Pour expliquer le fonctionnement d’un transistor à îlots flottants, nous prenons l’exemple simple d’un transistor à un seul îlot. Dans un transistor LDMOS conventionnel, le claquage est dû à un pic de champ électrique présent en surface sous l’extrémité de la grille. Dans un transistor à îlot flottant, deux pics de champ électrique apparaissent au claquage : le premier en surface sous le bord de la grille (comme dans un transistor LDMOS conventionnel), le second au niveau de la jonction « P flottant/N- drift », permettant de lisser le champ électrique le long du transistor. Le champ critique est ainsi atteint pour une tension plus élevée.

Cette structure relativement simple améliore la tenue en tension de manière non négligeable par rapport à une structure conventionnelle. En contrepartie, la résistance passante spécifique est dégradée. Ceci est dû au fait que le trajet des porteurs entre canal et drain est plus long en raison de la présence de l’îlot et de l’augmentation de la longueur de drift, nécessaire à l’insertion de la région dopée P flottante.

Le principal inconvénient d’un transistor à îlot flottant réside donc dans son encombrement supérieur par rapport aux solutions conventionnelles et dans l’augmentation du trajet des porteurs entre drain et source. Ces deux paramètres contribuent ainsi à l’augmentation globale de la résistance passante spécifique Ron.S.

Transistor M.O.S. à SuperJonction (SJMOS)

Une SuperJonction (SJ) est une succession de bandes N et P, remplaçant la zone N- d’extension de drain des transistors LDMOS conventionnels (Figure I-27, [Fuj97]). De ce fait, à surface de silicium identique, la jonction P-/N- obtenue est alors beaucoup plus étendue dans le transistor à SuperJonction que dans les transistors conventionnels.

Le mécanisme physique sur lequel repose le principe de la SuperJonction est la balance de charges. En effet une SJ nécessite un dopage et une largeur de bande judicieusement choisis (par exemple Na=Nd et Wn et Wp<<H). Le phénomène induit par l’application d’une tension positive sur le drain, alors que le transistor se trouve en mode bloqué, se déroule en deux étapes :

– dans un premier temps, les couches N et P se désertent plus vite latéralement que verticalement du fait du facteur de forme des bandes (Wn,p/H<<1).

Ainsi seule la composante latérale Ey du champ électrique augmente mais reste inférieure à la valeur du champ critique Ec.

– dans un deuxième temps, puisque la déplétion des bandes N et P est totale, la distribution du champ électrique dans le volume est uniforme. Il convient alors de considérer les régions N et P dépeuplées comme un diélectrique avec le champ critique du silicium.

Le principal avantage de la SuperJonction est que le dopage des régions N et P peut être choisi supérieur au dopage N- de l’extension de drain d’un transistor LDMOS conventionnel. Le paramètre primordial n’est plus la concentration, mais la balance de charges. Pour qu’une SuperJonction fonctionne correctement, il faut donc que les bandes N et P soient complètement dépeuplées avant d’atteindre le champ électrique critique, mais aussi que la balance des charges entre les régions N et P soit quasiment parfaite. Pour un dopage donné, en réduisant la largeur des bandes N et P, la désertion est de plus en plus totale : la distribution uniforme du champ électrique s’en trouve alors améliorée (Figure I-28).

PROBLEMATIQUE DE L’INTEGRATION D’UN CIRCUIT DE PUISSANCE

Le développement de filières de puissance ne se limite pas aux aspects liés au développement de composants. Etant donné le niveau des tensions appliquées, une bonne isolation entre blocs est nécessaire. Nous allons développer dans la partie suivante les différents types d’isolation et la problématique de l’intégration d’un circuit de puissance sur silicium.

Faire cohabiter de nombreux composants, fonctionnant sous des tensions différentes et gérant des niveaux de courants sans aucun rapport, nécessite une parfaite isolation entre éléments. Les technologies actuelles peuvent intégrer concrètement des blocs CMOS complexes, des mémoires mais aussi une partie dite de « puissance ». Cette intégration, et la réduction des dimensions qui y est associée, nécessite de résoudre le problème de l’isolation galvanique entre les différents blocs. Actuellement il existe deux familles principales d’isolation pour résoudre ces problèmes [Mor07] :

– les technologies d’isolation par jonction,

– les technologies d’isolation par diélectrique.

Les technologies d’isolation par jonction constituent les solutions conventionnelles les plus utilisées actuellement. Cependant, la densité de plus en plus importante de composants pose de nombreux problèmes que nous allons détailler dans un premier temps. Dans un second temps, nous verrons les technologies d’isolation par diélectrique.

Diode Schottky

Une autre solution consiste à insérer une diode Schottky (Métal- Semiconducteur) à l’intérieur du caisson du composant de puissance à l’origine du courant de substrat [Gon01]. La tension de seuil d’une diode Schottky étant faible, elle va rentrer en conduction avant la diode d’isolation de substrat, retardant ainsi sa mise en conduction.

Il faut cependant noter que son intégration ne peut se faire sans avoir résolu la faible tenue en tension en mode bloqué, problème inhérent aux diodes Schottky.

Transistor M.O.S. isolé

Utilisé en général pour les dispositifs 15/20V, le transistor isolé consiste à réaliser le drain non plus dans une couche N- mais dans une couche P- de sorte que le drain n’ait plus de contact direct avec la couche N- [Mor07]. Cette couche N- est alors contactée via la couche enterrée N+. Ainsi, lorsque le drain du transistor est polarisé négativement et que la diode drain/P- passe en direct, le fort courant injecté par celle-ci est collecté par la couche contactée N+. Il n’y a plus aucune injection de porteurs minoritaires dans le substrat.

INTERET DE LA TECHNOLOGIE S.O.I. RF

Nous allons ici montrer l’intérêt du SOI par rapport aux technologies standard réalisées sur substrat massif, en insistant sur l’amélioration des performances RF.

Nous avons vu que la diminution de la longueur de grille des transistors MOS avait permis d’atteindre des fréquences de fonctionnement de l’ordre du gigahertz (Figure I-7). Ainsi la technologie CMOS représente la meilleure possibilité d’intégration des fonctions RF, digitale et analogique sur une même puce. Bien qu’elle puisse se révéler onéreuse, cette approche SoC reste économiquement préférable. Les technologies CMOS sur substrat massif garantissent aujourd’hui de bonnes performances pour les éléments actifs des parties analogiques et radiofréquences ( T f élevé, faible bruit, bonne linéarité, …). De plus, une forte densité autorise l’intégration des processeurs numériques. Il reste pourtant des blocages technologiques importants.

En effet, pour réaliser des systèmes mixtes intégrés, les technologies doivent développer :

• des interconnexions de bonne qualité afin de réduire les pertes (faible résistivité et faibles capacités parasites),

• une bonne isolation entre les différents blocs analogiques, radiofréquences et numériques afin de réduire les effets de bruit par le substrat,

• et une consommation totale des systèmes réduite au maximum.

Les technologies SOI pour les applications RF peuvent apporter des avancées significatives par rapport à ces difficultés. Nous allons, dans les paragraphes suivants, expliquer les phénomènes de base et les avantages liés au développement d’une filière technologique SOI RF.

Élimination des capacités de jonctions

Le principal avantage connu des technologies SOI RF réside dans la réduction des capacités de jonctions des transistors. Grâce à la présence de l’oxyde enterré, les diffusions de drain et de source sont circonscrites à la couche de silicium supérieure : la partie inférieure des diffusions touche l’oxyde enterré. Ainsi en SOI on remplace une capacité de jonction Cjonctions par une capacité d’oxyde de plus faible valeur.

Effet de substrat flottant et réduction de la consommation

En technologie SOI, grâce à la présence de l’oxyde enterré qui isole le substrat de conduction (appelé aussi « body ») du substrat de support, il existe un couplage capacitif entre la grille et le substrat, si ce dernier n’est pas contacté à un potentiel (le transistor est dit « flottant » ou « à substrat flottant »). De ce couplage va résulter une charge et une décharge du substrat flottant, qui va créer une variation dynamique de la tension de seuil du transistor.

En mode statique, la variation du potentiel de body provient de mécanismes d’accumulation et de déplétion de charges à l’intérieur de celui-ci. L’accumulation dans le substrat flottant est due aux courants de fuite latéraux des jonctions, au couplage capacitif entre la grille et le body et au phénomène d’ionisation par impact, présent uniquement à tension de drain élevée.

L’ionisation se produit lorsque les porteurs, accélérés par un fort champ électrique, atteignent leur vitesse de saturation. Les collisions entre ces porteurs et le réseau (i.e. les atomes fixes de la couche de silicium) créent des paires électrons/trous dont certaines ne se recombinent pas. Les électrons libres sont alors accélérés par le champ vers le drain, alors que les trous s’accumulent dans le body flottant (Figure II-3). La barrière de potentiel de la diode source-body empêche l’évacuation des trous vers la source : le potentiel du body augmente.

|

Table des matières

CHAPITRE 1 : TECHNOLOGIES DE PUISSANCE

1. INTRODUCTION : CONTEXTE HISTORIQUE ET TECHNOLOGIQUE

2. TYPE D’UTILISATIONS DE DMOS

2.1. Gestion d’énergie

2.2. Applications Radiofréquences

3. QU’EST-CE QU’UN AMPLIFICATEUR DE PUISSANCE ?

3.1. Définition d’un amplificateur de puissance

3.2. Figures de mérite

3.3. Classes de fonctionnement

4. ÉTAT DE L’ART DES COMPOSANTS DE PUISSANCE DE TYPE MOS

4.1. Transistor DMOS Latéral (LDMOS)

4.2. Transistor M.O.S. à tranchées (LUDMOS)

4.3. Transistor M.O.S. à îlots flottants (FLIMOS)

4.4. Transistor M.O.S. à SuperJonction (SJMOS)

5. PROBLEMATIQUE DE L’INTEGRATION D’UN CIRCUIT DE PUISSANCE

5.1. Isolation par jonction

5.2. Isolation par diélectrique

5.3. Conclusion

6. CONCLUSION

BIBLIOGRAPHIE

CHAPITRE 2 : TECHNOLOGIES S.O.I. ET PUISSANCE SUR S.O.I

1. INTRODUCTION

2. LA TECHNOLOGIE S.O.I. : PRESENTATION

3. INTERET DE LA TECHNOLOGIE S.O.I. RF

3.1. Élimination des capacités de jonctions

3.2. Effet de substrat flottant et réduction de la consommation

3.3. Compatibilité avec des substrats Hautement Résistifs

4. INTEGRATION DE COMPOSANTS DE PUISSANCE SUR S.O.I.

4.1. Intérêt de la puissance sur S.O.I.

4.2. Impact du SOI sur les caractéristiques de puissance

4.3. Structure d’étude et procédé de fabrication retenus

5. CONCLUSION : LES DEFIS A RELEVER POUR LA REALISATION DE LDMOS SUR SOI

BIBLIOGRAPHIE

CHAPITRE 3 : OPTIMISATION ELECTRIQUE DU DISPOSITIF

1. INTRODUCTION

2. FONCTIONNEMENT ET OPTIMISATION STATIQUE DU DISPOSITIF

2.1. Caractéristiques statiques générales

2.2. Influence de paramètres géométriques sur les performances à l’état passant

2.3. Caractéristiques statiques générales

2.4. Compromis SRon/BV et étude de comportement de claquage

2.5. Comportement de claquage

2.6. Conclusion et applications de gestion d’énergie

3. CONTROLE DES EFFETS FLOTTANTS

3.1. Technologie 130nm

3.2. Technologie 65nm

3.3. Bruit basse fréquence

4. CARACTERISATION EN HAUTE FREQUENCE

4.1. Étude de l’impact de la largeur W (à Wtotal constant)

4.2. Réduction de la longueur de l’extension Lext

4.3. Réduction du recouvrement oxyde de protection/grille (Ov)

4.4. Etude des transistors LDMOS flottant

4.5. Réduction du recouvrement grille/extension (avec Ov nul)

4.6. Conclusion

5. CONCLUSION

BIBLIOGRAPHIE

CHAPITRE 4 : ETUDE DES PHENOMENES THERMIQUES ET ENERGETIQUES

1. INTRODUCTION

2. ÉTUDE DE L’AUTOECHAUFFEMENT

2.1. Introduction : présentation du problème

2.2. Description des procédures de mesures et de simulation

2.3. Résultats et discussion

2.4. Conclusion

3. COMPORTEMENT ENERGETIQUE DU DISPOSITIF

3.1. Principe de la mesure pulsée à ligne de transmission (TLP)

3.2. Caractérisation TLP du composant incriminé

4. ÉTUDE DE FIABILITE DU DISPOSITIF

4.1. Problématique : dérive rencontrée avec une intégration différente

4.2. Dérive en mode « porteurs chauds » (1er ordre)

4.3. Conclusion

5. CONCLUSION

BIBLIOGRAPHIE

Télécharger le rapport complet