Télécharger le fichier pdf d’un mémoire de fin d’études

Les microprocesseurs

Une des principales limitations technologiques propre aux microprocesseurs est le fossé grandissant qui sépare les performances des microprocesseurs et celles de leurs mémoires associées [Mahapa99]. L’expression anglophone Processor-Memory Bottleneck est couramment utilisée pour désigner cette problématique. Sur le fond, celle-ci est simple : les performances des processeurs augmentent plus rapidement que les vitesses d’accès à la mémoire. Pour contrecarrer ces limitations propres aux architectures planaires, une réorganisation du système {microprocesseur / mémoires} sur plusieurs niveaux superposés réduirait considérablement les longueurs d’interconnexions qui relient les deux entités. Deux cas de figure se dégagent de cette constatation [Garrou08v2]:

1°) un empilement de mémoires sur un processeur gagnerait en largeur de bande (memory bandwidth) par la réduction des longueurs d’interconnexions dédiées aux communications externes entre le processeur et les niveaux de mémoire cache. Il s’agit ici d’une architecture 3D dite « mémoire sur logique ». Contrairement à ce que l’on pourrait penser de prime abord, les échauffements thermiques induits par les différents niveaux physiques de composants ne sont pas réellement problématique dans cette approche. D’une part parce que les mémoires consomment peu de puissance (donc dissipent peu de chaleur), d’autre part parce que le processeur est directement connecté au dissipateur thermique, comme illustré à la Figure 1.23 [Morrow07] ;

2°) un empilement de blocs logiques fonctionnels permettrait de réduirait les longueurs d’interconnexions semi-globales qui relient plusieurs blocs d’une même microarchitecture14, et ainsi gagnerait en densité d’intégration de composants. Le principal intérêt est de réduire les temps de latence entre blocs et de diminuer la consommation de puissance tout en augmentant les performances. L’autre principal intérêt est de réduire la surface occupée par le microprocesseur comparativement à son homologue 2D [Black06], comme illustré à la Figure 1.24. Il s’agit d’une architecture 3D dite « logique sur logique ».

Les capteurs

Les capteurs ont été les premières applications industrielles à passer sous architecture 3D. Pour l’instant, cette famille de produit est principalement pilotée par les imageurs CMOS (capteurs d’images). La problématique est simple : dans le but de miniaturiser les caméras pour les applications portatives, les systèmes de packaging couramment utilisés (comme le wire-bonding) peuvent être remplacés par des TSV de type wafer-level packaging (dimensions relâchées). Ainsi, plusieurs procédés ont vu le jour depuis 2004 [Takahashi04, Leib04, Garrou04, Henry08] en présentant l’intégration des TSV comme remplaçant du câblage (Figure 1.27). D’un point de vue économique, les débouchés potentiels de cette technologie de packaging sont importants en termes de volume de production (téléphonie mobile, automobile, médical, etc.).

Une architecture plus évoluée est également en cours de développement chez STMicroelectronics [Coudrain08]. Il s’agit cette fois d’intégrer les composants logiques associés à chaque pixel (i.e. trois transistors par pixel) sur un niveau physique distinct, puis de réaliser un second niveau par-dessus le premier pour intégrer les composants optiques, comme illustré sur la précision de l’image augmente) tout en conservant un facteur de forme restreint correspondant aux spécifications des applications portatives. Cette technologie se rapproche fortement de l’intégration 3D très haute densité (dite séquentielle ou monolithique, cf. paragraphe 1.2.3.4), ce qui la laisse encore éloignée des objectifs de production actuels.

Les systèmes électroniques hétérogènes

Les applications électroniques portatives grand public sont, pour une grande majorité, gouvernées par les problématiques du facteur de forme, c’est-à-dire l’encombrement occupé par la puce dans le produit final, et des performances électriques. La tendance actuelle étant à la politique de miniaturisation tout en augmentant les performances et autres fonctionnalités du produit, l’intégration 3D, et particulièrement le 3D-WLP, permet de supplanter les traditionnels assemblages de type SiP avec connectiques par wire bonding. En effet, le câblage externe possède des propriétés électriques bien inférieures à celles des TSV (notamment en termes de résistance et d’inductance), et occupe une place non négligeable autour de la puce.

Le concept de cet assemblage 3D est de fabriquer les différents étages technologiques en utilisant une technologie adaptée pour chacun (mature, avancée, etc.), ce qui permet de gérer les coûts de fabrication de chaque niveau au plus juste. Ensuite, les circuits sont généralement interconnectés par collage métallique (alliage, micro-inserts, etc.) puis le report des contacts en face arrière est réalisé sur un des circuits à l’échelle du wafer. On dit alors de ce circuit qu’il sert d’interposer, c’est-à-dire qu’en plus de sa fonction électrique propre liée à sa circuiterie, il joue un rôle de connecteur unique pour le packaging.

Les principaux secteurs industriels intéressés sont les fabricants de systèmes électroniques destinés à la téléphonie mobile, aux jeux vidéo, au monde du numérique en général. Une démonstration technologique a été présentée en 2009 par STMicroelectronics et le CEA-LETI, qui consistait à interconnecter une puce en technologie avancée 45 nm avec une puce en technologie mature (130 nm), le tout étant fixé à un PCB classique [Chéramy09]. L’application finale est un circuit destiné à un décodeur numérique (set-top box15). Le schéma de principe ainsi que des images MEB de l’empilement et des TSV sont présentés sur la figure suivante.

Amincissement du silicium

Le substrat ou les puces collés doivent être amincis, généralement en dessous de 100 Em de manière à pouvoir réaliser les TSV par la suite. L’étape d’amincissement consiste à arracher progressivement le surplus d’épaisseur du substrat par action mécanique dans un premier temps (amincissement grossier), puis par action mécano-chimique dans un second temps (amincissement fin). Le choix du substrat s’avère donc crucial. En effet, l’oxyde enterré du substrat SOI20 – appelé BOX21 – constitue une couche d’arrêt pour l’étape d’amincissement du substrat supérieur. Cette étape s’avère plus complexe sur un substrat de silicium bulk, notamment lorsque les épaisseurs finales de silicium recherchées approchent la dizaine de microns (amincissement extrême pouvant être réalisé sur substrat bulk, approprié pour le 3D-IC). De plus, la couche d’oxyde enterré étant situé seulement à quelques microns de profondeur, les épaisseurs rémanentes sont beaucoup plus faibles que sur du silicium bulk, permettant ainsi de créer des vias traversants de plus petite taille que sur silicium bulk.

Mode de réalisation des TSV

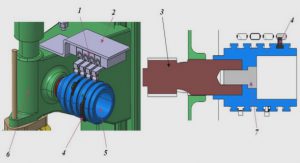

Au-delà du choix initial de travailler selon l’approche Via First ou Via Last, la constitution physique des TSV peut être généralisée à un ensemble de quatre étapes génériques :

1°) Gravure du TSV dans le silicium ;

2°) Isolation des flancs du TSV ;

3°) Dépôt du matériau barrière ;

4°) Remplissage du TSV par un matériau conducteur.

On se propose ici de décrire succinctement ces différentes étapes en stipulant pour chacune d’elles les enjeux technologiques, ainsi que quelques exemples de procédés largement utilisés. Gravure du TSV dans le silicium.

La gravure silicium a connu une rupture technologique cruciale pour le développement des technologies 3D dans le milieu des années 90. A cette période, Bosch a inventé un procédé de gravure plasma, plus connu sous l’acronyme DRIE22, qui permit de graver le silicium de manière verticale et profonde [Laermer96a, Laermer96b]. La DRIE, communément appelée Procédé Bosch, consiste en une série répétée de réaction de gravure anisotrope du silicium par SF6, suivie d’une passivation par C4F8 qui génère un dépôt CF2. La Figure 1.35 (gauche) illustre le procédé de base. Le procédé Bosch présente une sélectivité élevée ainsi qu’une gravure particulièrement verticale. Quelques exemples de gravures profondes sont montrés à la Figure 1.35 (droite) avec les défauts dus à l’utilisation du procédé de base. Des améliorations techniques ont permis d’optimiser le profil de gravure pour éviter la présence de tels défauts [Tezcan06, Hopkins01].

Interactions possibles avec les technologies CMOS

En choisissant d’implémenter une nouvelle technologie d’intégration avec des composants qui n’ont pas été conçus pour cela, la question de la compatibilité entre les deux technologies s’avère légitime. Plus particulièrement dans le cas présent, il est nécessaire de savoir si le rapport d’échelle entre les deux n’est pas problématique. En effet, les efforts continuels développés en R&D pour suivre la loi de Moore aussi longtemps que possible ont un sens logique : la taille des composants a tendance à diminuer pour permettre une intégration de plus en plus dense et donc des performances améliorées de génération en génération. Paradoxalement, les technologies d’intégration 3D actuellement développées se rapprochent plus des technologies de packaging dans leurs dimensions. Le fait est que ces deux domaines technologiques doivent co-habiter et fonctionner de manière optimale. Pour se faire une idée précise de ce rapport d’échelle entre les deux types de technologies, on représente respectivement, à échelle réelle, un TSV de diamètre 2 Em (soit l’un des plus petits TSV actuellement réalisables) placé à proximité d’un transistor 45 nm (Figure 1.37), et un TSV similaire à proximité d’un transistor 0.8 Em (Figure 1.38). Ces deux exemples reprennent le cas de figure développé au paragraphe 1.2.2.3 [Ferrant08]. On comprend bien que le TSV peut avoir une influence bien plus importante dans le cas de la Figure quantifier cette influence qui s’exprime sous deux formes différentes :

– Le TSV étant rempli par un matériau conducteur, la différence de dilatation thermique entre ce matériau et le silicium peut engendrer un niveau de contraintes résiduelles inhabituel dans le silicium. De plus, le TSV peut être source de perturbations de natures variées, comme la génération de nouvelles contraintes dues aux procédés technologiques (e.g. l’influence de l’amincissement du silicium sur le composant), ou bien une source de bruit de substrat inhabituelle.

Il s’agit de phénomènes d’impact technologique ;

– L’intégration 3D utilise la dimension verticale dans des circuits ayant été conçu en deux dimensions seulement. Se pose alors le problème de l’évolutivité des méthodes de conception de circuits : faut-il rendre compatible les outils de design actuels ou bien rompre complètement en proposant un schéma de conception novateur ?

Il s’agit de phénomènes d’impact conceptuel.

Impact thermomécanique lié aux procédés 3D sur les composants

L’impact des procédés technologiques liés à l’intégration 3D est un sujet de plus en plus étudié. Intel Corporation a initié le processus dès 2004 [Morrow04] où une réalisation d’oscillateurs en anneau implémentés en technologie 65 nm sur le niveau supérieur avec les contacts repris sur la face arrière amincie par des TSV est présentée. Les composants CMOS sont réalisés sur silicium contraint (strained silicon). L’objectif de l’étude est de comparer les performances électriques d’un oscillateur en anneau implémenté sur la strate amincie (à moins de 20 Em) avec celles d’un même oscillateur implémenté dans la strate inférieure non amincie. Il est à noter que les deux oscillateurs (haut et bas) ne communiquent pas entre eux.

La Figure 1.39 présente la fréquence d’oscillation normalisée (par rapport à la fréquence moyenne d’oscillation d’oscillateurs équivalents implémentés sur des substrats non collés) en fonction de la tension d’alimentation Vcc normalisée (par rapport à la tension d’alimentation de la technologie 65 nm, Vcc0). On observe que la différence de fréquence d’oscillation entre l’oscillateur implémenté dans le silicium aminci et celui dans la strate inférieure n’excède pas 2%, alors que la différence de fréquence entre l’oscillateur aminci et l’oscillateur non collé (référence) n’excède pas 5%. Les performances électriques du circuit aminci sont semblables à celles du même circuit dans le silicium massif.

Notions théoriques sur le couplage par le substrat

Le terme « couplage par le substrat », qui est un synonyme de l’expression « bruit substrat », fait référence à un phénomène pour le moins critique. Son action sur un circuit intégré peut être catastrophique ou bien extrêmement limitée, mais dans tous les cas, il est toujours plus prudent de le prendre en compte au moment de la conception. Néanmoins, le bruit substrat n’en reste pas moins un phénomène impalpable et invisible, ce qui lui confère une part de mystère qu’il convient de lever. Le sous-chapitre 2.1 est principalement basé sur les travaux de thèse d’Olivier Valorge [Valorge06] et sur un ouvrage de référence écrit par Eduardo Charbon et al. [Charbon01].

Sources de bruit substrat

Plusieurs sources différentes ont été identifiées quant à la génération de bruit substrat. On ne traitera ici que des trois principales, à savoir le bruit d’alimentation, le couplage capacitif et l’ionisation par impact, les autres ayant une influence plus restreinte.

Bruit d’alimentation

En considérant le circuit intégré dans son intégralité, c’est-à-dire avec le packaging associé, son positionnement sur la carte imprimée ainsi que les connectiques nécessaires à son fonctionnement, il apparaît que les lignes d’alimentation, peu importe le niveau JISSO considéré (voir paragraphe 1.2.3.1.), constituent autant de sources génératrices de bruit substrat. En effet, ces structures d’alimentation (masse y compris) représentent des inductances, des capacités et des résistances parasites qui interagissent directement avec le substrat par l’intermédiaire des contacts de polarisation du substrat présents sur l’ensemble de la surface d’un circuit. Il est à noter que les bruits d’alimentation constituent la principale source de parasitage dans le substrat. On distingue quatre sources de bruit substrat liées à l’alimentation :

– Les lignes d’alimentation : le courant électrique parcourt un chemin spécifique depuis son entrée sur le circuit imprimé jusqu’au coeur du circuit intégré. L’ensemble des câblages nécessaires à son acheminement constitue des sources de bruit ;

– Le courant de fonctionnement : dans les circuits logiques, certains signaux (comme la fréquence d’horloge) sont dynamiques, c’est-à-dire qu’ils vont commuter d’un état logique à un autre selon une certaine fréquence. Ces commutations engendrent des pics de consommation de courant plus ou moins importants, ces derniers engendrant des perturbations proportionnelles dans le substrat ;

– L’impédance du coeur du circuit : cette impédance est la mise en parallèle des impédances de chacun des composants élémentaires du circuit, si l’on considère que tous sont connectés au même point d’alimentation ;

– Les sauts d’alimentation et de masse : le bruit d’alimentation d’un circuit numérique est le fruit de l’interaction des trois précédentes sources décrites cidessus.

Les composants parasites des lignes d’alimentation forment avec l’impédance du coeur digital des réseaux de type RLC dont les oscillations sont entretenues par les pics de courant régulièrement appelés par les portes logiques de l’ensemble du circuit.

Couplage capacitif

Certaines capacités parasites propres aux structures mêmes d’un circuit génèrent un couplage des signaux bruités au substrat. Les principales sources de ce couplage sont classées en quatre catégories et sont explicitées par la Figure 2.1 :

– (a) les capacités MOS des transistors : l’oxyde de grille joue le rôle du diélectrique, la grille et le substrat les rôles des deux électrodes. Le PMOS est moins sensible que le NMOS car il est ancré dans un caisson dopé N (nwell) qui l’isole mieux du substrat (cf. Figure 2.5) ;

– (b) les capacités drain/substrat et source/substrat : les sources et drains des transistors CMOS forment des diodes PN avec le substrat. Celles-ci sont polarisées en inverse et se comportent donc comme une liaison capacitive entre le plot et le substrat ;

– (c) les capacités interconnexions/substrat : les niveaux locaux d’interconnexions constituent des électrodes qui se couplent au substrat par effet capacitif ;

– (d) les capacités caisson/substrat : dans les cas des transistors PMOS, le caisson nwell utilisé pour isoler le transistor du substrat dopé P constitue une jonction PN avec le substrat, polarisée en inverse afin d’isoler électriquement les composants à l’intérieur du caisson.

|

Table des matières

Introduction

Chapitre 1

1.1. Evolution et limitations des circuits intégrés

1.1.1. Limitations des circuits intégrés planaires

1.1.1.1. Interconnexions : un problème a priori simple

1.1.1.2. Une petite histoire des interconnexions

1.1.1.3. Des solutions temporaires pour dépasser ces limitations

1.1.1.4. Organisation du réseau d’interconnexions : architecture multiniveaux

1.1.2. Évolution et limitations des systèmes électroniques intégrés

1.1.2.1. Système sur Puce (SoC)

1.1.2.2. Système en boîtier (SiP)

1.2. Vers une solution réaliste : l’intégration 3D

1.2.1. Historique de l’intégration 3D

1.2.2. De l’intérêt d’intégrer verticalement

1.2.2.1. Amélioration des performances des circuits homogènes

1.2.2.2. Une architecture adaptée à l’intégration hétérogène

1.2.2.3. Optimisation des coûts et du rendement de production

1.2.3. Des architectures verticales configurables

1.2.3.1. Hiérarchisation

1.2.3.2. Intégration verticale moyenne densité : 3D-WLP

1.2.3.3. Intégration verticale haute densité : 3D-IC

1.2.3.4. Intégration verticale très haute densité : 3D monolithique

1.2.4. Applications

1.2.4.1. Les microprocesseurs

1.2.4.2. Les mémoires

1.2.4.3. Les capteurs

1.2.4.4. Les systèmes électroniques hétérogènes

1.2.5. Options d’intégration

1.2.5.1. Empilement

1.2.5.2. Orientation des circuits

1.2.5.3. Alignement

1.2.5.4. Collage

1.2.5.5. Amincissement du silicium

1.2.5.6. Connexions inter-strates

1.2.5.7. Connexions intra-strate (TSV)

1.2.5.8. Mode de réalisation des TSV

1.3. Interactions possibles avec les technologies CMOS

1.3.1. Impact thermomécanique lié aux procédés 3D sur les composants

1.3.2. Influence sur la conception de circuit

1.4. Contributions du doctorat

1.4.1. Synthèse de l’état de l’art

1.4.2. Démarche proposée

Chapitre 2

2.1. Notions théoriques sur le couplage par le substrat

2.1.1. Sources de bruit substrat

2.1.1.1. Bruit d’alimentation

2.1.1.2. Couplage capacitif

2.1.1.3. Ionisation par impact

2.1.2. Propagation du bruit et réception par les composants

2.1.2.1. Mécanismes de propagation

2.1.2.2. Mécanismes de réception

2.1.3. Solutions d’isolation du substrat

2.1.3.1. Anneaux de garde

2.1.3.2. Couches enterrées

2.1.3.3. Caissonnage

2.1.3.4. Connexion à la face arrière

2.2. Du composant et de son environnement

2.2.1. Notions théoriques relatives au transistor

2.2.1.1. Transistors NMOS et PMOS

2.2.1.2. Caractéristiques électriques

2.2.1.3. Facteurs influençant les performances du composant

2.2.2. Notions théoriques relatives à l’inverseur

2.2.2.1. Description électrique

2.2.2.2. Caractéristiques électriques

2.2.2.3. Facteurs influençant les performances de l’inverseur

2.2.3. Composants intégrés dans une structure 3D

2.3. Couplage induit par l’intégration 3D sur le composant

2.3.1. Méthodologie

2.3.1.1. Considérations générales

2.3.1.2. Modèles électriques

2.3.1.3. Structure simulée

2.3.1.4. Transistor simulé

2.3.1.5. Simulation du couplage induit par l’intégration 3D

2.3.2. Couplage induit par le TSV

2.3.2.1. Considérations générales

2.3.2.2. Influence de la zone d’exclusion

2.3.2.3. Influence de l’épaisseur d’isolation du TSV

2.3.2.4. Influence de l’épaisseur de silicium

2.3.3. Couplage induit par le niveau de redistribution (RDL)

2.3.3.1. Considérations générales

2.3.3.2. Influence de l’épaisseur de silicium

2.3.3.3. Influence de l’épaisseur d’isolation du RDL

2.3.4. Impact couplé du TSV et du RDL

2.3.4.1. Isolation homogène

2.3.4.2. Isolation hétérogène

2.3.5. Influence des signaux parasites sur le couplage

2.3.5.1. Considérations générales

2.3.5.2. Influence de la durée du front de potentiel du signal agresseur

2.3.5.3. Influence de l’épaisseur d’isolation du TSV

2.3.6. Solutions pour la réduction du couplage substrat

2.3.6.1. Augmentation de la résistivité du silicium massif

2.3.6.2. Séparation physique de la zone active et du TSV

2.3.6.3. Implémentation d’une masse en face arrière

2.4. Couplage induit par l’intégration 3D sur l’inverseur

2.4.1. Modélisation circuit

2.4.1.1. Élaboration du modèle électrique

2.4.1.2. Calibration du modèle

2.4.1.3. Méthodologie

2.4.2. Impact du TSV sur l’inverseur

2.4.3. Limitations de l’approche circuit

2.5. Synthèse

Chapitre 3

3.1. Définition de circuits de test dédiés à l’intégration 3D

3.1.1. Caractérisation du TSV

3.1.1.1. Résistance du TSV

3.1.1.2. Capacité du TSV

3.1.2. Impact des structures 3D sur les transistors MOS

3.1.2.1. Impact thermomécanique du TSV sur les transistors

3.1.2.2. Impact électrique du TSV sur les composants

3.1.2.3. Impact électrique du RDL sur les composants

3.1.3. Impact du TSV sur un oscillateur en anneau

3.1.3.1. Définition du circuit de test

3.1.3.2. Impact thermomécanique du TSV sur l’oscillateur en anneau

3.1.3.3. Impact électrique du TSV sur l’oscillateur en anneau

3.1.4. Caractérisation du délai intrinsèque du TSV

3.2. Conception logique : comment passer du 2D au 3D ?

3.2.1. Les différentes étapes de conception d’un circuit

3.2.1.1. Kit de conception

3.2.1.2. Flot de conception

3.2.2. Limitations des outils de conception pour l’intégration 3D

3.2.2.1. Kit de conception

3.2.2.2. Flot de conception

3.2.3. Quelle méthodologie pour la conception 3D ?

3.2.3.1. Circuit 3D homogène

3.2.3.2. Circuit 3D hétérogène

3.3. Implémentation sur démonstrateurs technologiques

3.3.1. Véhicule de test dédié à la moyenne densité

3.3.2. Véhicule de test dédié à la haute densité

3.4. Synthèse

Chapitre 4

4.1. Impact du procédé d’amincissement du silicium

4.1.1. Principe d’amincissement du silicium

4.1.2. Protocole expérimental

4.1.3. Résultats électriques

4.1.3.1. Transistors testés

4.1.3.2. Montée en tension du transistor

4.1.3.3. Variations sur les courants spécifiques

4.2. Impact thermomécanique et effet de proximité du TSV

4.2.1. Impact des procédés d’intégration 3D sur les transistors

4.2.1.1. Considérations générales

4.2.1.2. Comportement des transistors NMOS

4.2.1.3. Comportement des transistors PMOS

4.2.2. Effet de proximité du TSV sur les transistors

4.2.2.1. Comportement des transistors NMOS

4.2.2.2. Comportement des transistors PMOS

4.2.3. Effet de l’orientation de la grille des transistors

4.2.3.1. Comportement des transistors NMOS

4.2.3.2. Comportement des transistors PMOS

4.2.4. Effet de proximité du TSV sur l’oscillateur en anneau

4.2.4.1. Considérations générales

4.2.4.2. Impact sur l’oscillateur en anneau

4.3. Caractérisation du couplage par le substrat

4.3.1. Caractérisation de la technologie 3D moyenne densité

4.3.1.1. Résistance du TSV

4.3.1.2. Capacité du TSV

4.3.2. Bruit substrat

4.3.2.1. Considérations générales

4.3.2.2. Réponse du silicium

4.3.2.3. Effet de la distance de la sonde de mesure

4.3.2.4. Effet de la distance à la masse

4.3.2.5. Effet de l’amplitude de la tension perturbatrice

4.3.2.6. Effet du temps du front de montée

4.3.3. Modèles électriques

4.3.3.1. Fonction de transfert

4.3.3.2. Confrontation du modèle à l’expérience

4.4. Synthèse

Conclusion

Références bibliographiques

Télécharger le rapport complet