Le secteur de la microélectronique est continuellement en évolution. Les attentes du marché et les progrès techniques imposent une réactivité soutenue de la part des industriels, tant sur le plan de l’innovation que sur le plan des temps de développement. La course dictée par la loi de Moore impose l’adoption de technologies de plus en plus avancées et restreint le temps disponible pour les porter à maturation. La conséquence principale est la difficulté grandissante à obtenir des rendements comparables avec ceux obtenus pour les technologies précédentes. En effet, l’avancée technologique accompagnant la réduction des dimensions des transistors pose certaines limitations à l’industrie microélectronique. Cellesci concernent aussi bien le monde de la fabrication, avec l’apparition de limitations physiques jusqu’alors méconnues, que le monde de la conception qui voit ses contraintes se multiplier. Parmi elles, la complexification des règles de conception et l’apparition de règles dites « recommandées » complique grandement le travail des concepteurs. En effet, là où le respect des règles de conception standard assurait la possibilité de réaliser un circuit sur silicium, la variabilité technologique et les chutes de rendement ont fait émerger une nouvelle catégorie de règles de conception, dont le respect facilite le travail de fabrication et augmente le rendement mais augmente la surface des circuits dans la plupart des cas. Les pressions technologiques et industrielles ne s’accommodant pas facilement de ce type de contrainte, cette nouvelle approche de la conception nommée DFM (pour « Design For Manufacturing») peine à s’affirmer comme une référence. En effet, le retour sur investissement de l’adoption d’une méthode de conception de type DFM est une question récurrente chez les principaux groupes industriels. Pourtant, de nombreux exemples montrent que les industriels exploitants des nœuds technologiques très avancés ont adopté une méthode de conception orientée DFM. Il apparaît que les solutions DFM ne se limitent pas uniquement à l’ajout de règles supplémentaires. L’approche DFM passe également par une réorganisation de la méthode de conception dans le but d’améliorer le rendement. Pour ce faire, il est nécessaire de démontrer les bénéfices de l’adoption du DFM et d’accompagner les différentes parties du flot de production face à ce nouveau défi.

Introduction au DFM

Le DFM (pour « Design for Manufacturing ») est adoptée dans ces dernières années comme solution aux limitations inhérentes à la course technologique menée par les différents acteurs du monde de la microélectronique. En réponse à une complexification grandissante des méthodes de conception et de fabrication, cette nouvelle branche entend améliorer les rendements des technologies avancées. Ses principaux buts sont de changer les mentalités et de tenter de pallier la variabilité grandissante des procédés de fabrication par des méthodes de conception tenant compte de ces nouvelles contraintes. Cependant, le bon déroulement de son adoption par l’industrie est dégradé par les contraintes économiques importantes qui régissent ce secteur. La difficulté à chiffrer le retour sur investissement d’un changement de méthode de conception a pour effet la multiplication des interprétations de l’approche DFM, et on assiste à l’apparition de nombreuses ramifications parallèles. Celles-ci permettent de résoudre certains problèmes, mais n’autorisent pas l’anticipation des dérives physiques futures promise par la solution DFM. C’est pourquoi une nouvelle méthode de conception, le DFM², est définie. Elle permet de créer des interactions entre les différents acteurs du processus de développement d’un produit, afin de confronter leurs contraintes pour définir des solutions innovantes dans le but d’améliorer le gain de rendement.

La course à la réduction des dimensions dans le secteur de la microélectronique s’accompagne de limitations jusqu’alors ignorées, car leur impact sur le rendement n’est pas significatif. Les solutions aux difficultés rencontrées ne se limitent pas à la résolution des défis physiques générés par l’avancée technologique, car le facteur de variabilité de la fabrication représente une part de plus en plus conséquente dans les pertes de rendement et est par nature imprévisible. De ce fait, l’espace des solutions s’est recentré autour d’une nouvelle approche de la méthode de conception plus à l’écoute des contraintes de la fabrication : le DFM, qui est présenté en partie I.2. Cependant, les différentes orientations et interprétations données à l’approche DFM ne suffisent pas toujours à adresser de la meilleure manière les défis technologiques. Ainsi, la partie I.3 présente un nouveau concept de méthode de conception, où les mondes de la conception et de la fabrication sont interconnectés autour d’un acteur qui gère les flux d’informations à travers les canaux de communication ainsi créés. Cette méthode de conception innovante est baptisée DFM², et sa définition théorique sert de cadre aux travaux et résultats présentés dans la suite de cette thèse.

Evolution technologique

Les avancées technologiques dans la microélectronique

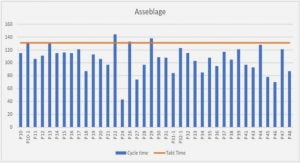

L’industrie du semi-conducteur est un secteur très compétitif et à forte croissance. De ce fait, la survie dans ce secteur passe nécessairement par une réactivité extrême. Les évolutions technologiques de ce domaine ont été prédites par Gordon Moore en 1965 [Moore’65], à l’origine d’un modèle économique qui permit de prévoir notamment la réduction des dimensions des transistors, qui sont les briques élémentaires des circuits microélectroniques, afin d’améliorer à la fois ses caractéristiques électriques et la densité d’intégration de ces composants (Figure 1). Les différentes générations de transistors sont attachées au concept de nœud technologique, déterminé par des contraintes électriques et dimensionnelles qui sont définies par l’ITRS (International Technology Roadmap for Semiconductors) [ITRS’07]. Cette loi, prédisant le doublement du nombre de transistors tous les dix huit mois (réajustement de 1975) dans des circuits de même taille, est aujourd’hui plus ou moins suivie par les industriels en raison du défi technologique majeur que représente une telle évolution. En effet, de nombreuses contraintes physiques apparaissent avec la réduction des dimensions et les processus standard de fabrication et de vérification ne permettent plus de suivre ce modèle d’évolution. Le fonctionnement d’un processus de conception pour des technologies dites « anciennes » autorise la séparation des différentes étapes de la fabrication. Les règles de dessin fournies par le département du développement des technologies se limitent principalement à des contraintes géométriques basiques, comme la taille minimale d’un rectangle ou encore l’espacement minimal entre deux polygones. En effet, pour des nœuds technologiques supérieurs à 350nm, la dimension de la longueur de grille minimale à imprimer par lithographie est supérieure à la longueur d’onde de la lumière utilisée, et de ce fait n’implique pas de spécifications de dessin contraignantes. La maîtrise de la technologie se fait de manière assez rapide et l’arrivée du rendement dans une phase mature n’est pas entravée par des dérives physiques non contrôlées.

Les limitations induites par la progression technologique

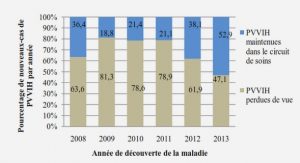

Pour les technologies avancées, il devient de plus en plus difficile de contrôler le processus de fabrication. En effet, la maîtrise des différentes étapes de la réalisation d’un produit se heurte à une variabilité des résultats produits. Celle-ci est inhérente au rapprochement continu des attentes industrielles vers les limites technologiques des procédés de fabrication. Ainsi les paramètres électriques définis lors de la phase de conception d’un composant électronique ne seront pas les mêmes que ceux du composant réalisé sur silicium [Raghavendra’08]. Ce phénomène est appelé variation de fabrication ou « process variation ». Il apparaît à différentes étapes du processus de fabrication, telles que la lithographie, l’implantation ionique ou encore le polissage mécanico-chimique (connu sous le sigle CMP : « Chemical Mechanical Polishing »). Les principaux facteurs de variation de fabrication sont le désalignement de la plaque de silicium lors de la phase de lithographie, la fluctuation aléatoire des dopants (particules introduites dans la structure cristalline d’un matériau semi-conducteur afin de modifier ses paramètres électroniques, comme la conductivité) ou encore des imperfections dans la planéité des différents niveaux. Durant les quarante dernières années, la réduction des dimensions a permis de réduire la taille des circuits, et donc des coûts de fabrication, et d’augmenter la vitesse tout en diminuant la consommation d’énergie des produits. Cependant, ces avantages ont été contrebalancés par l’apparition de nouveaux défis technologiques tels que les courants de fuites, les chutes de tension, la prévision des variations de délai ou encore les variations de géométrie pour les lignes métalliques ou les tailles des transistors (Figure 2) [Buurma’08].

Les coûts des équipements de fabrication adaptés aux nœuds technologiques avancés représentent une part conséquente des investissements des entreprises du fait de leur complexité, nécessaire pour fabriquer des composants approchant la limite atomique. De nombreuses précautions doivent être prises tant au niveau de la conception qu’au niveau de la fabrication des circuits afin d’assurer les rendements imposés par le marché. Les concepteurs de cellules ont besoin de modèles fiables qui prennent en compte tous les effets physiques, y compris ceux découverts récemment. De plus, ils doivent multiplier les vérifications de tous types afin de s’assurer que la marge de fonctionnalité du produit soit incluse dans la marge de variation induite par les procédés de fabrication. La robustesse des circuits est un facteur essentiel, spécialement dans certains domaines d’utilisation comme les secteurs automobile et aérospatial. Le facteur économique est également déterminant dans le développement des nouvelles technologies. Afin d’atteindre un rendement qui rendra la technologie industriellement exploitable, les investigations ne se limitent plus à la maîtrise des caractéristiques basiques de la technologie ou à la validation des nouvelles machines .

Des stratégies doivent être mises en place afin de modéliser les effets physiques découverts récemment et de prédire les variations de fabrication. Cela passe par des analyses théoriques et par le développement de solutions alternatives de fabrication qui permettront de profiter au mieux des possibilités offertes par une nouvelle technologie tout en conservant au maximum la qualité attendue par les clients. Dans de nombreux cas, par exemple pour le développement de cellules analogiques, la robustesse face aux variations de fabrication impose la mise en place d’une méthode de conception sur-contrainte et ne permet donc pas de tirer partie des avantages du nœud technologique considéré. Cette limitation n’est pas acceptable du fait des coûts colossaux engendrés par l’adoption d’une technologie. De nouvelles solutions doivent donc être trouvées afin de maximiser le retour sur investissement tout en préservant la qualité. Cela passe par une méthode de conception qui prend en compte les contraintes technologiques de l’étape de fabrication afin d’optimiser le rendement. On assiste donc à une intensification des interactions entre les deux mondes de la conception et de la fabrication dans le but de relever le défi de la variabilité technologique. Cette association constitue la base de l’approche DFM.

|

Table des matières

Introduction générale

Chapitre I Introduction au DFM

I.1 Introduction

I.2 Historique du DFM

I.2.1 Evolution technologique

I.2.1.1 Les avancées technologiques dans la microélectronique

I.2.1.2 Les limitations induites par la progression technologique

I.2.2 De la nécessité du DFM

I.2.2.1 Les premiers pas du DFM

I.2.2.2 Emergence de deux orientations fondamentales

I.2.2.2.1 DFM géométrique ou DFM électrique ?

I.2.2.2.2 Classification des défauts

I.2.2.2.3 Fusion des deux orientations fondamentales

I.2.2.3 Recadrage des différentes orientations du DFM

I.3 Définition d’une nouvelle méthode de conception

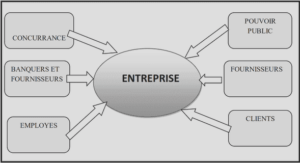

I.3.1 Les interactions de la conception cellules avec les différentes parties du processus de conception

I.3.2 Fusion des deux dimensions dans l’espace DFM²

I.3.2.1 Nécessité de confronter les deux dimensions Conception et Technologie

I.3.2.2 La pierre angulaire de cette interconnexion : la Conception cellule

I.4 Conclusion

Chapitre II Application de la méthode DFM au niveau FEOL

II.1 Introduction

II.2 Introduction de l’impact du DFM sur le FEOL

II.3 Identification des problèmes existants

II.3.1 Les modes de communication entre le monde de la fabrication et le monde de la conception

II.3.2 Problèmes relatifs au procédé de fabrication

II.3.3 Manque d’anticipation sur les phénomènes à prendre en compte

II.4 Mise en place de solutions

II.4.1 Mise en relation de la technologie et de la conception

II.4.1.1 Intensification des interactions entre technologie et conception

II.4.1.2 Définition de structures de test

II.4.2 Définition de nouvelles règles

II.4.2.1 Modification des règles standard

II.4.2.2 Définition de règles DFM

II.4.3 Définition d’une structure de remplissage innovante : la DFM Filler Cell

II.5 Conclusion

Chapitre III Influence des variations de la métallisation sur les performances temporelles des circuits

III.1 Introduction

III.2 Les phénomènes de variation de la métallisation

III.2.1 Impact du CMP sur la fabrication au niveau BEOL d’un point de vue global

III.2.2 Etat de l’art de l’étude de l’impact des dispositifs de remplissage métalliques

III.3 Modélisation de l’impact de la géométrie du motif des dispositifs de remplissage métalliques

III.3.1 Présentation de la méthode Design Of Experiment

III.3.2 Définition des structures de test

III.3.2.1 Structure ROC : cellules standard et leurs interconnexions

III.3.2.2 Structure ROI : Interconnexions pour différents niveaux métalliques

III.3.3 Application de la méthode DOE à l’étude de l’impact de la géométrie des dispositifs de remplissage métalliques

III.4 Exploitation des résultats

III.4.1 Dispersion de l’impact de la géométrie du motif des dispositifs de remplissage métalliques sur le délai des interconnections

III.4.1.1 Présentation des résultats de la structure ROC

III.4.1.2 Présentation des résultats de la structure ROI

III.4.1.3 Relation entre l’impact des dispositifs de remplissage métalliques et la densité

III.4.2 Définition du concept de « Metal Filling Corner »

III.4.2.1 Comparaison des impacts des variations technologiques et des caractéristiques des dispositifs de remplissage métalliques

III.4.2.2 Définition du « Metal Filling Corner »

III.5 Conclusion

Chapitre IV Développement d’un outil en adéquation avec la méthode DFM2 : le DUTY

IV.1 Introduction

IV.2 La place du DUTY au sein du processus de conception industriel

IV.2.1 Motivations du développement

IV.2.2 Un outil dédié a la conception des cellules

IV.3 Fonctionnement du DUTY

IV.3.1 Généralités

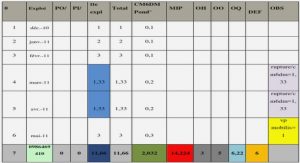

IV.3.2 YAM – Yield Analysis Module

IV.3.3 YEM – Yield Enhancement Module

IV.3.4 DUTY Metric

IV.4 Conclusion

Conclusion générale