Modèle de délai (retard)

Les pannes de délai affectent le comportement temporel d’un circuit. Ils ajoutent un délai excessif le long d’un chemin combinatoire de sorte que les signaux se propagent lentement ou rapidement. Les pannes de délai sont de plus en plus présentes dans les circuits intégrés en raison de la miniaturisation de ces derniers. Ces pannes provoquent un dysfonctionnement du circuit à haute vitesse (Wang, Wu et Wen, 2006). L’effet principal de ces pannes est de ralentir les transitions qui se propagent dans un circuit. Les modèles de délai sont divisés en deux sous catégories : les pannes de délai de chemin (path delay fault) et les pannes de transition. Le modèle de pannes de chemin suppose que le délai additionnel causé par la panne est réparti sur tout le chemin. Ce modèle de pannes est habituellement utilisé pour représenter l’effet des variations du procédé de fabrication et pour tester les chemins les plus critiques. Un circuit est défectueux si le délai de l’un de ces chemins combinatoires excède la limite de délai spécifié (Smith, 1985). Le modèle de pannes de transition, quant à lui, suppose que la panne affecte un seul noeud du circuit, de manière ponctuelle (Waicukauski et al., 1987).

Par exemple, si une panne de délai est identifiée sur un noeud logique, toute transition de signal passant par ce noeud est retardée au-delà de la période d’horloge. Ces pannes sont modélisées comme un retard du temps de montée ou de descente des transitions des signaux au niveau des portes logiques. Selon (Waicukauski et al., 1987), il existe deux types de pannes de transition : la panne de transition lente à monter (STR, slow-to-rise fault) et la panne de transition lente à descendre (STF, slow-to-fall fault). Une panne STR signifie que toute transition de 0 1 sur un noeud ne produit pas un résultat correct lorsque le circuit fonctionne à fréquence nominale. Une panne STF signifie que toute transition de 10 sur un noeud ne produit pas un résultat correct lorsque le circuit fonctionne à fréquence nominale. Ce mémoire traite uniquement les pannes de délais et, plus particulièrement, les pannes de transition. Par conséquent, le test de délai de transition est le type de test utilisé lors de nos expérimentations.

Génération automatique de vecteurs de test (ATPG)

Les vecteurs de test, appelé aussi patrons de test, sont des ensembles de 0 et 1 logiques placés aux broches des entrées primaires d’un CUT. Ils permettent de contrôler les pannes à partir des entrées primaires et de les observer sur les sorties primaires. Lors de l’application des vecteurs de test, les équipements automatiques de test (ATE, Automatic Test Equipment) déterminent s’il existe des pannes de fabrication sur un CUT en comparant les réponses de ses sorties primaires à celles d’un circuit sans panne (fault-free circuit). L’objectif de la génération automatique de vecteurs de test (ATPG, Automatic Test Pattern Generation) est de créer un ensemble de vecteurs de test pour atteindre une couverture de pannes adéquate (Tessent, 2014). La couverture de test (TC) est une mesure pour évaluer l’efficacité de test.

La couverture de test est le pourcentage du nombre de pannes détectées divisé par le nombre total de pannes de circuit (équation 1.1). ?? = 100 ∙ Nombre de pannes détectées par la séquence de test Nombre total de pannes du circuit (1.1) L’ATPG utilise des vecteurs de test déterministes pour détecter autant de pannes que possible avec un effort raisonnablement faible. Il génère des vecteurs de test qui sont destinés à montrer si le système exécute sa fonction spécifiée. Ces vecteurs de test détectent les pannes définies par des modèles de pannes spécifiques. Pour détecter une panne, l’ATPG insère une panne à un noeud dans le CUT. Deux procédures sont appliquées à la panne ciblée : l’activation des pannes et la propagation des pannes. L’activation des pannes impose une valeur logique, au niveau du noeud ciblé, opposé à la valeur de la panne. La panne se propage par la suite à travers les portes logiques, pour atteindre les sorties primaires (Tremblay, 2007).

Conception en vue de test Traditionnellement, le processus du test était considéré uniquement après le processus de conception. Mais avec les flux actuels de conception, ces deux processus sont maintenant combinés. Cette combinaison est appelée conception en vue de test (DFT, Design for Test). De plus, la plupart des circuits numériques sur le marché sont des circuits séquentiels, dans lesquels les signaux internes sont difficiles à observer et à contrôler. En conséquence, il est difficile de les tester. Le but de la DFT est de rendre le test des circuits plus faciles et plus efficaces (Hobeika, 2011). Les techniques de DFT les plus utilisées sont la technique d’autotest (BIST, Built in-it-Self Test) et la technique de test basé sur l’insertion des registres de balayage (SBT, Scan Based Test). L’autotest (BIST) permet aux circuits de se tester eux-mêmes. BIST est capable de générer des vecteurs de test à l’intérieur du CUT et de vérifier la fonctionnalité interne du circuit (Hobeika, 2011).

Le SBT est une technique DFT largement utilisée qui permet de contrôler et d’observer les bascules en ajoutant un mode de balayage au circuit. Lorsque le circuit est en mode de balayage, toutes les bascules forment un ou plusieurs registres à décalage, également appelés chaînes de balayage.

Ce processus réduit le cout du test en transformant un circuit séquentiel en un circuit combinatoire à des fins de test. La figure 1.2 illustre une structure DFT avant et après l’ajout des circuits de balayage. Le SBT consiste à insérer des bascules de balayage à la place des bascules présentes sur le design (un multiplexeur et une bascule forment une bascule de balayage). Le signal (SE, Scan Enable) détermine si le système est en mode normal (SE = 0) ou mode de balayage (SE = 1). Les vecteurs de test peuvent être décalés vers l’intérieur (à travers sc_in) ou vers l’extérieur (à travers sc_out) à travers des chaines de balayage, tandis que les autres entrées (A,B,C) sont encore fournies par des entrées primaires (Hobeika, 2011). De cette façon, chaque entrée peut être contrôlée bit par bit, et chaque sortie peut être observée plus clairement.

Par conséquent, le circuit séquentiel avec la technique SBT a une meilleure contrôlabilité et une meilleure observabilité. Les deux derniers termes peuvent affecter la qualité de test (Hobeika, 2011). La contrôlabilité est une mesure de la facilité d’imposer au niveau logique d’un noeud du circuit un état logique donné (0 ou 1). L’observabilité est une mesure de la facilité d’observer le niveau logique d’un noeud aux broches de sortie du CUT.

Revue de littérature

Les tests de balayage à vitesse nominale (SBAST) sont considérés comme la méthode de test de délai la plus dominante des tests structurels (Moghaddam et al., 2010). Ce type de test vient avec certains inconvénients comme le bruit de tension d’alimentation (PSN, Power Supply Noise) produit pendant le mode test et qui diffère de celui induit pendant le mode fonctionnel. La cause de cette différence est l’augmentation du niveau d’activité de commutation dans le circuit d’un facteur de 3 à 4 pendant les tests SBAST (Arabi, Saleh et Meng, 2007). L’augmentation de la fréquence et la diminution des durées de transition (montée ou descente) des CI provoquent plus d’activité de commutation dans un petit intervalle de temps. Elle entraîne une augmentation de la densité de courant et une chute de tension. Le PSN peut être introduit par des paramètres inductifs ou résistifs, ou par une combinaison des deux.

De plus, le schème des techniques SBAST peut aussi conduire à cette différence. En effet, l’horloge de test est composée de deux cycles ; un cycle de décalage fonctionnant à des vitesses lentes suivi par deux impulsions rapides (deuxième cycle) pour lancer et capturer la transition. Le PSN a été traité par plusieurs chercheurs. Leurs travaux portaient sur la chute de tension d’alimentation. L’effet principal de cette chute est la modification de temps de propagation des signaux. Elle peut conduire au phénomène d’étirement d’horloge de telle sorte que le CUT apparait plus rapide (Rearick, 2001). Les états de transition et les chutes de tension lors du mode test conduisent à des dégradations des fréquences d’horloges. Ces dégradations sont dues à l’augmentation de l’activité de circuit ainsi qu’à la consommation d’énergie (Rearick, 2001). L’une des options proposées dans la littérature pour réduire la chute de tension est d’augmenter la longueur de la séquence de lancement ou de capture et d’appliquer les premiers cycles de capture à des vitesses plus lentes. Les techniques les plus pertinentes proposées sont : SeBoS (Lin et al., 2013; Pant et Zelman, 2009), BurstMode (Nadeau-Dostie, Takeshita et Cote, 2008) et PKLPG (Zhang et Walker, 2013).

|

Table des matières

INTRODUCTION

CHAPITRE 1 NOTIONS DE BASE ET REVUE DE LITTÉRATURE

1.1 Introduction

1.2 Notions de base sur le test des circuits intégrés

1.2.1 Test fonctionnel

1.2.2 Test structurel

1.2.3 Modèles de pannes

1.2.4 Génération automatique de vecteurs de test (ATPG)

1.2.5 Conception en vue de test

1.2.6 Test de transition avec insertion de registres de balayages

1.2.7 Launch on Shift

1.2.8 Launch on Capture

1.3 Circuits intégrés 3D

1.4 Revue de littérature

1.4.1 Sequential Broad Side (SeBoS)

1.4.2 BurstMode

1.4.3 Pseudo-functional K Longest Path per Gate (PKLPG)

1.5 Conclusion

CHAPITRE 2 MODÈLES DE SIMULATION ET EXPÉRIMENTATIONS PRÉLIMINAIRES

2.1 Introduction

2.2 Modèle du réseau de distribution d’alimentation (PDN)

2.2.1 Réseau de distribution d’alimentation utilisé

2.2.2 Modèle équivalent du PDN complet

2.3 Description des simulations HSPICE

2.3.1 Circuit de mesure de délai

2.3.2 Principe de fonctionnement du circuit de mesure de délai

2.4 Simulations préliminaires

2.4.1 Cas d’étude

2.4.2 Simulation AC

2.4.3 Mesure de délai en mode fonctionnel

2.4.4 Interprétation des résultats

2.5 Conclusion

CHAPITRE 3 RÉSULTATS DE SIMULATION EN MODE TEST POUR LES PRINCIPALES TECHNIQUES DE TEST SBAST EXISTANTES

3.1 Introduction

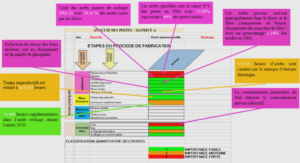

3.2 Métrique de test

3.3 Résultats de simulation pour les techniques Launch on Capture et Launch on Shift

3.4 Résultats de simulation pour la technique Sequential Broadside Side (SeBoS)

3.5 Résultats de simulation pour la technique BurstMode

3.6 Résultats de simulation pour la technique Pseudo-functional K Longest Paths per Gate (PKLPG)

3.7 Conclusion

CHAPITRE 4 NOUVELLE TECHNIQUE DE TEST PROPOSÉE ET COMPARAISON AVEC LES TECHNIQUES EXISTANTES

4.1 Introduction

4.2 Nouvelle technique de test OCAS

4.3 Résultats de simulation

4.4 Comparaison et analyse des résultats avec les techniques existantes

4.5 Conclusion

CHAPITRE 5 GÉNÉRATION AUTOMATIQUE DE VECTEURS DE TEST

5.1 Introduction

5.2 Conception en vue du test et génération automatique de vecteurs de test

5.3 Génération automatique de vecteurs de test pour les techniques LOC, LOS et BurstMode

5.4 Procédure de test développée pour SeBoS et OCAS

5.4.1 Procédure de test développée pour SeBoS

5.4.2 Procédure de test développée pour OCAS

5.5 Résultats de simulation des différentes techniques de test

5.6 Conclusion

CONCLUSION

RECOMMANDATIONS

ANNEXE I MODÈLE ORIGINAL DU CIRCUIT ÉQUIVALENT CI-3D

ANNEXE II RÉSULTATS DE MESURE DE DÉLAI DE PROPAGATION DES PRINCIPALES TECHNIQUES DE de SBAST

LISTE DE RÉFÉRENCES BIBLIOGRAPHIQUES

![]() Télécharger le rapport complet

Télécharger le rapport complet