De nos jours, le Traitement Numérique de Signal ne cesse d’évoluer pour répondre aux exigences actuelles de plusieurs domaines tels que les télécommunications qui ont marqué une avancée impressionnante. De plus, les algorithmes de Traitement Numérique de Signal figurent dans différentes applications telles que le domaine médical, l’aéronautique, le multimédia et l’électronique grand public. L’évolution rapide de la technologie des semi-conducteurs a conduit à d’énormes innovations dans le domaine de conception des produits électroniques pour implanter des applications de plus en plus complexes. Les équipements électroniques disponibles sur les marchés d’aujourd’hui sont caractérisés par une concurrence entre les grandes entreprises d’électronique pour les rendre plus efficaces et multifonctionnels. Cela s’est manifesté par l’évolution rapide des réseaux radio mobile particulièrement avec la quatrième génération (ou 4G). Par conséquent, les équipements de ces normes intègrent différentes technologies de communication numérique (WIFI, Bluetooth, GPS,…) qui cohabitent ensemble au sein du même équipement avec plusieurs applications fondées sur des algorithmes de traitement numérique de signal. En conséquence, ces grandes firmes d’électronique se trouvent face à un cycle continu de conception et de livraison des produits. A chaque itération de ce cycle, les concepteurs ont besoin de travailler avec une très haute complexité technologique en visant en même temps à fournir davantage de valeur ajoutée au consommateur dans les meilleurs délais.

Les smart-phones actuels avec la 4G sont un bon exemple d’un équipement électronique de télécommunication, de traitement de signal et de semi-conducteurs et qui nécessite de très hautes capacités de calcul pour accomplir les diverses applications qui sont embarquées dans ces équipement et assurer les performances demandées pour la voix et le trafic des données. De plus, ils sont équipés de plusieurs outils de multimédia tels que les caméras par exemple pour enregistrer des vidéos et jouer de la musique en temps réel. Tout cela est conçu sous les contraintes d’énergie et de temps. L’exemple des smart-phones peut être généralisé pour la conception des équipements électroniques modernes afin de à minimiser le coût du système en termes de surface de silicium, le profit de la consommation de puissance et le temps d’exécution sous contrainte de performances améliorées en termes de précision de calcul et du temps de réponse. Par conséquent, ces objectifs représentent « pour les concepteurs » un compromis entre les performances et le coût. En conséquence, il est très important de faire les choix adéquats à chaque étape de conception afin d’assurer les meilleurs performances possibles du système global. De plus, le temps de mise sur le marché (Time-to-market) de ces produits doit être réduit. Pour cette raison, la conception et le développement de ces applications nécessitent l’utilisation des outils de haut-niveau qui interviennent dans toutes les étapes du cycle de développement des applications de traitement numérique de signal et de communication numérique. Le rôle de ces outils est de fournir aux concepteurs des facilités d’implantation pour choisir la meilleure architecture à implémenter en permettant de passer d’un haut niveau d’abstraction à une caractérisation bas niveau. Également, le choix des opérateurs utilisés pour implémenter ces algorithmes influence très largement le compromis coût/performance. Les opérateurs en arithmétique virgule flottante et en arithmétique virgule fixe sont les deux choix les plus courants pour l’implémentation de toutes les opérations arithmétiques. Il convient de préciser que l’implémentation en arithmétique virgule fixe possède l’avantage d’une consommation de puissance inférieure à celle en arithmétique virgule flottante, mais aussi elle est marquée par une latence plus courte et des surfaces significativement plus petites. Par conséquent l’arithmétique en virgule fixe est un choix populaire pour l’implémentation des algorithmes de traitement numérique de signal (TNS) qui possèdent des paramètres de performances rigoureux à achever et qui demandent des puissances de calcul élevées.

Arithmétique virgule fixe

Cette partie est consacrée à la présentation des spécifications de l’arithmétique virgule fixe ainsi que des différentes techniques existantes pour évaluer la précision des systèmes virgule fixe. En effet, les arithmétiques virgule fixe et virgule flottante sont les arithmétiques binaires de données les plus utilisées sur les plates-formes informatiques modernes. La première partie de ce chapitre est consacrée à la description des différents types de codage. Les circuits en arithmétique virgule fixe ont existé depuis les premiers ordinateurs électroniques et les calculateurs. Choisir le format approprié en arithmétique virgule fixe a toujours été un sujet de préoccupation. Auparavant, ce choix était influencé principalement par des considérations liées à la puissance de calcul des processeurs mais également par des considérations sur la mémoire nécessaire en raison de la latence et du coût de celle-ci. La plupart des algorithmes numériques complexes devaient compter sur des tables précalculées durant les calculs. Aujourd’hui, la définition du format en virgule fixe d’un nombre est impactée par des considérations telles que la surface de silicium, le temps d’exécution et la consommation totale d’énergie du dispositif électronique. L’arithmétique virgule fixe répond bien à ces exigences par rapport à l’arithmétique flottante. Par contre, l’utilisation de l’arithmétique virgule fixe engendre la génération de bruits de quantification causés par les débordements lors du changement de format. Ces bruits, présentés dans la deuxième partie de ce chapitre, se propagent ensuite au sein du système global et conduisent à la modification de la qualité de l’application. Par conséquent, l’évaluation de la précision est une étape primordiale lors de la conversion de format flottant au format fixe afin de garantir l’intégrité de l’application. Il est donc important de disposer de méthodologies d’évaluation de cette précision en arithmétique virgule fixe. Ce point fera l’objet de la troisième partie de ce chapitre. Il existe deux familles d’approches : l’approche d’évaluation par simulation qui est basée sur des simulations virgule fixe de l’application et l’approche d’évaluation analytique qui consiste à trouver des modèles analytiques basés sur des métriques. Nous menons ci-après une analyse des points forts de chacune de ces deux approches ce qui nous permettra de sélectionner l’approche retenue dans le cadre de ce travail.

Les différents types de formats de données

Le choix d’une représentation binaire relève d’une problématique qui concerne toute plateforme numérique actuelle. Faire un choix d’une représentation ou d’une arithmétique représente une étape primordiale dans le développement d’une application numérique. Les arithmétiques virgule fixe et virgule flottante sont généralement utilisées dans un but de stockage ou de calcul. En général, les algorithmes de traitement numérique de signal demandent des capacités de calcul intensif. Par conséquent, le choix du bon format de représentation des nombres joue un rôle crucial pour une implémentation efficace de n’importe quel algorithme de traitement numérique de signal. Dans le calcul numérique, le système de numération spécifie la méthode selon laquelle les nombres sont représentés comme étant une séquence de chiffres binaires et il spécifie également les règles pour effectuer les opérations arithmétiques (ex. addition, multiplication etc.) entre ces nombres. Dans la plupart du temps, les calculs scientifiques donnent seulement une approximation de la valeur exacte qui serait obtenue avec une précision infinie. Ceci est une conséquence du nombre limité de bits utilisés dans le système de numération. Quel que soit l’arithmétique virgule fixe ou l’arithmétique virgule flottante utilisée, seulement un nombre fini de bits est utilisé pour la représentation des nombres réels.

La précision limitée des standards de codage peut être évaluée selon deux perspectives différentes. La première concerne la précision des calculs déterminée par l’étape de quantification du système de numération (la distance entre deux nombres). Le second aspect est relatif à la variation de la dynamique maximale permise par la représentation. Cette variation de la dynamique d’un système de numération est donnée par l’ensemble des valeurs possibles qui peuvent être représentées.

Généralement, les algorithmes pour les systèmes embarqués sont développés en utilisant l’arithmétique virgule flottante afin d’éviter les problèmes liés à la longueur finie d’un mot de code. Ce processus valide l’intégrité de l’algorithme et vérifie si l’algorithme proposé répond bien au cahier des charges. Même si l’erreur inhérente à l’exactitude de calcul existe toujours, elle demeure faible par rapport à celle obtenue par l’arithmétique en virgule fixe. Par conséquent, le calcul en virgule flottante garantit une précision et une variation de dynamique suffisantes dans la plupart des cas. Néanmoins, la plupart des implémentations VLSI utilisent l’arithmétique en virgule fixe pour réduire la surface et la consommation d’énergie et obtenir un matériel rentable. En contrepartie, une dégradation de la précision des calculs est produite en raison du nombre limité de bits utilisés dans la représentation des données. En effet, l’utilisation du codage en virgule fixe introduit des bruits de quantification lors de l’élimination de bits à travers les opérations de saturation (arrondi) et troncature. En outre, cela conduit à l’apparition de débordements à chaque fois que la longueur du mot de code de la partie entière est insuffisante pour représenter l’ensemble de la variation de la dynamique.

Notation Signe – Valeur Absolue (SVA)

La notation en numération simple d’un nombre signé correspond à la représentation de la valeur absolue de ce nombre en numération simple de position en ajoutant un symbole spécifiant le signe du nombre à représenter. L’inconvénient de cette représentation se manifeste par les opérations mathématiques effectuées sur des nombres respectant cette notation. En effet, à titre d’exemple, l’addition de deux nombres nécessite l’utilisation de deux algorithmes : un algorithme d’addition si les deux nombres possèdent le même signe et un algorithme de soustraction dans le cas contraire.

Présentation en complément à la base

Afin d’éviter le problème de prise en compte du signe des opérandes présent pour la notation SVA, le système de numération des entiers, en complément à la base B a été créé. Par conséquent dans le cas où B est une base paire, l’entier p = (aN−1…a2a1a0)B¯ est représenté de la façon suivante :

– Si 0 ≤ p ≤ BN /2 − 1, la représentation est celle de l’équation (1.2) :

ESAB(aN−1…a2a1a0) = p.

– Si −BN /2 ≤ p ≤ −1, le codage est réalisé selon l’expression suivante :

ESAB(aN−1…a2a1a0) = BN + p.

Par conséquent, grâce à cette notation, on utilise un seul algorithme d’addition modulo BN pour réaliser l’addition de tous les entiers compris entre −BN /2 et BN /2. Si le signe du résultat de l’addition est différent de celui des opérandes, il en résulte un dépassement de capacité. Dans le cas où B = 2, cette notation est connue sous le nom de notation à complément à deux (CA2).

Le format virgule fixe

Soit x un réel écrit sous la forme x = pK avec p un entier codé selon l’une des représentations décrites précédemment où K est appelé le facteur d’échelle. Ce facteur d’échelle est une puissance de la base B préalablement fixée : K = Bn . La position de la virgule peut alors être référencée par un entier n relativement au bit de poids faible (Least Significant Bit ou LSB) ou par un entier m relativement au bit de poids fort (Most Significant Bit ou MSB).

|

Table des matières

Introduction

Contexte de l’étude

Problématique de la thèse

Contributions

Organisation de la thèse

1 Arithmétique virgule fixe

1.1 Les différents types de formats de données

1.1.1 Représentation des nombres entiers

1.1.2 Le format virgule fixe

1.1.3 Le format virgule flottante

1.1.4 Comparaison arithmétiques virgule flottante et virgule fixe

1.2 Modélisation du bruit de quantification

1.2.1 Processus de quantification

1.2.2 Signal à amplitude continue

1.2.3 Signal à amplitude discrète

1.2.4 Conclusion

1.3 Évaluation de la précision

1.3.1 Les métriques de précision

1.3.2 Les méthodes d’évaluation de la précision par simulation

1.3.3 Les approches analytiques de l’évaluation de la précision

1.3.4 Autres effets de la quantification

1.3.5 Bilan des deux approches

1.3.6 Les approches hybrides

1.4 Conclusion

2 Évaluation analytique de la précision des algorithmes de décodage sphérique

2.1 Les opérateurs lisses et non lisses

2.1.1 Introduction

2.1.2 Les opérateurs lisses et non-lisses

2.1.3 La quantification d’un opérateur non lisse

2.1.4 Identification d’un opérateur non lisse

2.2 Modèle analytique pour l’opérateur de décision

2.2.1 Modélisation de l’opérateur de décision

2.2.2 La réponse à la perturbation

2.2.3 La probabilité d’erreur de décision

2.3 Cascade d’opérateurs de décision

2.3.1 Propagation de l’erreur de quantification

2.3.2 Détermination analytique de la probabilité d’erreur en sortie de la cascade

2.3.3 Analyse de la complexité du modèle analytique

2.4 Application du modèle à l’algorithme SSFE

2.4.1 Modèle du système MIMO

2.4.2 Présentation de l’algorithme

2.4.3 Application du modèle analytique proposé

2.4.4 Première approche

2.5 Conclusion

3 Évaluation de la précision de l’itération d’opérateur de décision

3.1 Problématique

3.1.1 Caractéristiques de la propagation du bruit

3.2 Modèle analytique proposé

3.2.1 Approche basée sur la résolution d’un système non linéaire à l’aide de l’algorithme de Newton-Raphson

3.2.2 Borne supérieure de la probabilité d’erreur

3.3 Évaluation de la précision de l’égaliseur à retour de décision

3.3.1 Présentation de l’algorithme DFE

3.3.2 Résultat pour le cas non adaptatif

3.3.3 Solution proposée pour le cas adaptatif

3.4 Optimisation du format virgule fixe pour l’implémentation matérielle

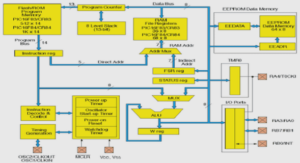

3.4.1 Présentation de l’architecture

3.4.2 Implémentation sur FPGA

3.4.3 Les contraintes du choix du format de représentation

3.5 Conclusion

4 Évaluation de la précision du turbo décodage

4.1 L’optimisation de la largeur des données en virgule fixe

4.1.1 Variantes du problème

4.1.2 Variable d’optimisation

4.1.3 Solution au problème d’optimisation de la longueur du mot de code

4.2 Optimisation du turbo décodage

4.2.1 Présentation de l’algorithme

4.2.2 Modélisation et design en virgule fixe

4.2.3 Réduction de la taille de mémoire

4.2.4 Performance du turbo décodeur

4.3 Optimisation du décodage LDPC

4.3.1 Modélisation et design en virgule fixe d’un décodeur LDPC

4.3.2 Réduction de la taille de mémoire

4.3.3 Performance en virgule fixe du décodeur LDPC

4.4 Positionnement des travaux par rapport à la littérature

4.5 Conclusion

Conclusion