Télécharger le fichier pdf d’un mémoire de fin d’études

Description de la Couche Physique (PHY) dans la bande ISM 2,4GHz

Le standard IEEE 802.15.4 spécifie la couche physique (PHY) dans les bandes ISM 868MHz, 915MHz et 2.4GHz avec un débit respectif de 20, 50 et 250kbits/s. Le nombre de canaux disponible étant plus important dans la bande 2.4GHz, c’est elle qui est la plus utilisée. Ce travail de recherche s’est donc concentré sur cette bande de fréquence dont les bornes basses et hautes sont respectivement 2,405GHz et 2,48GHz.

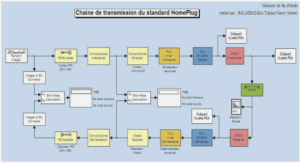

Un codage des bits par étalement de spectre est utilisé avant la modulation sur fréquence porteuse [13]. Cette technique d’étalement permet de faire fonctionner la transmission avec un rapport signal à bruit (SNR) plus important que ceux des systèmes à bande étroite (Figure 12), au prix d’une bande passante plus importante. La technique utilisée par le standard 802.15.4 consiste à faire correspondre à chaque groupe de 4 bits un code d’étalement de 32 bits (appelés chips dans le cas d’un codage par étalement de spectre) fixé par le standard. Le débit brut dans l’air étant de 250kbit/s, le débit chip obtenu est de 2Mchips/s. Les chips sont ensuite modulés sur la fréquence porteuse à l’aide d’une O‐QPSK pour Offset Quaternary Phase Shift Keying [14] où les chips paires sont envoyés sur la voie I et les chips impaires sur la voie Q, chaque chip étant répété deux fois sur chaque voie (Figure 8). Un exemple de cette modulation est présenté sur la Figure 9. Il montre les signaux I et Q après modulation pour une trame de chips composée de 110110001 ainsi que le diagramme de phase correspondant.

La modulation OQPSK est équivalente à une modulation MSK pour Minimum Shift Keying [15] dont l’indice de modulation serait égal à 0.5. C’est une modulation à enveloppe constante, facilitant ainsi la conception de la chaîne de transmission ainsi que celle de la chaîne de réception, en réduisant notamment les contraintes de linéarité. En effet, en l’absence de modulation d’amplitude, le signal est en mesure de supporter des phénomènes de compression tant que ces phénomènes n’introduisent pas d’erreur dans la modulation de phase.

Une modélisation système de cette modulation a été réalisée avec le logiciel ADS. Le spectre obtenu présente un lobe principal occupant une bande de fréquence de 3MHz (Figure 10). Les « trous » dans le spectre sont dus au fait que seulement 16 codes orthogonaux de 32 chips sont utilisés.

Dans la bande disponible entre 2.405GHz et 2.48GHz, le standard ZigBee défini donc 16 canaux avec un espacement inter‐canal de 5MHz (Figure 11). Ils sont numérotés de 11 à 26, les dix premiers correspondants aux canaux disponibles dans les bandes de fréquence 868 et 915 MHz.

Enfin précisons que ce standard fonctionne en mode « half‐duplex » pour lequel il ne peut y avoir simultanément réception et transmission de données, contrairement à ce qui est réalisé dans le mode « full‐duplex».

NOTION DE COEXISTENCE DANS LA BANDE ISM 2.4GHZ

Le standard ZigBee se trouvant dans une bande ISM (Industriel, Scientifique, et Médical) il est soumis au problème de coexistence. Dans ce paragraphe, nous allons introduire ce problème, en présentant dans une première partie les différents standards présents dans la bande ISM 2.4GHz avant d’étudier plus en détail dans une deuxième partie le cas du standard WLAN qui est de loin le plus contraignant.

Présentation du problème

La bande ISM 2.4GHz est une bande libre, non soumise à des réglementations nationales et qui peuvent être utilisées librement (gratuitement et sans autorisation) pour des applications industrielles, scientifiques et médicales. Les seules obligations à observer sont la puissance d’émission et les excursions en fréquence, ou la perturbation des fréquences voisines. En contre ‐ partie et par voie de conséquence elle est assez encombrée [17]. Les principaux standards présents dans cette bande sont les suivants :

• IEEE 802.11b : WLAN

• IEEE 802.15.1 : Bluetooth

• IEEE 802.15.3 : WPAN haut débit.

Le TABLEAU IV résume pour chacun d’entre eux, les principales caractéristiques affectant la coexistence, en incluant le standard IEEE 802.15.4.

ETAT DE L’ART DES SOLUTIONS ZIGBEE ET DEFINITION DU CADRE ET DES SPECIFICATIONS DU TRAVAIL DE RECHERCHE

Comme nous l’avons vu dans le paragraphe 3.3, le standard IEEE 802.15.4 possède des spécifications assez relâchées. Pour avoir une idée plus précise des spécifications à viser pour un futur produit, il apparait plus intéressant de faire l’état de l’art des circuits compatibles ZigBee déjà existants. Dans un premier temps nous présenterons les caractéristiques importantes d’un circuit ZigBee. Ce travail nous permettra finalement de fixer les bornes de l’étude et les spécifications à tenir.

Présentation d’un circuit compatible ZigBee :

Pour être compatible ZigBee, un nœud doit posséder une interface de communication radio, un microcontrôleur et de la mémoire [19]. Avec l’avancé des technologies CMOS, il devient maintenant possible d’intégrer toutes ces parties sur une seule puce sous la forme d’une puce multifonction. Outre son faible coût, la principale caractéristique de ce système est de pouvoir fonctionner en étant alimenté sur une simple pile pendant une durée supérieure à dix ans. Ce point constitue la principale différence avec les systèmes standards de communications sans fils (WLAN, Bluetooth,..) qui eux sont prévus pour fonctionner sur batterie rechargeable. La consommation de puissance en mode de fonctionnement doit donc être la plus faible possible, surtout en mode de réception, mode qui est actif beaucoup plus souvent que celui d’émission (le canal nécessitant une écoute fréquente). Cependant, le rapport cyclique d’utilisation effective du circuit restant très faible, la consommation de puissance en mode « stand by » est toute aussi importante. Pour donner un ordre de grandeur, un circuit ZigBee complet doit consommer moins de 1µA en mode de veille. Cela nécessite des courants de fuite très faibles et par conséquent ce paramètre conditionne largement le choix de la technologie de réalisation. Pour satisfaire les particularités et les contraintes de ce nouveau 22 standard, de nouvelles techniques plus innovantes et plus risquées doivent être utilisées tant au niveau de la couche réseau, qu’au niveau de la couche physique, notamment pour l’interface de radiocommunication. La conception de cette dernière ayant constitué le but de ce travail de recherche, nous focaliserons la suite de nôtre exposé sur cette fonctionnalité.

Etat de l’art des solutions ZigBee

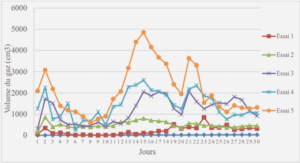

Le standard ZigBee étant relativement récent, peu de produits et de travaux de recherche complets étaient référencés lors du début du travail de recherche. D’ailleurs, c’est toujours le cas. Le TABLEAU VI fait la synthèse de ces circuits, en résumant les principales caractéristiques de leur interface radio. Les performances atteintes sont déjà bien supérieures à celles fixées par la norme IEEE 802.15.4. Par exemple la sensibilité est d’environ 10dB meilleure. Par contre les produits présentés dans ce tableau sont les premiers compatibles ZigBee et leur consommation en courant n’est pas encore bien optimisée et reste trop importante.

Définition du cadre et des spécifications fixées pour le travail de recherche

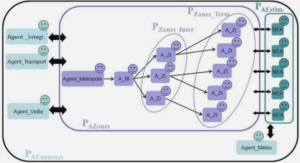

L’étude de l’architecture et la conception de la totalité de la partie radio n’étant pas envisageable, le travail de recherche s’est donc concentré sur la partie réception RF, la plus exigeante et la plus contraignante, notamment en terme de consommation. Cependant, avec les nouvelles architectures de réception CMOS à faible tension d’alimentation, il n’est pas possible de valider des solutions RF sans prendre en compte le premier étage de gain après le mélangeur (PMA pour Post Mixer Amplifier). En effet, d’une part le gain disponible à son entrée restant faible, sa contribution en bruit n’est pas négligeable, et d’autre part, son impédance d’entrée influe beaucoup sur le 23 fonctionnement de la partie RF, comme nous le verrons par la suite. Par contre en sortie de cet étage d’amplification, le gain de la chaîne devient suffisant pour masquer le bruit des étages suivants. L’étude s’est donc concentrée sur les fonctions présentes depuis l’entrée du récepteur (hors antenne) jusqu’à l’amplificateur post mélangeur (PMA). Ce dernier réalise aussi un premier filtrage en bande de base (filtrage du 1er ordre).

Les points essentiels retenus pour l’optimisation de la nouvelle chaîne de réception sont dans l’ordre d’importance : la réduction de coût, la réduction de puissance et l’obtention de performances identiques, voire supérieures, à l’état de l’art. La réduction du coût implique une limitation du nombre des composants externes (filtres, balun, inductances,…) et une réduction de la surface de silicium nécessaire à l’intégration de la puce. Une attention particulière a été portée sur la robustesse aux interféreurs IEEE 802.11b (WLAN), dont la coexistence avec le ZigBee a été présentée au paragraphe 4. Nous avons ainsi pu fixer les spécifications à atteindre pour la tête RF du récepteur. Elles sont résumées dans la TABLEAU VII.

Présentation de la technologie CMOS 90nm

La technologie CMOS de 90nm de longueurs de grilles développée par STMicroelectronics [23], dispose de deux options. Une l’option « low power (LP) » d’épaisseur d’oxyde de grille égale à 21Å, fonctionnant sous une tension typique de 1.2V, et une option « general purpose (GP )» dont l’oxyde de grille est plus fin et fonctionnant sous une tension de 1V. L’option GP apparaît plus adaptée à la réalisation de circuits purement numériques. Elle dispose, en effet, de transistors plus rapides mais avec des courants de fuite trop élevés. L’option LP correspond mieux aux circuits analogiques et mixtes. C’est cette dernière qui a donc été retenue. En utilisant cette option, les transistors MOS ont la possibilité d’être alimenté en « sur tension ». Nous avons donc choisi, pour faciliter la conception, d’utiliser cette possibilité en alimentant tous les blocs avec une tension d’alimentation de 1.35V. La fonctionnalité et les performances du circuit devant être garanties avec une variation de ±10% de la valeur de cette tension.

Niveaux métalliques

Comme toutes les filières silicium, cette technologie intègre un nombre important de niveaux métalliques. Ici, nous disposons de sept niveaux réalisés à l’aide d’un alliage à base de cuivre. Les deux niveaux de métallisation supérieurs sont de forte épaisseur et offre ainsi une faible résistivité. Leur éloignement limite également le couplage avec le substrat. L’option retenue intègre un niveau supplémentaire appelé « AluCap » (Figure 18). Les niveaux métalliques supérieurs ayant les plus faibles pertes, ils sont préférentiellement utilisés pour la réalisation des inductances.

Transistors MOS

Les transistors MOS disponibles en technologie CMOS 90nm, ont une longueur minimale de grille de 0.1µm. Ils sont de deux types : le transistor SVT (standard VTH) et le transistor HVT (High VTH). Comme son nom l’indique, le transistor HVT est caractérisé par une tension de seuil (VTH) plus élevée. Le TABLEAU VIII résume les principales caractéristiques de ces deux transistors, dans le cas de la technologie typique et pour des transistors de dimension W=1µm et L=0.1µm.

Les notations et conventions utilisées pour le transistor ainsi que ses grandeurs de commande sont présentées sur la Figure 19.

Le transistor HVT possède une valeur de fréquence de transition (FT) plus faible. Cependant les courants de fuite qu’il présente sont aussi plus faibles. Il apparait donc bien adapté à la réalisation des circuits digitaux demandant peu de vitesse. Le transistor SVT, dont la tension de seuil est de plus faible valeur, convient mieux à la réalisation des fonctions RF et analogiques fonctionnant sous faible 26 tension d’alimentation. Pour notre étude, le transistor SVT a donc été utilisé dans toutes les fonctions analogiques principales tandis que le transistor HVT est implémenté uniquement dans des circuits de polarisation.

Récepteur à conversion directe

Comme nous venons de le voire, les principaux obstacles à l’utilisation de la conversion hétérodyne sont : son très faible niveau d’intégration, son coût et sa consommation de puissance importante. Considérons maintenant la structure à conversion directe, encore appelée structure homodyne [2] [3]. En mettant en œuvre une fréquence de l’oscillateur local égale à celle de la fréquence porteuse RF, la fréquence intermédiaire devient alors nulle. La complexité du filtrage nécessaire à la sélection du canal est dans ces conditions bien réduite. Cependant, la portion du canal translatée dans les fréquences négatives devient l’image de l’autre partie du canal qui est elle translatée dans les fréquences positives. Un traitement complexe est nécessaire pour reconstituer le signal. Sans ce traitement, il y aurait repliement des fréquences négatives sur les fréquences positives. L’architecture utilisant une telle conversion est décrite sur la Figure 2.

En raison de la valeur nulle de la fréquence intermédiaire, la sélection du canal peut être réalisée par un unique et simple filtre passe bas. De plus, cette structure n’utilise qu’un seul oscillateur local et la réjection d’image entre le LNA et le mélangeur n’est plus nécessaire, ce qui permet encore la suppression d’un filtre. De ce qui précède, nous pouvons conclure que cette structure est beaucoup plus simple que celle de l’architecture hétérodyne et qu’elle possède un très fort niveau d’intégration, en ne nécessitant que peu de composants externes. De plus contrairement à l’architecture hétérodyne, elle peut être très large bande.

|

Table des matières

INTRODUCTION GENERALE

CHAPITRE I : INTRODUCTION AUX RESEAUX DE CAPTEURS, PRESENTATION DU STANDARD ZIGBEE ET DEFINITION DE L’AXE DE L’ETUDE

1 INTRODUCTION :

2 PRESENTATION DES RESEAUX DE CAPTEURS (WSN)

2.1 Introduction:

2.2 Applications :

2.3 Couche Réseau et Notion d’auto organisation:

2.4 Couche de liaison:

2.5 Conclusion:

3 PRESENTATION DES STANDARDS ZIGBEE ET IEEE 802.15.4

3.1 Introduction :

3.2 Description de la Couche Physique (PHY) dans la bande ISM 2,4GHz.

3.3 Spécifications de la couche PHY 802.15.4

3.4 Conclusion

4 NOTION DE COEXISTENCE DANS LA BANDE ISM 2.4GHZ

4.1 Présentation du problème :

4.2 Etude de la coexistence avec le standard IEEE 802.11b :

4.3 Bilan

5 ETAT DE L’ART DES SOLUTIONS ZIGBEE ET DEFINITION DU CADRE ET DES SPECIFICATIONS DU TRAVAIL DE RECHERCHE

5.1 Présentation d’un circuit compatible ZigBee :

5.2 Etat de l’art des solutions ZigBee :

5.3 Définition du cadre et des spécifications fixées pour le travail de recherche:

6 CHOIX ET PRESENTATION DE LA TECHNOLOGIE

6.1 Choix de la technologie :

6.2 Présentation de la technologie CMOS 90nm

6.2.1 Niveaux métalliques :

6.2.2 Transistors MOS :

6.2.3 Composants passifs :

7 CONCLUSION

BIBLIOGRAPHIE

CHAPITRE II : ETUDE ET CHOIX DE L’ARCHITECTURE DE RECEPTION

1 INTRODUCTION

2 CHOIX GENERAL DE L’ARCHITECTURE DE RECEPTION

2.1 Récepteur hétérodyne

2.2 Récepteur à conversion directe

2.3 Récepteur « Low‐IF »

2.4 Bilan et choix de la structure

3 CHOIX DE LA FREQUENCE INTERMEDIAIRE

3.1 Hypothèses de l’étude

3.2 Etude des interféreurs du standard IEEE 802.15.4

3.2.1 Fréquence intermédiaire de 1.5MHz

3.2.2 Fréquence intermédiaire de 2MHz

3.2.3 Fréquence intermédiaire de 4MHz

3.2.4 Fréquence intermédiaire de 6MHz

3.2.5 Bilan

3.3 Etude des interféreurs du standard IEEE 802.11b

3.3.1 Fréquence intermédiaire de 1.5MHz

3.3.2 Fréquence intermédiaire de 6MHz

3.3.3 Bilan

4 PRESENTATION DE L’ARCHITECTURE RETENUE

4.1 Interface RX/TX

4.2 Suppression du filtre d’antenne

4.3 Amplificateur faible bruit

4.4 Mélangeur

4.5 Conclusion

5 SPECIFICATIONS PRELIMINAIRES POUR CHAQUE ETAGE

5.1 Budget de consommation

5.2 Cahier des charges pour chaque fonction du récepteur

5.2.1 Facteur de bruit global de la chaîne de réception

5.2.2 Budget de gain et de NF

5.2.3 Spécifications de linéarité

5.2.4 Spécifications du signal OL

6 CONCLUSION

BIBLIOGRAPHIE

CHAPITRE III : INNOVATIONS PROPOSEES SUR DES BLOCS SPECIFIQUES : BALUN, LNA ET MELANGEUR

1 INTRODUCTION

2 LNA HAUTE IMPEDANCE

2.1 Structures possibles de LNA

2.1.1 Structure 1: Source commune cascodée

2.1.2 Solution 2 : Structure à grille commune

2.1.3 Bilan

2.2 LNA non adapté

2.3 Impact de la ligne de transmission dans le cas d’un récepteur non adapté

2.4 Présentation des performances du LNA retenu

2.5 Bilan

3 ETUDE DU BALUN

3.1 Introduction

3.2 Choix du type de Balun

3.2.1 Balun externe à composants discrets

3.2.2 Balun externe

3.2.3 Balun intégré

3.3 Choix du rapport de transformation du balun

3.4 Spécifications du Balun 3 accès

3.5 Réalisation du Balun 3 Accès

3.6 Résultats de simulation en puissance du Balun 3 accès

3.7 Fonctionnement du Balun chargé par une forte impédance

3.8 Bilan

4 MELANGEUR SOUS FAIBLE TENSION D’ALIMENTATION

4.1 Introduction

4.2 Mélangeur passif ou Mélangeur actif

4.2.1 Mélangeur actif (Mélangeur de Gilbert)

4.2.2 Mélangeur passif CMOS

4.3 Mélangeur passif en tension

4.4 Améliorations proposées pour le mélangeur passif

4.4.1 Solution 1 : Augmentation du rON

4.4.2 Solution 2 : Réduction du rapport cyclique de la LO

4.4.3 Comparaison des différentes solutions

4.5 Bilan

5 CONCLUSION

CHAPITRE IV : CONCEPTION ET VALIDATION DE LA CHAINE DE RECEPTION

1 INTRODUCTION

2 CONCEPTION DE LA CHAINE DE RECEPTION

2.1 Rappel de l’architecture

2.2 LNA (Amplificateur faible bruit)

2.2.1 Polarisation

2.2.1 Dimensionnement du LNA

2.2.2 Dessin des masques du LNA

2.2.3 Présentation des performances du LNA

2.3 Buffer Post‐LNA

2.3.1 Principe

2.3.2 Polarisation

2.3.3 Interconnexion avec le mélangeur

2.3.4 Présentation du dessin des masques

2.3.5 Présentation des performances

2.4 Conception de la voie LO

2.4.1 Génération du signal carré à rapport cyclique 1/4

2.4.2 Conception du diviseur par deux

2.4.3 Réalisation du dessin des masques

2.4.4 Présentation des performances de la chaîne LO

2.5 Mélangeur passif

2.5.1 Polarisation

2.5.2 Conception et dessin des masques

2.5.3 Performances du mélangeur

2.6 Filtre de canal (ou PMA pour Post Mixer amplifier)

2.6.1 Choix de la structure du PMA

2.6.2 Conception du filtre passe bas

2.6.3 Conception du filtre complexe

2.6.4 Dessin des masques

2.6.5 Performances

3 CHAINE DE RECEPTION COMPLETE

3.1 Dessin des masques

3.2 Performances globales

4 VALIDATION EXPERIMENTALE

4.1 Description de la méthode de validation

4.2 Caractérisation des Balun intégrés

4.2.1 Principe de mesure

4.2.2 Résultats de mesure

4.2.3 Bilan

4.3 Principe de mesure des puces 1 et 2

4.3.1 Méthode de mesure

4.3.2 Réalisation des cartes de test

4.4 Résultats de mesure du récepteur utilisant un balun 50/200Ω et un mélangeur piloté par une LO à rapport cyclique 1/4

4.4.1 Consommation en courant

4.4.2 Réponse réelle du balun intégré

4.4.3 Chaîne de réception complète

4.4.4 Résultats statistiques

4.5 Comparaison des deux modes de pilotage du mélangeur

4.5.1 Consommation en courant

4.5.2 Gain et sensibilité

4.5.3 Linéarité

4.6 Bilan

5 CONCLUSION

BIBLIOGRAPHIE

Télécharger le rapport complet