Etude d’un générateur aléatoire numérique

Montage Darlington

Après avoir présenté brièvement les transistors bipolaires, on présente alors le montage Darlington conçu à partir de deux transistors bipolaires de même type et utilisé principalement comme amplificateur de courant. C’est ainsi qu’afin de commander de forts courants, généralement supérieurs 1A, à partir d’un circuit électronique qui ne peut pas débiter un fort courant, il est nécessaire de disposer de transistor avec un coefficient d’amplification supérieur à 1000. Pour cela on associe deux transistors de même type. C’est le cas du montage Darlington. On peut toutefois remarquer qu’il existe deux types de montage Darlington soit alors: le montage Darlington à transistors NPN et le montage Darlington à transistors PNP. On présente dans ce travail le montage Darlington à transistors NPN que nous avons utilisé dans notre étude.

Comme nous l’avons déjà cité auparavant, le montage Darlington est constitué par l’association de deux transistors T1 et T2 de même Type (deux PNP ou deux NPN). T2 est un transistor de puissance donc de gain en courant petit et dont l’impédance d’entrée h’11 pour le courant nominal est faible ; T1 est un transistor d’usage général de gain normal. La base du transistor T2 est reliée à l’émetteur de T1 et les deux collecteurs sont reliés. L’ensemble est un dispositif à trois électrodes équivalent à un transistor unique dont on va déterminer les paramètres. Le courant de base ?? du transistor T1 est amplifié successivement par le transistor T1 puis par le transistor T2. Ce montage est assimilable à un « super transistor » dont le coefficient d’amplification total ? est très élevé car il correspond au coefficient d’amplification ?1 du premier transistor multiplié par le coefficient d’amplification ?2 du second transistor.

L’AMPLIFICATEUR OPERATIONNEL

Les amplificateurs opérationnels appelés aussi » op amp » ou « AO » ont été au départ inventés pour résoudre analogiquement les problèmes numériques, on citera entre autre l’étude des équations différentiels dont les solutions analytiques sont inconnues. Notons toutefois que les amplificateurs opérationnels ont été au départ conçus avec des composants discrets, avec les progrès technologiques incessants, l’électronique intégrés a permis alors la conception d’amplificateurs opérationnels ayants d’excellentes performances et avec des couts très compétitifs. Ces derniers ne nécessitent alors que peu de composants périphériques, éliminant par la même occasion les problèmes délicats de polarisation engendrés par les AO réalisés avec des composants discrets. Globalement, les amplificateurs opérationnels sont largement utilisés dans de nombreux domaines de l’électronique analogique.

Tension de décalage et courants d’entrée Lorsqu’un amplificateur opérationnel ne reçoit aucun signal sur ses entrées (lorsque ses entrées sont toutes les deux réunies à zéro), il subsiste généralement une tension continue de décalage de la tension de sortie vis-à-vis de zéro. Ce décalage (ou offset) provient de deux phénomènes : la tension de décalage propre aux circuits internes de l’AOP d’une part, et l’influence des courants de polarisation de la paire différentielle des transistors d’entrée sur le circuit extérieur d’autre part. La tension de décalage représente la différence de tension qu’il faudrait appliquer entre les deux entrées d’un AOP en boucle ouverte, quand on a relié une des entrées au zéro, pour avoir une tension de sortie nulle. Cette tension d’offset peut être représentée en série avec l’entrée non-inverseuse ou inverseuse.

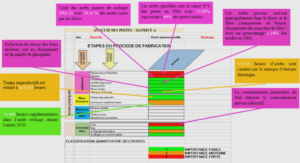

Analyse du générateur numérique de signaux aléatoires : On présente dans ce qui suit le montage que nous avons étudié et qui nous a permis d’obtenir des signaux aléatoires d’origine logique. Les portes logiques NAND (1) et NAND (2) du circuit intégré IC1 forment un oscillateur astable .On détermine la période du signal carré obtenu à la sortie de cet oscillateur par l’expression: T1=2.2 A1C1 (III.1) Pour A1= 47kΩ Et C1=0.22 microfarads On obtient alors une période égale à T1=2.2x47x103x0.22×10-6 = 2.27 10−2 s Il en est de même pour les portes logiques NAND (3) et NAND (4) qui forment elles aussi un oscillateur. La valeur de la résistance de la seconde résistance ajustable (A2) est volontairement décalée de celle de la première et ceci pour avoir une valeur qui diffère de celle du premier ajustable (A1), ceci permettra alors d’obtenir une période du créneau du second ajustable différente de celle du premier ajustable. Les sorties de ces deux oscillateurs sont reliées respectivement aux entrées de la porte NAND (1) du circuit intégré IC2 qui sera à un état haut si au moins l’une de ses deux entrées est à un état bas autrement si les deux entrées sont à un état haut la sortie de cette entrée sera à un état bas.

On remarque donc que la sortie de cette porte logique présente une suite de niveaux logiques, par conséquent la période du signal issu de la sortie (3) de la porte NAND varie sans arrêt Pseudo-aléatoirement. Le filtre passe bas R3C3 élimine le cas litigieux, ou il apparaitrait un niveau bas d’une durée très faible. Les créneaux inversés par la porte NAND (2) seront acheminés à travers la résistance R4 au trigger de Schmitt formés des portes NAND(3) et NAND (4) du circuit intégré IC2 qui délivrera à sa sortie un signal pseudo aléatoire. Ce dernier signal sera appliqué à l’entrée (10) du compteur binaire CD 4040. Le CD 4040 comporte douze étages montés en cascade, et dispose de cinq sorties Q0, Q1, Q2, Q3, Q4. Si ces sorties étaient reliées à des résistances tel que Q1 reliée à R, Q2 reliée à une résistance égale à 2R, Q3 reliée à une résistance égale à 4R, Q4 reliée à une résistance égale à 8R ,Q5 reliée à une résistance égale à 16R, les différentes sorties du compteurs évoluent au rythme du principe du comptage binaire. Si ces différentes sorties étaient reliées respectivement à des résistances R,2R,4R,8R,16R le potentiel recueilli au point commun des différentes résistance pour un position de comptage qu’on notera « comp » qui peut varier dans notre cas de 0 à 31 pourrait être déterminé par:

Le choix du transistor s’est porté sur le 2N2222 car ce dernier est un assez bon candidat au bruit de souffle et permet d’obtenir un bruit de souffle assez important .Le principe repose ici sur l’amplification du petit souffle inhérent au transistor à jonction. On remarque en analysant notre circuit que l’amplification se fait avec deux étages amplificateurs. Le générateur de signaux aléatoires d’origine analogique que nous avons étudié est donc constitué donc d’un transistor bipolaire NPN « T1 » type 2N2222 dont la jonction émetteur/base est polarisée en inverse par la résistance R1 , le collecteur de ce transistor est maintenu en l’air ce qui permet à ce transistor d’émettre au niveau de sa base un large spectre de fréquences qui sont essentiellement dues au bruit de souffle . Ce type de bruit est émis généralement et naturellement par les transistors. Le bruit généré par T1 sera amplifié par T2 qui aura pour tache d’amplifier les signaux récupérés et appliqués sur sa base. La résistance R2 et le condensateur C2 constituent un filtre passe bas qui éliminera alors les fréquences supérieures à sa fréquence de coupure.

|

Table des matières

Chapitre I : étude d’un générateur aléatoire numérique

1. Les Portes logiques

1.1. Portes logiques de base

1.1.1. Inverseur

1.1.2. Porte AND

1.1.3. Porte OR

1.2. Combinaisons de portes logiques

1.2.1. Porte NAND (Non ET)

1.2.2. Porte NOR (Non OU)

1.3. Porte XOR

1.4. Porte NXOR

2. Les multivibrateurs astables

2.1. Différents montages astable

2.1.1. Montage à base de transistors

2.1.2. Montage Astable à ampli opérationnel

2.1.2.1. Principe de fonctionnement

2.1.3. Montage astable à circuit intégré NE555

2.1.4. Montage astable à porte logique

3. Filtres électronique

3.1. Définitions

3.2. Types de filtres

4. Trigger de Schmitt

4.1. Fonctionnement

5. le transistor bipolaire

5.1. Constitution

5.2. Principe de fonctionnement

5.3. Les régimes de fonctionnement

5.3.1. Les régimes de blocage (état bloqué)

5.3.2. Régime linéaire (amplificateur)

5.3.3. Régime de saturation (état passant

5.4. Le transistor en commutation (interrupteur statique)

5.5. Le transistor BD139

5.5.1. Caractéristiques électriques du transistor BD139

5.6. Le transistor BC547

5.6.1. Caractéristiques électriques du transistor BC547

5.6.2. Applications du transistor BC547

6. Montage Darlington

6.1. Principe

6.2. Schéma équivalent en petits signaux

6.3. Paramètres du circuit

6.3.1. Résistance d’entrée

6.3.2. Résistance de sortie

7. Circuit intégré CD4011

7.1. Caractéristiques

8. Compteur binaire CD4040

8.1. Caractéristiques

Chapitre II : étude d’un générateur aléatoire analogique

1. L’amplificateur opérationnel

1.1. Généralités

1.2. Représentation symboliques de l’amplificateur opérationnel

1.3. Polarisation de l’amplificateur opérationnel

1.4. Caractéristiques

1.4.1. L’impédance d’entrée, de gain et gain en puissance

1.4.2. Impédance d’entrée

1.4.3. Impédance de sortie

1.4.4. Gain de puissance

1.5. Tension de décalage et courants d’entrée

1.6. Vitesse de balayage

1.7. Réaction positive et contre-réaction

1.7.1. Définitions

1.8. Application

2. Montage de base de l’amplificateur opérationnel

2.1. Amplificateur suiveur de tension

2.2. Amplificateur de tension mon-inverseur

2.3 Amplificateur de tension inverseur

2.4. Amplificateur différentiel

2.5. Amplificateur sommateur

2.6. Additionneur non-inverseur (extensible a n entrées)

2.7. Intégrateur inverseur

2.8. Dérivateur

2.9. Comparateur de tensions

3. Le transistor bipolaire 2N2222

3.1. Complémentaire des transistors 2N2222

3.2. Caractéristiques électriques du transistor 2N2222

3.3. Applications du transistor 2N2222

4. Potentiomètre

Chapitre III : Résultats et interprétations

1. Analyse du générateur numérique de signaux aléatoires

2. Analyse du générateur Analogique de signaux aléatoires

3. Chronogrammes aux différents noeuds de nos circuits sont donnés dans ce qui suit

3. l. Chronogrammes aux différents noeuds de notre circuit numérique

3.1.1. Les signaux obtenus dans les différents points du circuit N°1

3.2. Chronogrammes aux différents noeuds de notre circuit analogique

3.2.1. Le signal obtenu du circuit N°2

5. Nomenclature des composants

Conclusion générale

Bibliographie

Annexe1

Annexe2

Annexe3

![]() Télécharger le rapport complet

Télécharger le rapport complet