Télécharger le fichier pdf d’un mémoire de fin d’études

La mise en évidence de l’effet tunnel :

Le comportement en température dŠun TFET

Comme nous lŠavons vu, les performances électriques dŠun Tunnel FET dépendent de la tension de grille appliquée. Nous pouvons même considérer deux plages de tension de grille sur lesquelles le Tunnel FET répond à diférents mécanismes de transport des porteurs, comme présenté sur la Ągure 1.12, extraite de lŠarticle [46]. Mookerjea et al. ont réalisé un TFET vertical à base de In0,53Ga0,47As, semiconducteur à gap direct. La zone appelée « BTB Tunneling » est celle où les porteurs sont générés par efet tunnel bande à bande, après le seuil. Elle a donc une très faible dépendance en fonction de la température, cŠest-à-dire seulement celle du gap en fonction de celle-ci ( g ( )) puisque le dispositif est à gap direct. Si lŠon utilise un semiconducteur à gap indirect, la dépendance en température des phonons interviendrait également. Cependant cette dépendance est relativement faible puisque des études sur des dispositifs à base de silicium ont montré un niveau de courant constant en fonction de la température [47, 48, 49]. En revanche la zone appelée « TAT » pour « Trap-assisted Tunneling » présente une augmentation du courant exponentiel avec la tension de grille, cŠest donc la zone sous le seuil. On observe que lŠinverse de la pente sous le seuil de ces courbes se dégradent avec la température. Ce comportement sŠexplique par le fait que les porteurs transitent par efet tunnel de la BV à des pièges dŠénergie du milieu du gap, puis ils sont libérés grâce à lŠagitation thermique et lŠefet de champ par un mécanisme de type PooleŰFrenkel. CŠest à cause de ce second processus, que le courant de ce régime dépend davantage de la température que la transition tunnel bande à bande et que lŠinverse de la pente sous le seuil est dégradé. Le TAT est représenté schématiquement sur la Ągure 1.13.

Cette invariance en température du courant issu de lŠefet tunnel est une caractéristique typique dŠun Tunnel-FET. Elle permet de prouver que lŠon a bien un mécanisme de conduction BBT lorsque la valeur de lŠinverse de la pente sous le seuil reste élevée. Un autre comportement du TFET qui le diférencie des autres transistors est sa dépendance en tension de drain, comme nous allons le voir dans le paragraphe suivant.

La déĄnition des tensions seuils des TFETs :

Il est dŠusage de déĄnir une tension seuil pour les transistors, cette tension permettant de déĄnir la séparation entre le régime de faible et de forte injection pour les MOSFETs, et dŠobtenir le niveau de courant de fonctionnement du transistor. La déĄnition dŠune tension seuil pour un transistor tunnel est tout au tant utile que pour les MOSFETs, mais comme le mécanisme de conduction nŠest pas le même, il a fallu la redéĄnir pour quŠelle est un sens physique. Tout comme pour les MOSFETs, la tension seuil dŠun TFET est la tension à partir de laquelle le courant tunnel change de dépendance en fonction de la tension de grille. LorsquŠune tension de grille est appliquée sur la jonction tunnel, le courant qui la traverse dépend exponentiellement de la tension de grille, car celleŰci diminue la largeur de la barrière tunnel. La largeur de la barrière tunnel possède également une dépendance exponentielle en fonction de la tension drain, ce qui est une particularité des Tunnel FETs étudiée par quelques groupes [23, 51, 52, 48]. En efet pour quŠune transition tunnel dŠune bande à lŠautre se produise, elle requière une valeur minimum de tension de drain pour que le transistor passe dans lŠétat On quelque soit la tension de grille appliquée.

Mais cette barrière tunnel ne peut pas être indéĄniment diminuée, et la dépendance envers les deux tensions appliquées ne sont pas identiques. De Michielis et al. [51] ont montré que la dépendance en Vd provenait de la diminution des niveaux dŠénergie du bas de la bande de conduction induite par lŠapplication de la tension de drain. Ainsi cette dépendance exponentielle atteint rapidement un niveau de saturation pour lequel le courant Id devient indépendant de la tension appliquée au drain, comme on peut lŠobserver sur la caractéristique Id-Vd à Vg Ąxe de la Ągure 1.14, matérialisé par la zone appelée ń superlinear region ż. En ce qui concerne la dépendance en tension de grille, pour VGS > VThG, le courant tunnel aura une dépendance linéaire avec la tension de grille [20, 30]. Ces tensions seuils ne peuvent pas être estimées par la méthode dŠextraction à courant constant, méthode largement utilisée pour les MOSFETs car elle est rapide et facile dŠutilisation, malgré son manque de précision. Cette méthode sous estimerait fortement les valeurs des tensions seuils, car elles resteraient dans les zones de dépendance exponentielle. Pour obtenir les tensions seuil dŠun TFET, nous devons utiliser la méthode utilisant la dérivée seconde de la transconductance, (déjà validée pour les transistors MOS [53]), sur les caractéristiques de transfert et sur les courbes de IDŰVDS à VGS Ąxe.

Malheureusement, lŠextraction des tensions seuils par cette méthode sur nos mesures expérimentales ce sont révélées beaucoup trop bruitées pour extraire des valeurs correctes, malgré nos tentatives de dé-bruitage et lissage des courbes.

Etat de l’art des Tunnels FET à nanofils

Nous allons présenter dans cette partie, quelques exemples de lŠétat de lŠart des Tunnel FET à nanoĄls obtenus selon les deux approches existantes : top-down et bottom-up. Nous centrerons lŠétat de lŠart des TFETs sur les matériaux IVŰIV compatibles avec les procédés de fabrication de lŠindustrie de la microélectronique. Nous distinguerons deux types de TFET pour aller du plus simple à la conĄguration optimum du point de vue du contrôle électrostatique : les transistors planaires avec un recouvrement de grille partiel et ceux à grille totalement enrobante (Gate-all-around). Ayant déjà discuté brièvement lŠétat de lŠart de la pente sous le seuil, dans le paragraphe 1.2.3, nous nous concentrerons sur le niveau de courant de lŠétat ON en fonction du matériau utilisé. Ce paramètre est en fait une des faiblesses des TFET par rapport aux MOSFETs, même si dans le domaine dŠapplication back-end que nous visons, nous nŠavons pas les mêmes contraintes que les dispositifs pour De nombreuses études sur les transistors à nanoĄls en -grille ont été réalisées depuis les années 2000. LŠéquipe de H. Riel de IBM Research-Zurich publia en 2011 des résultats expérimentaux sur lŠintégration de nanoĄls de silicium obtenus par la même technique de croissance que nous utilisons dans la thèse, cŠest-à-dire par CVD-VLS (Dépôt Chimique en phase Vapeur utilisant le mécanisme Vapeur-liquide-solide) [48]. Cette équipe a obtenu les meilleurs résultats publiés sur ce type de nanoĄls à notre connaissance. La croissance des nanoĄls de silicium a été réalisée à 450 ◇C catalysée par des nano-particules dŠor de 20 à 60 nm de diamètre. Le dopage de la partie de typeŰn est de 1,5 ≤ 1020cm⊗3 et celui de le partie p est seulement de 5 ≤ 1018cm⊗3, ils ont réalisé une coquille fortement dopé de type-p autour de la partie drain du Ąl (Ągure 1.15 (a) et (b) ). Ensuite ils ont efectué un recuit à 700 ◇C pour tous les dispositifs.

Ils ont montré lŠinĆuence du contrôle électrostatique sur les performances du TFET par lŠutilisation dŠoxyde de grille à forte constante diélectrique et par la réduction du diamètre du nanoĄl. En efet, la comparaison des caractéristiques obtenues avec lŠutilisation de HfO2 et SiO2 (Ągure 1.15 (c)) montrent bien lŠamélioration du courant Ion et du SS par lŠoxyde de grille alors que le dispositif avec HfO2 à un diamètre plus important que celui avec SiO2. Ensuite lŠinĆuence du diamètre du nanoĄl est montrée par les trois caractéristiques IDS-VGS pour lŠoxyde de grille Al2O3.

Le dispositif présentant les meilleures performances électriques est celui avec HfO2, dont le courant ION = 0,1Û /Û à VDS = ⊗0,5 V et VGS =−2 V avec un SS moyen de 120mV/dec. TFET planaire à base de nanofil SiGe.

En 2014, lŠéquipe de M. Vinet du CEA-LETI de Grenoble présenta un record de niveau de courant sur TFET à base de nanoĄls SiGe obtenus par voie descendante [54]. Ils ont réalisé ces transistors dans lŠoptique dŠune intégration dans le front-end. Ils ont fabriqué un tunnel FET à hétérostructure dont les parties source et drain sont composées de Si1⊗xGex avec x=0,3 et dont le canal est aussi lŠalliage Si1⊗xGex mais avec x compris entre 0,2 et 0,25. LŠinsertion du germanium dans le substrat est réalisée par enrichissement au germanium. Les nanoĄls ont une largeur dŠenviron 5 nm et la longueur de la grille est de 100 nm. Cette dernière a la géométrie -grille comme présentée sur la Ągure 1.16(a) et un oxyde de grille de 1,25 nm dŠEOT.

La caractéristique de transfert de ce dispositif est présentée en Ągure 1.16(b). Le niveau de courant obtenu est de 760ÛA/Ûm pour une tension drain de ⊗0,5 V et de grille de −2 V. LŠinverse de la pente sous le seuil est de 80mV/dec en moyenne sur plus de deux décades. Le courant Iof de la structure est de 20pA/Ûm. En revanche, comme ils ont inséré la même quantité de germanium dans la source comme dans le drain, leur dispositif est ambipolaire. Ce résultat est très encourageant pour une intégration future des Tunnel FET dans le front-end.

Transistor Gate-All-Around

Nous allons présenter dans ce paragraphe un résultat particulier obtenu sur des transistor verticaux à grille totalement enrobante. Cette architecture sera la deuxième étudiée durant la thèse. Nous avons choisi les travaux de lŠéquipe de R. Gandhi de lŠUniversité de Singapour dont la structure est très proche de celle que nous utiliserons et qui a obtenu la meilleure pente sous le seuil sur silicium jusquŠà présent [55].

Leurs nombreuses étapes de fabrication peuvent être résumées comme suit : les nanoĄls ont été obtenus dans un substrat type-p faiblement dopé (1015cm⊗3) par gravure Deep RIE suivie dŠune oxydation thermique à 1000 ◇C et dŠun retrait chimique de lŠoxyde par une solution HF diluée. Ainsi ils ont obtenu des nanoĄls dŠun diamètre compris entre 20 et 200 nm, selon la taille du masque dur. Ensuite ils ont déĄni la zone de drain par implantation dŠions BF2. Ils ont en-capsulé le pied de la structure dans un diélectrique pour réaliser lŠoxyde de grille de 4,5 nm par oxydation thermique suivie dŠun dépôt de silicium amorphe comme contact de grille. La partie source et le contact de grille ont ensuite été implanté par des ions As. Ils ont efectué la siliciuration du contact de la source grâce à 15 nm de nickel, puis tout le dispositif fut recouvert de diélectrique. EnĄn ils ont déĄni les ouvertures de contact dans le diélectrique et réalisé la métallisation avec de lŠaluminium. Chaque implantation a été suivie dŠun recuit dŠactivation à 1000 ◇C.

Ils ont utilisé la ségrégation des dopants par siliciuration pour accumuler les dopants en direction de la jonction tunnel pour la rendre plus abrupte. Ils ont obtenu des niveaux de courant de 1,2ÛA/Ûm à VDS =-1V et un record de lŠinverse de pente sous le seuil sur nanoĄl de silicium de 30mV/dec sur deux décades environ. Leur étude met en avant le fait que lŠinverse de la pente sous le seuil est une fonction du diamètre du nanoĄl, alors que la constante diélectrique de lŠoxyde de grille améliorerait uniquement le niveau de courant du TFET.

Pour conclure sur lŠétat de lŠart des Tunnel FET, nous avons voulu montrer quŠil y a eu beaucoup de dispositifs réalisés, parmi lesquels nous avons choisi de présenter les meilleurs résultats en fonction de la géométrie visée. Les deux dernières études présentées dans cette section avaient pour objectif dŠaméliorer les performances des Tunnel FET en vue dŠune intégration dans le front-end. Nous pouvons voir que de très bonnes performances sont atteintes par les dispositifs composés dŠalliage SiGe. De plus, lŠintégration avec une grille totalement enrobante a montré sa capacité à améliorer la valeur de la pente sous le seuil du dispositif.

La croissance des nanofils semi-conducteurs IV-IV

Les différentes méthodes d’élaboration des nanofils

Il y a deux approches pour lŠélaboration des nanoĄls, lŠapproche descendante et ascendante, parmi lesquelles il existe de nombreuses méthodes dŠélaboration. Nous ne les détaillerons pas ici mais nous ferons une description de la classiĄcation en deux approches.

Approche descendante

LŠapproche descendante ou dite ń top-down ż en Anglais est traditionnellement utilisée en microélectronique pour la réalisation de structures pour les dispositifs. Elle regroupe les étapes de dépôt de Ąlm mince, de lithographie et de gravure qui permettent de déĄnir la composition et la géométrie du futur composant. Tout dŠabord, le ou les matériaux composants les nanostructures sont épitaxiés sur un substrat. Puis grâce aux techniques de lithographie (optique ou électronique), un masque de gravure en résine est déĄni sur celuiŰci, suivi de la gravure elle-même (généralement par voie sèche) pour la réalisation des 302Élaboration des transistors à nanoĄls Si et Si/SiGe et méthode dŠextraction des paramètres électriques nanoĄls. Ceux-ci peuvent être horizontaux ou verticaux, selon le masque déĄni en résine et la gravure utilisée. Cette approche a été utilisée dans les travaux des équipes de M. Vinet et R. Gandhi présentés dans le paragraphe 1.3.2 du chapitre 1.

Les avantages de cette technique sont :

Ů le très bon contrôle du/des matériaux constituants, et de la direction cristallographique des nanoĄls

Ů une forte reproductibilité

Ů une excellente localisation des nanoĄls

Ů un niveau de dopage bien contrôlé pendant la croissance ou par implantation ionique

Les désavantages de cette technique pour notre application sont :

Ů Les recuits dŠactivation des dopants à haute température

Ů La nécessité dŠavoir un substrat cristallin dans les étapes dŠinterconnexions.

Ů La rugosité de surface des nanoĄls induite par les gravures et le dopage par implanta-tion.

Il nous faut donc une autre méthode pour obtenir des nanoĄls cristallins à basse température, tel que le permet lŠapproche ascendante.

Approche ascendante

LŠapproche ascendante (ou ń bottom-up ż) est une toute autre vision de la réalisation des objets de taille nanométrique. En efet, à la place dŠun dépôt pleine plaque de matériau qui sera ensuite gravé, implanté, passivé, etc, pour déĄnir le composant, cette approche permet de faire croître le matériau ayant les caractéristiques nécessaires au composant Ąnal. La croissance est lŠétape clé de cette approche, car elle permet de déĄnir le ou les matériaux [56, 57, 58, 59], leurs directions cristallographiques [60], leurs géométries (nano-rubans, nanoĄls horizontaux ou verticaux) [61, 62] et le niveau de dopage du dispositif [63, 64, 65], tout ceci en une seule étape. Pour synthétiser des nanoĄls, il existe diférentes techniques de croissance dont les principales sont lŠépitaxie par jet moléculaire (« Molecular Beam Epitaxy », MBE) et le dépôt chimique en phase vapeur (« Chemical vapour deposition », CVD). Un schéma de ces deux méthodes de dépôt est montré en Ągure 2.1 pour la croissance de nanoĄls de silicium par le mécanisme vapeur-liquide-solide (VLS). Nous présenterons en détails le mécanisme VLS dans le paragraphe 2.1.2.1, mais tout dŠabord, nous allons nous intéresser aux diférences entre les deux techniques de croissance, MBE et CVD. LŠépitaxie par jet moléculaire, comme présenté sur la Ągure 2.1, a un apport de matière directionnel, car elle utilise lŠévaporation de source de matériau pure sous ultra-vide comme apport de matériau. Ces atomes ou molécules sont ensuite adsorbés sur le substrat dŠoù ils difusent pour sŠagglomérer aĄn de réaliser la structure souhaitée. Cette technique a des vitesses de croissance relativement lentes, cŠest-à-dire de lŠordre de 1 µm/h, due à son environnement sous ultra-vide et donc aux faibles pressions partielles, 10⊗8 à 10⊗9 Torr, utilisées durant les dépôts. À cause des conditions dŠultra-vide, des procédés de microélectronique à grande échelle sont diicilement réalisables en MBE. CŠest pourquoi

La croissance des nanoĄls semi-conducteurs IV-IV 31

Le dépôt chimique en phase vapeur est une technique largement utilisée dans lŠindustrie de la micro-électronique et en recherche. Le terme « phase vapeur » vient du fait que les matériaux sont acheminés sous forme de gaz appelés gaz précurseurs. Cette amenée de précurseur est supposée isotrope contrairement à la MBE, comme représentée sur la Ągure 2.1. Ces gaz sont le silane (SiH4) et le germane (GeH4) pour le silicium et le germanium respectivement. La décomposition de ces gaz précurseurs à la surface du substrat est généralement thermiquement activée. Le lieu de la décomposition des précurseurs dans un bâti CVD est sélectionné par la chimie de surface. Dans le cas dŠune croissance catalysée de type VLS, le catalyseur Ąxe le périmètre du nanoĄl. Une fois le gaz précurseur décomposé, le matériau souhaité est incorporé dans le catalyseur et les déchets produits par la réaction chimique sont sous forme gazeuse. La croissance est réalisée à basse pression, dans notre étude elle sera de 3 ou 4,5 Torr. Les vitesses de croissance sont de lŠordre de 100 nm/min à 1 µm/min. La croissance CVD est une approche intéressante pour réaliser des dépôts sur des substrats de grande dimension, dans des temps courts de croissance, et cela avec une grande sélectivité du dépôt grâce à la chimie de surface.

Présentation de la technique de croissance par CVD-VLS

Dans ce paragraphe, nous allons détailler le mécanisme de croissance VLS, le réacteur CVD et la préparation des substrats avec les catalyseurs.

32Élaboration des transistors à nanoĄls Si et Si/SiGe et méthode dŠextraction des paramètres électriques

La croissance par le mécanisme VLS

Le nom du mécanisme VLS reprend les trois états physiques du matériau pendant le processus de dépôt. De nombreuses études théoriques ont été menées sur la modélisation de ce mécanisme de croissance [67, 68, 69, 70, 71, 72]. On peut schématiser le mécanisme VLS par la Ągure 2.2(a) où chaque étape est décomposée dans le cas dŠune croissance CVD, mais de manière générale il se résume par les trois phases suivantes :

1. Le matériau est acheminé jusquŠau catalyseur métallique sous forme gazeuse (étape 1, Ągure 2.2(a)).

2. le précurseur est alors adsorbé à la surface du catalyseur liquide (étape 2.i), puis il se décompose (étape 2.ii) et le silicium sŠincorpore et difuse dans la goutte (étape 3), celleŰci étant à une température au dessus de lŠeutectique de lŠalliage ainsi formé. La composition de cet alliage peut-être représentée par son diagramme de phase, comme sur la Ągure 2.2 b) pour lŠexemple du silicium catalysé par lŠor.

3. Lorsque la concentration en matériau à déposer a atteint un niveau de saturation dans la goutte, celui-ci se cristallise à lŠinterface entre le liquide et le substrat (étape 4).

La précipitation peut se produire théoriquement nŠimporte où dans le liquide. Mais il est plus favorable énergétiquement pour le système, que le matériau précipite vers la phase solide existante plutôt que de créer une nouvelle interface liquide-solide. LŠinterface entre le catalyseur et le substrat est donc le site préférentiel de la précipitation. Par conséquent sa taille et sa forme déterminent celles du volume de matériau précipité. CŠest pourquoi la mise en forme du catalyseur en goutte de taille nanométrique est très importante pour lŠobtention des Ąls de cette dimension. Nous verrons la préparation du catalyseur sur le substrat dans le paragraphe 2.1.2.2.

Dans le cas de la croissance par CVD-VLS, le catalyseur est principalement un catalyseur chimique, car il accélère la décomposition du précurseur à lŠinterface vapeur-liquide, rendant ainsi plus probable la décomposition des précurseurs sur le catalyseur que sur le substrat. Cependant, des mécanismes de croissance parasites (difusion, décomposition nonŰcatalysée)

La croissance des nanoĄls semi-conducteurs IV-IV 33

peuvent se produire et recouvrir dŠun dépôt 2D les Ćancs du nanoĄls et le substrat, comme présenté sur la Ągure 2.3. Ce dépôt est particulièrement problématique lorsque lŠon réalise le dopage inŰsitu des nanoĄls, une coquille de dopage est alors présente sur des parties intrinsèques, comme cela est expliqué dans lŠétude de Amit et al. [64]. Dans le cas des croissances de diode pŰiŰn, cette coquille peut court-circuiter les jonctions et induire une caractéristique électrique non plus de diode mais de Ąl uniformément dopé dŠun seul type de dopant. Les paramètres de croissance de nanoĄl de silicium et SiGe ont été optimisées lors des précédents travaux de thèse pour limiter ce dépôt, grâce à la diminution de la température de croissance et à lŠincorporation du HCl. Les nanoĄls seront donc exempts du dépôt 2D pour les faibles ratios de dopage et concentration de germanium. Nous verrons dans la suite que hors de ces conditions, un dépôt 2D sera présent le long des nanoĄls et que les conditions de croissance seront réŰévaluées pour limiter le dépôt nonŰcatalysé.

Les outils de la croissance CVD-VLS

Le réacteur

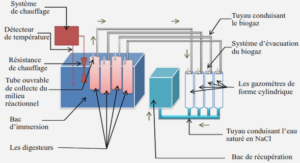

La croissance CVD est réalisée dans un réacteur RPCVD (Reduced Pressure Chemical Vapour Deposition) de marque EasyTubeTM3000 commercialisée par FirstNano. Le schéma simpliĄé du réacteur et des lignes de gaz est représenté sur la Ągure 2.4.

La taille maximale des substrats acceptés est de 100 nm. Sur ce bâti, il y a 8 lignes de gaz indépendantes ainsi quŠune ligne dŠazote. Comme présenté sur la Ągure 2.4, un Ćux de dihydrogène (H2) et de diazote (N2) est maintenu constant durant la croissance. Ils sont acheminés par la ligne « background » au début de la chambre de façon à instaurer un Ćux de gaz porteur continu et laminaire. Les gaz précurseurs accessibles sont le silane (SiH4) et le germane (GeH4), ce dernier étant dilué à hauteur de 10% dans le dihydrogène (H2). Les gaz dopants sont le diborane (B2H6) pour le dopage de type p et la phosphine (PH3) pour le dopage de type n. Les lignes dŠacheminement des gaz dopants sont équipées dŠun système de dilution par H2 avant dŠentrer dans la chambre. Ainsi le ratio de dopants insérés dans la chambre doit être calculé de la manière suivante : B/P = dopant = 0,2 entrée × injectée (2.1) précurseur100 injectée + diluéeprécurseur.

Où entrée est le Ćux de dopants avant la dilution au H2, injectée est le Ćux de dopant inséré dans la chambre après dilution, diluée est la quantité de Ćux de gaz dopants à diluer. Et précurseur est le Ćux de silane ou bien de germane (dilué à hauteur de 10%) ou encore lŠaddition des deux dans le cas dŠun nanoĄl Si1⊗xGex.

De plus, pour améliorer la morphologie des nanoĄls et éviter la difusion de lŠor le long de ceux-ci [68], nous utilisons le gaz HCl pour passiver la surface des nanoĄls par chlorination durant la croissance [74]. Ces gaz sont acheminés par la ligne dŠinjection qui débouche juste avant le porte échantillon dans le sens du Ćux. Les purges de lignes et la préparation des Ćux avant injection dans le bâti sont réalisées grâce à la ligne dŠévacuation qui ne passe pas par la chambre de dépôt et débouche au niveau de la pompe primaire.

Toutes les lignes dŠamenée des gaz sont équipées de débitmètre de masse pour contrôler précisément les quantités et ratios de gaz en temps réel. Ainsi nous pouvons moduler la composition des nanoĄls, le type de dopage et son niveau en jouant sur le ratio de dopant (2.1) durant la croissance. Ce réacteur est dit à parois chaudes car le système résistif englobe le tube de quartz dans lequel est réalisé le dépôt. De cette façon, le porte-échantillon et les parois peuvent-être chaufés dans la gamme de 100 à 1000 ◇C. La température de croissance est contrôlée par trois thermocouples placés le long du bras soutenant le porte-échantillon et est asservie sur le thermocouple se trouvant à la perpendiculaire de lŠéchantillon. Ce type de réacteur est à opposer aux réacteurs à murs froids où seul le porte échantillon est chaufé ce qui évite lŠefet mémoire des parois du bâti comme nous le verrons dans la suite.

La préparation des substrats pour la croissance

La bonne morphologie et lŠenvironnement du catalyseur sont des points essentiels pour obtenir une bonne croissance, comme nous le verrons en détails dans la suite. Ainsi tout commence avec le dépôt dŠor sur les substrats, comme futur catalyseur. Durant la thèse, nous avons utilisé des substrats de silicium dont lŠorientation cristallographique est [111] pour favoriser la croissance verticale des nanoĄls.

Pour réaliser des transistors à nanoĄls horizontaux, ces substrats étaient non dopés et découpés en morceaux de 1 cm2. Nous avons retiré lŠoxyde natif du silicium grâce à un nettoyage standard à partir dŠune solution appelée BOE (ń Bufered Oxide Etchant ż, qui est un mélange de HF 49% et de NH4F 40%, voir annexe ??) pour permettre la relation dŠépitaxie entre le substrat et le dépôt catalysé souhaité. Nous avons ensuite placé comme catalyseur soit une couche uniforme dŠor de 2 nm dŠépaisseur, soit des colloïdes dŠor commerciaux ayant un diamètre de 50 à 100 nm. La première solution fournit des nanoŰgouttelettes après un recuit dans la chambre de croissance. La formation de ces gouttelettes est complexe car dépendante de nombreux paramètres, leur distribution en taille est relativement large. Mais elle peut être relativement contrôlée par lŠépaisseur de la couche dŠor déposée, la température et la durée du recuit. Les colloïdes dŠor quant à eux, permettent dŠavoir une distribution en taille réduite des nanoŰgouttelettes après recuit et ils sont assez simple dŠutilisation. En efet, la dispersion des colloïdes sur le substrat est représentée sur la Ągure 2.5.

On dépose une goutte de solution de colloïdes décorés dŠions citrates sur le substrat. Les ions citrates permettent que la surface des nanoparticles dŠor soit chargée négativement ce qui empêche leur agglomération. On introduit une dose de HF dans la goutte pour diminuer le pH de la solution en dessous de 3,1, permettant ainsi de convertir les ions citrates en acide citrique. Les nanoparticules dŠor ont alors une surface neutre ce qui leurs permet dŠadhérer au substrat de silicium. Il faut ensuite retirer la goutte du substrat dans les 60 s après insertion du HF, pour éviter que les colloïdes ne sŠagglomèrent, OŠReilly et al [75].

Pour la réalisation des transistors verticaux, nous avons utilisé des substrats 2 pouces dopés à 2 ≤ 1019cm⊗3 de type p. Ce niveau de dopage a fait lŠobjet dŠun compromis, car nous souhaitions nous servir du substrat comme contact face arrière (contact drain). Mais nous ne voulions pas un dopage trop important, car alors la partie source aurait été moins dopée que la partie drain. En efet, dans une structure pŰiŰn obtenue par dopage in situ, comme nous lŠavons dit précédemment, nous devons limiter le dopage pour éviter la croissance dŠune coquille 2D le long du nanoĄl. Nous avons essayé diférents niveaux de dopage et nous avons trouvé que pour un niveau de dopage supérieur à 5 ≤ 1019cm⊗3 la coquille 2D était présente et court-circuitait les jonctions de la diode pŰiŰn. Ce niveau de dopage est donc la limite haute pour toutes les croissances de diodes pŰiŰn, aĄn de ne pas recouvrir les Ćancs du nanoĄl par un dépôt 2D. Une fois nos substrats choisis, nous avons localisé des nanoparticules dŠor sur le substrat. Pour ce faire, nous avons étalé successivement deux couches de résines électroniques (PMMA/MMA tous les détails sont dans lŠannexe B.1). Après la lithographie électronique et le développement des résines, nous avons retiré lŠoxyde natif des surfaces ainsi ouvertes par un nettoyage BOE standard (annexe ??). Puis nous avons déposé une couche dŠor de 20 nm par évaporation. Après le lift-of et les nettoyages, 362Élaboration des transistors à nanoĄls Si et Si/SiGe et méthode dŠextraction des paramètres électriques nous obtenons des disques dŠor de 120 nm de diamètre aĄn de réaliser une croissance de nanoĄls verticaux localisés, comme nous le verrons dans la suite de ce chapitre. On peut voir sur les Ągures 2.6 a), b) et c) que très peu dŠor est déposé entre les catalyseurs, ce qui permet de conserver un espacement de 1 µm entre chaque catalyseur.

Figure 2.6: Images MEB dŠun substrat typique avec les catalyseurs dŠor localisés déposés pour la croissance verticale localisée des nanoĄls : a) Zoom sur un catalyseur de 121 nm de diamètre et lŠon peut constater quŠil nŠy a que de très Ąnes traces laissées autour du catalyseur par la technique de dépôt dŠor ; b) Vue dŠensemble de plusieurs catalyseurs localisés montrant la bonne reproductibilité du motif ; c) Zone de localisation des catalyseurs permettant une intégration verticale de nombreux nanoĄls.

Avant dŠintroduire les substrats dans le réacteur CVD, ceux-ci sont désoxydés par un trai-tement HF vapeur/liquide (49%/10%). Immédiatement après, les substrats sont introduits dans le sas de la chambre où lŠatmosphère est purgée puis placée sous azote. EnĄn ils sont introduits dans la chambre où ils sont recuits sous un mélange N2/H2 pendant 25 min entre 600 ◇C et 650 ◇C pour former un catalyseur liquide composé dŠor et de silicium, puis on introduit les gaz précurseurs et les processus de croissance expliqués dans la section 2.1.2.1 commencent.

Les nanofils de silicium, l’alliage Si1⊗xGex et leurs hétérostructures

Depuis 2006, notre équipe travaille sur lŠétude de la croissance des nanoĄls. Grâce aux thèses de Fabrice Oehler [66] et Florian Dhalluin [76], les conditions optimales de croissance de nanoĄls de silicium ont été sondées. LŠimpact de la température et pression de la chambre, ainsi que celui du diamètre et du métal utilisé comme catalyseur a été montré sur la croissance des nanoĄls silicium. Le rôle crucial de la température et de lŠinsertion du HCl a été mis en évidence pour minimiser la migration de lŠor et le dépôt non-catalysé le long des nanoĄls. Puis notre équipe a étudié les conditions de croissance de nanoĄls dans un alliage très prometteur, le Si1⊗xGex. Ainsi le travail de thèse dŠAlexis Potié [77] a montré lŠimportance du HCl sur lŠinsertion du germanium dans les nanoĄls [78], grâce à quoi, la gamme de concentration du germanium inséré dans Si1⊗xGex est très large. Et la thèse de Priyanka Periwal [79] a permis la croissance optimisée dŠhétérostructures Si/Si1⊗xGex. Une grande partie des nanoĄls utilisés pour les TFET horizontaux ont été réalisés par P. Periwal. Elle a étudié en détails lŠefet réservoir dû au catalyseur dŠor qui dégradait lŠinterface entre les jonctions [57], ainsi que le dopage des nanoĄls Si/Si1⊗xGex par le bore pour le type p et le phosphore pour le type n. Riche de ces études, nous avons repris les conditions de croissance présentées dans ces thèses pour les adapter à la croissance de nanoĄls courts (dŠune longueur dŠenviron 1 µm) à partir de catalyseurs localisés pour réaliser des transistors verticaux. Avant de décrire les étapes de croissance, il nous faut rappeler que les nanoĄls sont crus dans lŠoptique dŠêtre des briques élémentaires de dispositifs électroniques. De ce fait, ils doivent répondre à certains critères aĄn dŠassurer le bon fonctionnement électrique du dispositif, tels que : être monocristallin et avoir peu de défauts ainsi quŠune faible rugosité de surface, un niveau de dopage élevé avec un proĄl de dopage le plus abrupte possible entre la source et le canal. Ces critères ont été éprouvés sur substrats recouverts de colloïdes et de Ąlm dŠor, lors des diférentes thèses présentés précédemment.

Ainsi durant les trois ans de thèse, nous avons synthétisé diférents nanoĄls avec des dopages variés. Nous pouvons regrouper ces croissances en deux catégories : les homo-structures Si ou Si0,7Ge0,3 et les hétéro-structures Si/Si1⊗xGex. Nous allons décrire dans la suite, les grandes lignes de la croissance de ces nanoĄls. Nous donnerons les données exactes de chaque croissance avec les caractéristiques électriques associées aux dispositifs dans les chapitres suivants. Mais avant de détailler la méthodologie de croissance, il est important de spéciĄer la diférence entre un nanoĄl cru pour une intégration horizontale et en vue dŠune intégration verticale.

Pour lŠintégration horizontale des nanoĄls, nous avons réalisé des Ąls relativement longs entre 7 et 10 µm de long. Comme présenté précédemment, nous avons optimisé les conditions de croissance pour limiter le dépôt 2D non catalysé sur le substrat et le long des Ąls, même sur des temps de croissance longs (entre 30 min et 2 h).

Pour lŠintégration verticale des nanoĄls, nous avons besoin quŠils aient une longueur comprise entre 1 µm et 1,5 µm. Pour des nanoĄls plus courts, il est diicile de venir prendre deux contacts le long des Ąls (contact de grille et de drain) sans risquer de courtŰcircuiter le dispositif avec notre procédé de fabrication. De plus, réaliser des Ąls de cette longueur nécessite une très bonne maîtrise de la croissance des nanoĄls et des contaminations du bâti.

Les homoŰstructures

La croissance CVD est composée de trois étapes principales : la montée en température du bâti et de lŠéchantillon, lŠincubation de la croissance et le dépôt luiŰmême. Ces trois étapes seront le sujet des prochains paragraphes, détaillés selon nos conditions de croissance. Les croissances des homostructures se déroulent sans arrêt des gaz précurseurs de silane et/ou de germane ainsi que du HCl. Les Ćux de dopants sont quantŰeux stoppés durant la croissance pour obtenir la partie intrinsèque du Ąl.

Les diodes p-i-n en silicium ont été obtenues à 600 ◇C avec un débit de silane entre 20 et 40 sccm, avec 100 sccm de HCl à une pression dans la chambre de croissance de 3 Torr. Les rapports de Ćux de dopants sur Ćux de silane utilisés (dŠaprès lŠéquation 2.1) sont compris entre 7 ≤ 10⊗4 et 10⊗3. Pour un ratio de 1 ≤ 10⊗3, les mesures de résistivité quatre pointes donnent une densité dŠatomes de 5 ≤ 1018cm⊗3 pour B2H6 et de 2 ≤ 1019cm⊗3 pour PH3 [74], ces valeurs sont estimées à partir de la résistivité du silicium massif.

Les diodes p-i-n en Si0,7Ge0,3 ont été obtenues à 450 ◇C avec un débit de silane de 90 sccm et de germane de 45 sccm, avec 45 sccm de HCl pour une pression de 4,5 Torr dans la chambre. Les rapports de Ćux de dopants sont compris entre 5,3 ≤ 10⊗4 et 10⊗3 pour le Si0,7Ge0,3 ce qui est équivalent dŠaprès les mesures TofŰSIMS pour les plus forts ratio de dopant à une densité dŠatomes de 1 ≤ 1019cm ⊗3 pour B2H6 et de 1 ≤ 1020cm⊗3 pour PH3. Cependant, les mesures TofŰSIMS ne révèlent pas le niveau de dopage électriquement actif.

Les hétéroŰstructures

Pour obtenir les meilleures hétéroŰstructures pour les Tunnel FETs, nous avons besoin dŠune jonction abrupte entre le canal et la source du transistor. Or il y a un important efet réservoir du germanium par le catalyseur. En efet, le Si1⊗xGex sŠincorpore plus lentement au nanoĄl que le Si pour la même température de croissance (vitesse de croissance du Si0,7Ge0,3 =100 nm/min et celle du Si=175 nm/min pour une température de 450 ◇C). Pour contrer cela, Priyanka Periwal a étudié lŠimpact des arrêts de croissance pour diminuer cet efet réservoir. Elle a montré quŠun arrêt de 2 min de croissance, sous Ćux continu de HCl, permettait de mieux gérer les changements de composition par le catalyseur. Ainsi la nouvelle composition dŠéquilibre est atteinte plus rapidement, ce qui diminue la largeur de la jonction. De plus ce temps dŠarrêt perturbe peu lŠéquilibre du catalyseur, car 70% des nanoĄls crus avec le stop de croissance sont droits. Cependant, même avec les arrêts de croissances, les jonctions Si/Si0,7Ge0,3 et Si0,7Ge0,3/Si ne sont pas identiques. Car pour lŠinterface Si1⊗xGex/Si, la concentration de Ge dans le catalyseur est déjà à lŠétat de saturation. Quand on arrête lŠarrivée de germanium, celui-ci va sŠinsérer lentement dans le nanoĄl. En revanche pour la jonction inverse, Si/Si0,7Ge0,3, le silicium présent dans le catalyseur sŠinsère dans le nanoĄl pratiquement deux fois plus vite que le Si0,7Ge0,3. Donc la concentration en silicium dans le catalyseur diminue rapidement. Ainsi lorsque lŠon incorpore le SiH4 et le GeH4, le catalyseur atteint rapidement la concentration de saturation du liquide Au-Si-Ge, en silicium et germanium au vu des Ćux de précurseurs. Par conséquent le proĄl de concentration en germanium de lŠinterface Si/Si0,7Ge0,3 est moins étalée que pour la première [57].

Le rapport de stage ou le pfe est un document d’analyse, de synthèse et d’évaluation de votre apprentissage, c’est pour cela chatpfe.com propose le téléchargement des modèles complet de projet de fin d’étude, rapport de stage, mémoire, pfe, thèse, pour connaître la méthodologie à avoir et savoir comment construire les parties d’un projet de fin d’étude.

|

Table des matières

1 Introduction

1.1 Du MOSFET vers le Tunnel FET

1.1.1 La miniaturisation du MOSFET

1.1.2 La puissance statique et dynamique des MOSFETs

1.1.3 Les dispositifs à faible inverse de pente sous le seuil

1.1.3.1 Les dispositifs à EFFET KINK :

1.1.3.2 LŠIMOS :

1.1.3.3 Les Tunnel FETs :

1.2 Introduction du Tunnel FET

1.2.1 Structure et fonctionnement du Tunnel FET

1.2.2 InĆuence du design sur le niveau de courant du Tunnel FET

1.2.2.1 Efet du matériau de la source

1.2.2.2 Efet de la géométrie du dispositif

1.2.3 InĆuence des paramètres sur lŠinverse de la pente sous le seuil (SS)

1.2.4 La mise en évidence de lŠefet tunnel :

1.2.4.1 Le comportement en température dŠun TFET

1.2.4.2 La déĄnition des tensions seuils des TFETs :

1.3 Etat de lŠart des Tunnels FET à nanoĄls

1.3.1 Transistors planaires

1.3.2 Transistor Gate-All-Around

1.4 Conclusion du chapitre dŠintroduction

2 Élaboration des transistors à nanofils Si et Si/SiGe et méthode d’extraction des paramètres électriques

2.1 La croissance des nanoĄls semi-conducteurs IV-IV

2.1.1 Les diférentes méthodes dŠélaboration des nanoĄls

2.1.1.1 Approche descendante

2.1.1.2 Approche ascendante

2.1.2 Présentation de la technique de croissance par CVD-VLS

2.1.2.1 La croissance par le mécanisme VLS

2.1.2.2 Les outils de la croissance CVD-VLS

2.1.3 Les nanoĄls de silicium, lŠalliage Si1⊗xGex et leurs hétérostructures

2.1.3.1 Les homoŰstructures

2.1.3.2 Les hétéroŰstructures

2.1.3.3 Variabilités des propriétés des nanoĄls

2.1.3.4 LŠintérêt du HCl

2.2 Transistors à nanoĄl planaires et verticaux

2.2.1 Le nettoyage des nanoĄls

2.2.2 Le procédé dŠintégration planaire des nanoĄls

2.2.2.1 Dispersion des nanoĄls

2.2.2.2 Réalisation du TFET à base dŠun nanoĄl horizontal :

2.2.3 Le procédé dŠintégration verticale des nanoĄls

2.2.4 La siliciuration des contacts drain-source

2.2.4.1 La siliciuration des Ąls de silicium

2.2.4.2 La siliciuration des Ąls SiGe

2.3 Extraction des propriétés électriques

2.3.1 Paramètres électriques clefs des transistors

2.3.2 Capacité de grille

2.3.3 Extraction des propriétés électriques des Tunnel FETs

2.4 Conclusion du chapitre

3 Étude des propriétés électriques des tunnel FET à nanofil à hétérojonction Silicium

3.1 LŠeicacité du dopage inŰsitu :

3.1.1 La modulation du dopage le long dŠun nanoĄl de silicium

3.1.2 Estimation du niveau de dopage des nanoĄls de silicium

3.1.3 La prise de contact sur les nanoĄls :

3.2 Efet du niveau de dopage sur les performances entre TFET à base de nanoĄl de silicium.

3.2.1 Observation des caractéristiques de diode avant lŠutilisation en TFET

3.2.2 Les caractéristiques de transfert des Si NW TFETs pour diférents niveaux de dopage.

3.3 LŠanalyse des mécanismes de lŠefet tunnel

3.4 Efets de lŠamélioration du couplage électrostatique et de la siliciuration.

3.4.1 Conclusion sur les transistors nanoĄl Silicium

4 Étude des propriétés électriques des TFETs à nanofil contenant du germanium

4.1 Les propriétés de lŠalliage SiGe

4.1.1 Efets de la concentration de germanium sur les propriétés électriques dŠun TFET.

4.2 Les hétérojonctions pŰiŰn à base de nanoĄls Si0,7Ge0,3.

4.2.1 La croissance et le diagramme de bande des nanoĄls Si0,7Ge0,3

4.2.2 Les mesures électriques à lŠambiante des TFETs Si0,7Ge0,3

4.2.3 Simulation des courbes électriques des TFETs Si0,7Ge0,3

4.2.4 Conclusion sur les transistors nanoĄl à alliage SiŰGe (30% de Ge)

4.3 Les hétérostructures Si/Si/SiGe avec 30% de germanium.

4.3.1 En quoi une hétérostructure estŰelle bénéĄque pour les performances des TFETs ?

4.3.2 Le proĄl de dopage et de composition pour une hétérostructure

4.3.3 Les mesures électriques du TFET Si/Si/Si0,7Ge0,3

4.3.4 Simulation des courbes électriques du TFET Si/Si/Si0,7Ge0,3

4.4 Optimisation de lŠhétérostructure Si/Si/SiGe.

4.4.1 Augmentation de la concentration de germanium dans les nanoĄls pour lŠintégration horizontale.

4.4.2 Le TFET à nanoĄls Si/Si/Si0,3Si0,7 verticaux

4.4.2.1 La structure

4.4.2.2 Caractéristique électrique du TFET à nanoĄls Si/Si/Si0,3Si0,7 verticaux

4.4.3 Conclusion sur lŠoptimisation des hétérostructures.

4.5 Conclusion du chapitre

5 Conclusion générale de la thèse et Perspectives

5.1 Conclusion générale de la thèse

5.2 Perspective

Annexe

A Nettoyage BOE standard

B Lithographie

B.1 Procédé de localisation des catalyseurs par EBEAM

B.2 Paramètres de la lithographie des contacts Drain/source et Grille

Publications

Bibliographie 129

Télécharger le rapport complet