Etude des éléments logiques et des éléments combinatoires

THEORIE DES MACHINES SYSTOLIQUES

LES MACHINES PARALLELES

Introduction

Ce chapitre donne une aperçue générale des machines parallèles, particulièrement les machines systoliques. Le parallélisme est l’évolution simultanée des différentes opérations ou calculs au niveau des processeurs (que ce soit arithmétique ou logique). En effet, la plupart des microprocesseurs modernes ne sont plus entièrement séquentielle ; ils sont dotés de fonctions de parallélisme. Par exemple il n’est pas rare (Pentium, power PC, etc.) d’avoir plusieurs unités de calcul arithmétique pouvant fonctionner en parallèles.

Avantages et inconvénients

Le principal avantage du parallélisme est la vitesse de calcul. Pour N processeurs en parallèle, le calcul est exécuté plus vite qu’en mode séquentiel classique.

L’inconvénient est la nécessité d’une espace mémoire plus grande.

Difficultés

– Il faut gérer le partage des tâches ;

– Il faut gérer l’échange d’information car une erreur peut fausser toute l’opération.

Les différents modèles de machines parallèles

On distingue classiquement quatre types des machines parallèles : SISD, SIMD, MISD et MIMD.

Cette classification est basée sur les notions de flot de contrôle (les deux premières lettres) et flot de données (les deux dernières lettres).

Machine SISD

Une machine SISD (Single Instruction Single Data) ou flux à une instruction et une donnée, est ce que l’on appelle d’habitude une machine séquentielle, ou machine de Von Neumann. Une seule instruction est exécutée à un moment donné et une seule donnée (simple, non structurée) est traitée à un moment donné.

float[10] A,B,C

for (init i=0 ;i<10 ;i++)

C[i]=A[i]+B[i];

Ce code s’exécute sur une machine séquentielle en faisant les additions :

A[0]+B[0], A[1 ]+B[1],…,A[9]+B[9] à la suite les unes des autres.

Machine MISD

Une machine MISD (Multiple Instruction Single Data) est une machine à plusieurs instructions. Une donnée peut exécuter plusieurs instructions en même temps. Cela peut paraître paradoxal mais cela recouvre en fait un type très ordinaire de microparallèlisme dans les microprocesseurs moderne : les processeurs vectoriels et les architectures pipelines.

|

Guide du mémoire de fin d’études avec la catégorie Génie Informatique |

|

Étudiant en université, dans une école supérieur ou d’ingénieur, et que vous cherchez des ressources pédagogiques entièrement gratuites, il est jamais trop tard pour commencer à apprendre et consulter une liste des projets proposées cette année, vous trouverez ici des centaines de rapports pfe spécialement conçu pour vous aider à rédiger votre rapport de stage, vous prouvez les télécharger librement en divers formats (DOC, RAR, PDF).. Tout ce que vous devez faire est de télécharger le pfe et ouvrir le fichier PDF ou DOC. Ce rapport complet, pour aider les autres étudiants dans leurs propres travaux, est classé dans la catégorie Architecture Systolique où vous pouvez trouver aussi quelques autres mémoires de fin d’études similaires.

|

Table des matières

Chapitre1 : THEORIE DES MACHINES SYSTOLIQUES

1. LES MACHINES PARALLELES

1.1. Introduction

1.2.Les différents modèles de machines parallèles

1.2.1. Machine SISD

1.2.2. Machine MISD

1.2.3. Machine MIMD

1.2.4. Machine SIMD

1.3. Machine cellulaire

1.4. Machine vectorielle

1.4.1. Pipeline

1.4.2. Pipeline d’instruction du branchement conditionnel

1.4.3. Performance du pipeline

1.5. Les machines systoliques

1.5.1. Exploitation du parallélisme de données et de flux en mode systolique

1.5.2. Architecture générale d’une machine systolique

1.6.Application d’une machine systolique pour le calcul du produit de matrices

1.6.1. modélisation analytique

1.6.1.1. Réseau systolique

1.6.1.2. Principe

1.6.1.3. Algorithme de calcul dans une cellule pendant un cycle d’horloge

1.6.1.4. Architecture systolique pour la multiplication des matrices et le fonctionnement des cellules

Chapitre 2 : Etude du système

2.1. Généralité

2.2. Etude des éléments logiques et des éléments combinatoires

2.3. MISE EN OEUVRE DES SCHEMAS

2.3.1. Schéma bloc du système

2.3.2. Fonctionnement

2.4. Circuit détaillé du bloc acquisition de données

2.4.1. Schéma

2.4.2. Fonctionnement

2.5. Architecture systolique

2.5.1. Les buffers

2.5.2. La machine cellulaire

2.5.2.1. Schéma du circuit

2.5.2.2. Le fonctionnement

2.6. Circuit détaillé du bloc transmetteur de données

2.6.1. Schéma

2.6.2. Le fonctionnement

2.7. L’unité de contrôle

2.7.1. L’unité de commande de l’acquisition de données

2.7.2. L’unité de contrôle de l’architecture systolique

2.7.3. L’unité de contrôle de transmetteur de données

2.8. Conclusion

Chapitre 3. L’architecture d’une cellule

3.1. Multiplication

3.1.1. Concept de base

3.1.2. Etudes des schémas blocs pour la multiplication

3.1.2.1. Premier version du matériel et de l’algorithme pour la multiplication

3.1.2.2. Deuxième version du matériel et de l’ algorithme pour la multiplication

3.1.2.3. Troisième version du matériel et de l’algorithme pour la multiplication

3.1.3. Le schéma détaillé du chemin des données de la multiplication

3.2. Etude de chaque composant de la multiplication

3.2.1. Additionneur complet 1 bit

3.2.1.1. Table de vérité de l’additionneur complet de 1 bit

3.2.1.2. Table de karnaugh

3.2.1.3. Additionneur complet 8 bits

3.2.2. Composant registre d’entrée de donnée (registre 8 bits)

3.2.3 : Composant registre à décalage

3.2.3.1: Registre 16 bits sans chargement

3.2.3.2. Multiplexeur à deux entrées de 8 bits

3.2.3.3. Compteur par 9

3.2.4. Composant bascule D sans initialisation

3.3. Addition

3.3.1. Additionneur de 16 bits

3.4. Conclusion

Chapitre 4 : synthèse sur FPGA

4.1. Les circuits FPGA

4.1.1. Présentation

4.1.2. Méthodologie de synthèse

4.1.3. Les circuits XILINX

4.1.4. Module XILINX spartan-3

4.2. Le langage VHDL

4.2.1. Généralité sur langage VHDL

4.2.2. Méthode de conception adoptée

4.3. Codes VHDL des composants du système

4.3.1. Code VHDL de l’inverseur

4.3.2. Code VHDL de l’opérateur AND à 2 entrées

4.3.3. Code VHDL de l’opérateur OR à 2 entrées

4.3.4. Code VHDL de L’opérateur XOR à 2 entrées

4.3.5. Code de la bascule D avec remise à zéro

4.3.6. Code VHDL d’un Module qui détecte le bit de Start

4.3.7. Code VHDL du compteur par 9

4.3.8. Code VHDL de démultiplexeur

4.3.9. Code VHDL de multiplexeur

4.3.10. Code VHDL de l’additionneur complet 1 bit

4.3.11. Code VHDL de l’additionneur complet 8 bit

4.3.12. Code source du registre à décalage (shifter)

4.3.13. Le code VHDL correspondant à la bascule D

4.3.14. Le code VHDL d’un registre 8 bits avec affectation après 8ème coups d’horloge.57

4.4. Code VHDL d’acquisition

4.4.1. Entité

4.4.2. Architecture

4.5. Code VHDL du circuit d’une cellule

4.5.1. Entité

4.5.2. Architecture

4.6. Code VHDL Datatransmitter

4.6.1. Entité

4.6.2. Architecture

Chapitre 5. Simulation et réalisation

5.1. Simulation

5.1.1. Configuration de l’horloge

5.2. Réalisation

5.2.1. Processus « Synthesize-XST »

5.2.2. Création du fichier de contrainte systorice.ucf

5.2.3. Implémentation

5.2.4. Génération du fichier de programme

5.3. Mise en oeuvre de la communication sérielle selon le protocole RS232 défini sur Spartan3

5.3.2. Broches du port séries et FPGA pins

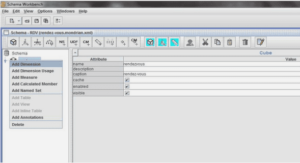

Chapitre 6 : Le logiciel SystoRice

6.1. Généralité

6.2. Les onglets

6.2.1. L’onglet « step by step »

6.2.1.1. Présentation de l’interface

6.2.1.2. Principe d’utilisation et fonctionnement

6.2.2. L’onglet « On the wing »

6.2.3. L’onglet « implementation of datums in FPGA »

Télécharger le rapport complet![]()