L’ORIGINE DE LA CONTRAINTE MECANIQUE

La contrainte mécanique est un levier technologique indispensable pour améliorer les performances des transistors CMOS. Actuellement, une large gamme de techniques permettant d’introduire et de contrôler le niveau de contrainte dans les canaux de conduction des transistors MOSFETs est apparue dans les procédés microélectroniques. La contrainte introduite par le procédé provoque une déformation du cristal, et modifie par conséquent les performances électriques.

Bref historique

Jusqu’aux années 80, la contrainte mécanique a, longtemps, été synonyme de défauts ponctuels (ex. : lacunes, impuretés) [Garros 09] ou d’étendus de dislocations dans les matériaux microélectroniques, et de délaminations de couches [Rochette 08]. Ce n’est que depuis une vingtaine d’années que les industries semiconductrices ont commencé à exploiter son influence sur la mobilité afin d’améliorer les performances des transistors MOSFETs [Thompson 02] [Ghani 03]. La contrainte modifie la structure de bande du semi-conducteur, ce qui implique à la fois une modification de l’énergie de la bande interdite ainsi qu’une levée de dégénérescences des bandes (conduction et valence), en réduisant la probabilité d’interaction entre les porteurs et les phonons

(cf. chapitre II). De manière générale, deux familles de contraintes peuvent être générées au moment de la fabrication de dispositifs MOSFETs. D’une part les contraintes mécaniques non-intentionnelles qui sont générées systématiquement tout au long des étapes de procédé. Ces contraintes mécaniques ont différentes origines, telles que le polissage mécano-chimique (connu sous le nom CMP = Chemical-Mechanical Polishing), les implantations ioniques, les recuits thermiques, les oxydations et les contraintes intrinsèques qui dépendent quant à elles des conditions du dépôt. Le deuxième type s’appuie sur les contraintes induites volontairement par le procédé de fabrication afin d’améliorer les performances de ces dispositifs, comme l’utilisation de substrat contraint : sSOI ou SiGeOI. Nous parlons alors d’ingénierie des contraintes (cf. figure I.6).

Contrainte thermique

Ce type de contrainte est responsable de la partie la plus significative des contraintes mécaniques non-intentionnelles, puisque la plupart des étapes du procédé CMOS sont suivies généralement de plusieurs cycles de recuit (ex. : dépôt d’oxyde STI). En effet, l’origine de la déformation est due à la fois à la différence entre les coefficients de dilatation thermique entre les différents matériaux et à la température.

D’un point de vue théorique, le dépôt d’un film mince (d’épaisseur faible) à une température donnée (notée T dep ) sur un substrat épais (ex. : silicium) fait apparaître des contraintes mécaniques dans le film lors du retour à la température ambiante (T amb ). La déformation du film (supposé libre) dans le plan (notée ? ? ) correspond au produit de son coefficient de dilatation thermique α f avec l’écart de température ΔT (T dep − T amb ). Systématiquement, la déformation du substrat supposé libre (notée ici ? ? ) peut s’écrire : ε s = α s × ΔT (I.18) avec α s le coefficient de dilatation thermique du substrat.

En raison de l’épaisseur très élevée du substrat, le film déposé n’est toutefois pas libre de se relaxer, on dit que le substrat impose sa rigidité (figure I.7). Cela entraîne une déformation résiduelle dans le film, qui est la différence entre la déformation du film et celle du substrat (ε f − ε s ). En appliquant la loi de Hooke, nous pouvons remonter à l’état de contrainte.

EXEMPLES D’INTEGRATION DE LA CONTRAINTE DANS LE CANAL DES DISPOSITIFS AVANCES

En microélectronique, différents procédés ont été utilisés afin de contraindre le canal des transistors MOS et d’améliorer par conséquent le gain sur le courant. D’un point de vue microscopique, une contrainte mécanique modifie directement la structure de bandes conduction/valence. Cela entraine un décalage énergétique de ces bandes en fonction de la nature de la contrainte appliquée (ex. : hydrostatique, déviatrice), une modification du peuplement de porteurs et une variation de la masse effective. En général, nous pouvons classer en deux catégories distinctes les techniques permettant d’introduire une contrainte contrôlée dans le canal. La première dite globale, repose sur l’épitaxie des canaux contraints, où l’ensemble du substrat est uniformément contraint. La seconde catégorie est une méthode locale basée sur les contraintes induites par le procédé de fabrication.

Techniques largement utilisées en microélectronique

Comme nous pouvons le constater, les contraintes mécaniques sont omniprésentes dans la physique des semi-conducteurs, mais leur exploitation reste quelque chose de très récent en technologie CMOS. La société Intel est la première entreprise qui a pu produire des transistors MOSFETs contraints pour le nœud 90nm [Ghani 03]. Comme nous pouvons le voir sur la figure I.9, ces contraintes ont des origines mécaniques très différentes. Dans le cas des transistors nMOS, un paramètre clé de l’amélioration des performances une couche de nitrure SiN en tension est à l’origine de la contrainte dans le canal, tandis que le canal est mis en compression par des S/D en SiGe dans le cas pMOS.

Dans la suite de ce paragraphe, nous donnons une liste des principales techniques précédemment ou récemment utilisées dans les technologies CMOS. Notons que nous aurons l’occasion d’évaluer aux chapitres III et IV certaines de ces méthodes par le biais de la simulation TCAD.

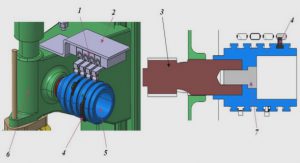

Contraintes induites par les régions S/D

Parmi les plus anciennes méthodes pour introduire une contrainte contrôlée dans un procédé CMOS et améliorer la mobilité des trous figure la méthode des S/D surélevés en SiGe (figure I.9). L’objectif de cette technique consiste à contraindre localement le canal d’un transistor pMOS via la relaxation de zones S/D intrinsèquement contraintes en compression. En raison de la miniaturisation progressive des dispositifs microélectroniques, l’espacement entre la source et le drain ne cesse de baisser. C’est la raison pour laquelle la concentration en Ge dans ces zones épitaxiées augmente afin de conserver un niveau de contrainte bénéfique pour le transport des porteurs [Kuhn 12] [Coquand 13a]. Ce point en particulier sera abordé pour le cas du FDSOI dans le chapitre IV.

SAIPS

Une méthode récemment utilisée (similaire à celle présentée précédemment au paragraphe §I.3.1.1) est la technique SAIPS (= Self-Aligned In-Plane Stressors). Comme l’indique la figure I.16, avant l’étape d’épitaxie S/D, le principe de cette méthode consiste à augmenter davantage la concentration en germanium par procédé de condensation [Tezuka 01] dans le film SiGe côté S/D du pMOSFET. L’un des avantages de cette technique est le transfert optimal de la contrainte depuis la zone SAIPS au canal.

LES TECHNIQUES D’ANALYSE DE CONTRAINTES

Ce paragraphe a pour but de rappeler dans un premier temps les différentes techniques de mesures permettant de déterminer le niveau de déformation dans les canaux des transistors étudiés. Nous donnerons le principe des techniques NBED (= Nano-Beam Electron diffraction) et PED (= Precession Electron Diffraction) qui sont utilisées dans le laboratoire LCTE du LETI avec lequel nous avons collaboré, l’objectif étant d’avoir accès à des mesures de contraintes qui nous permettent de valider les résultats que nous avons obtenus par simulation. Le dernier paragraphe positionnera les outils de simulation, par éléments finis, que nous avons utilisés dans cette thèse.

Techniques de mesures de déformation

Le contrôle et la mesure de la contrainte mécanique dans un transistor à effet de champ se font généralement par plusieurs techniques et elles permettent toutes de renseigner sur l’état de déformation dans le canal. De manière générale, le choix de la méthode dépend de l’échantillon à disposition, de la résolution et de la sensibilité souhaitée. Nous pouvons classer ces techniques en deux catégories distinctes. D’une part, celles hors microscopie électronique, à titre d’exemple la diffraction de rayons X et la technique Raman, et d’autre part, les mesures de déformation par microscopie électronique. Dans cette étude, nous allons nous focaliser uniquement sur la méthode de diffraction en faisceaux parallèles (NBED) ainsi que celle en précession (PED). Le lecteur souhaitant connaître plus en détails les autres techniques utilisées permettant de mesurer l’état de déformation du canal, est invité à se référer à ces articles [Boureau 15] [Eggemann 13] [Rouvière 05] [Vigouroux 14].

Diffraction électronique en faisceaux nanométriques : NBED

Les méthodes de caractérisation basées sur les techniques TEM (= Transmission Electron Microscopy) sont de plus en plus courantes dans la microélectronique [Toda 08] [Favia 11], notamment la technique de diffraction en faisceaux parallèles (NBED). Son principe repose sur l’illumination d’un échantillon avec un faisceau d’électrons quasi-parallèle dont le diamètre de la sonde (noté d) est inférieur à la dizaine de nanomètres (figure I.18). Le cliché de diffraction obtenu (ex. : figure I.20.a et I.20.b) se compose de diverses taches de faibles diamètres, par lesquelles l’accès direct aux informations locales du cristal est possible.

L’utilisation du NBED en microélectronique porte généralement sur la détermination de phases cristallines et les orientations des matériaux caractérisés d’une part [Liu 05] [Alloyeau 08] ; d’autre part sur la mesure de déformation [Usuda 03], en déterminant le déplacement atomique du réseau.

Techniques de simulation

Après avoir montré comment l’état de déformation peut être expérimentalement mesurée dans un matériau ou dispositif contraint, il est temps de présenter d’autres méthodes d’analyse basées principalement sur la simulation numérique pour évaluer l’impact des contraintes mécaniques sur laperformance électrique des transistors avancés. En effet, nous pouvons diviser de façon très schématique la simulation numérique en plusieurs parties (figure I.21) : les simulations numériques avancées qui sont indispensables pour étudier les phénomènes physiques complexes, nécessitant une grande précision de calculs ; la simulation numérique des dispositifs microélectroniques (ex. : TCAD) qui est nécessaire au développement et à la prédiction des performances des dispositifs CMOS ; les simulations des circuits électroniques qui peuvent être étudiés via des simulations de type analytique/compacte (ex. : SPICE).

Principe de fonctionnement

Pour le fonctionnement d’un transistor MOS, deux régimes disctincts sont considérés. A faible polarisation du drain VD, le transistor se comporte comme une résistance régie par la grille.

Il s’agit ici d’un régime ohmique largement exploité par les différentes techniques d’extraction de mobilité, du fait que la résistance est proportionnelle à la mobilité. En revanche, à fort VD (régime de saturation), on parle d’un transistor en source de courant commandé idéalement par la grille. La caractéristique de transfert de la figure II.2 décrit la variation du courant de drain en fonction de la polarisation de grille en échelle logarithmique. Le transistor est donc commandé par la tension de grille (notée VG) influant le nombre de porteurs dans le canal (il s’agit ici des électrons). Pour une tension VD supérieure à 0, nous parlons « d’état bloqué » quand la tension VG est inférieure à la tension de seuil VT et « d’état passant » quand celle-ci est supérieure à VT. La tension de seuil VT représente le passage de l’état bloqué à l’état passant alors que la polarisation de drain VDD représente la tension d’alimentation. Les performances des transistors MOSFET sont généralement définies par le ratio entre le courant ION (courant de drain pour VG=VDD) et le courant IOFF (courant de drain pour VG=0V). Ainsi, la pente sous le seuil SS correspond quant à elle à l’augmentation nécessaire de la tension appliquée sur la grille VG pour augmenter le courant de drain ID d’une décade. Cela montre que plus le SS sera faible, meilleure sera la sensibilité du transistor à la commande.

Régimes de fonctionnement

Il existe différents régimes de fonctionnement électrique d’un MOSFET selon la polarisation de grille tels que le régime sous le seuil, le régime d’inversion faible et celui de forte inversion. Le dernier régime sera le sujet de la suite de cette étude, de façon à retrouver l’équation du courant associée au drain (ID) à l’état passant. Ici, nous allons commencer par décrire le diagramme de bandes, afin de retrouver l’origine de ces régimes. La figure II.3 présente le diagramme de bandes du transistor MOS. EFM et EF correspondent respectivement au niveau de Fermi du métal et du silicium. V est l’écart entre les quasi-niveaux de Fermi et correspond à la polarisation extérieure appliquée sur la grille, et Ψ(y) est le potentiel de surface à l’abscisse y.

|

Table des matières

LISTE DES NOTATIONS ET DES ACRONYMES

INTRODUCTION GENERALE

CHAPITRE I

LA CONTRAINTE MECANIQUE EN MICROELECTRONIQUE : UN PARAMETRE CLE DE L’AMELIORATION DES PERFORMANCES

I.1. PROPRIETES DES MATERIAUX EN MICROELECTRONIQUE D’UN POINT DE VUE MECANIQUE

I.1.1. Propriétés d’élasticité du silicium

I.1.1.1. Tenseurs des contraintes et des déformations

I.1.1.2. Tenseur d’élasticité du silicium

I.1.2. Le comportement viscoélastique des matériaux

I.1.2.1. L’élément de Maxwell

I.1.2.2. L’élément de Kelvin-Voigt

I.1.2.3. L’élément de Zener

I.1.3. Piézo-résistivité dans les semi-conducteurs

I.2. L’ORIGINE DE LA CONTRAINTE MECANIQUE

I.2.1. Bref historique

I.2.2. Contrainte thermique

I.2.3. Contrainte intentionnelle

I.3. EXEMPLES D’INTEGRATION DE LA CONTRAINTE DANS LE CANAL DES DISPOSITIFS AVANCES

I.3.1. Techniques largement utilisées en microélectronique

I.3.1.1. Contraintes induites par les régions S/D

I.3.1.2. Couche contrainte d’arrêt à la gravure : CESL

I.3.1.3. Substrat contraint

I.3.2. Techniques alternatives récemment intégrées en procédé

I.3.2.1. BOX CREEP

I.3.2.2. STRASS

I.3.2.3. SAIPS

I.3.3. Bilan

I.4. LES TECHNIQUES D’ANALYSE DE CONTRAINTES

I.4.1. Techniques de mesures de déformation

I.4.1.1. Diffraction électronique en faisceaux nanométriques : NBED

I.4.1.2. Diffraction électronique en précession : PED

I.4.2. Techniques de simulation

I.5. OBJECTIF DE L’ETUDE

CHAPITRE II

EXTRACTION DE MOBILITE – METHODES CLASSIQUES ET MAGNETORESISTANCE

II.1. PRINCIPE D’EXTRACTION DE MOBILITE

II.1.1. Modèle analytique simplifié

II.1.1.1. Modèle Dérive-Diffusion

II.1.1.2. Structure MOS classique

II.1.1.3. Principe de fonctionnement

II.1.1.4. Régimes de fonctionnement

II.1.1.5. Courant de drain en régime d’inversion forte

II.1.2. Notion de mobilité

II.1.2.1. Mobilité phonon

II.1.2.2. Mobilité coulombienne

II.1.2.3. Mobilité surface rugueuse

II.2. METHODES DE CARACTERISATION ET METHODOLOGIES D’EXTRACTION

II.2.1. Technique dite de « Split-CV »

II.2.2. Fonction Y

II.2.2.1. Modèle

II.2.2.2. Méthode

II.2.2.3. Prise en compte de résistances séries par la méthode de la fonction Y

II.2.3. Mobilité magnétorésistance

II.2.3.1. L’effet Hall

II.2.3.2. L’effet magnétorésistance

II.2.3.3. Application aux dispositifs MOS

II.3. MAGNETORESISTANCE : CARACTERISATION ET MODELISATION

II.3.1. Descriptions expérimentales

II.3.2. Mesures et extraction de la mobilité µGMR dans les transistors à triple grille

II.3.2.1. Mesures préliminaires

II.3.2.2. Mesures de la mobilité magnétorésistance

II.3.3. Modélisation tridimensionnelle de la mobilité magnétorésistance

II.3.3.1. Approche classique

II.3.3.2. Implémentation FlexPDE

II.3.3.3. Résultats de simulation

II.4. CONCLUSION DU CHAPITRE II

CHAPITRE III

EVALUATION DU TRANSPORT DANS LES TRANSISTORS NMOS A TRIPLE-GRILLE SUR SUBSTRATS (S)SOI

III.1. ANALYSE MECANIQUE VIA DES SIMULATIONS PAR ELEMENTS FINIS

III.1.1. Le transistor nMOS à triple grille

III.1.2. Description de la simulation mécanique

III.1.1.2.1. Procédé et paramètres de simulation

III.1.2.1.a. Constitution du substrat SOI

III.1.2.1.b. Préparation de la zone active

III.1.2.1.c. Dépôt et gravure de la grille

III.1.2.1.d. Epitaxies S/D

III.1.2.1.e. Dépôt de t-CESL

III.1.2.2. Hypothèses de simulation

III.1.3. Champs de contraintes issus de la simulation mécanique

III.1.3.1. Cas des transistors FDSOI

III.1.3.2. Cas des transistors TriGate

III.1.4. Comparaison des contraintes entre la TCAD et les mesures NBED

III.1.5. Synthèse

III.1.5.1. Influence des substrats en sSi sur le niveau de contrainte du canal

III.1.5.2. Influence de CESL

III.1.5.3. Dégradation de la contrainte avec la couche TiN

III.2. EXTRACTIONS DE MOBILITE

III.2.1. Extraction de la mobilité à champ faible

III.2.1.1. Description des mesures à faible VD

III.2.1.1.a. Mesures des dispositifs FDSOI

III.2.1.1.b. Mesures des dispositifs TriGate

III.2.1.2. Longueurs et largeurs effectives

III.2.1.2.a. La longueur effective « Leff »

III.2.1.2.b. La largeur effective « Weff »

III.2.1.3. Etude expérimentale de la mobilité dans les canaux contraints

III.2.1.3.a. Description de la méthode de la fonction Y

III.2.1.3.b. Extraction de la mobilité à champ faible

III.2.1.3.c. Analyse et synthèse

III.2.2. Extraction de la mobilité via une approche de type BSIM

III.2.2.1. Description de la méthode

III.2.2.1.a. Le modèle analytique

III.2.2.1.b. Stratégie d’extraction des paramètres

III.2.2.1.c. Extraction de RSD et μ=f(Q) via la modélisation proposée

III.2.2.2. Etude du transport dans les dispositifs nMOS via la modélisation de type BSIM

III.2.2.2.a. Impact de la longueur de grille : cas FDSOI

III.2.2.2.b. Impact de la largeur de grille : cas TriGate

III.2.2.3. Bilan

III.3. ANALYSE APPROFONDIE DE LA VARIATION DE MOBILITE DUE A LA CONTRAINTE

III.3.1. Prédiction de l’influence de la contrainte sur la mobilité

III.3.1.1. Coefficients piézorésistifs

III.3.1.2. Application aux transistors à triple grille

III.3.2. Décorrélation des mécanismes d’interactions limitant la mobilité par étude en température

III.3.2.1. Analyse de la mobilité des transistors courts

III.3.2.2. Analyse de la mobilité dans les dispositifs étroits

III.4 CONCLUSION DU CHAPITRE III

CHAPITRE IV

ETUDE DE L’IMPACT DE DIFFERENTES SOLUTIONS D’INGENIERIES DE CONTRAINTE SUR LES PERFORMANCES DES TRANSISTORS FDSOI

IV.1. PRESENTATION DE L’ARCHITECTURE 14NM FDSOI

IV.1.1. Contexte de l’étude

IV.1.2. Simulation mécanique du procédé de fabrication

IV.1.3. Hypothèses et paramètres de simulation

IV.1.4. Niveaux de contraintes dans le transistor 14nm

IV.2. COMPARAISON DES DIFFERENTES TECHNIQUES D’INGENIERIE DE CONTRAINTES

IV.2.1. Intégration « Gate-First »

IV.2.1.1. Evaluation de l’impact de la grille métallique

IV.2.1.2. Impact des S/D surélevés

IV.2.2. Intégration « Gate-Last »

IV.2.3. La technique SAIPS

IV.2.4. Effets induits par l’isolation STI

IV.2.4.1. Définition du problème

IV.2.4.2. Gain apporté par les S/D

IV.2.5. Synthèse

IV.3. CONSEQUENCES SUR LES PERFORMANCES ELECTRIQUES

IV.3.1. Procédé de simulation électrique

IV.3.2. Cas des dispositifs périodiques

IV.3.2.1. Influence de la longueur de grille

IV.3.2.2. Influence de l’épaisseur de l’épitaxie S/D

IV.3.2.3. Influence des zones SAIPS

IV.3.2.4. Influence de l’intégration « Gate-Last »

IV.3.3. Cas des dispositifs isolés

IV.3.3.1. Influence de la couche d’oxyde STI (STIH)

IV.3.3.2. Influence de la contrainte résiduelle dans la couche TiN

IV.3.3.3. Cas d’une simulation viscoélastique

IV.4. CONCLUSION DU CHAPITRE IV

CONCLUSION GENERALE

BILAN GENERAL

PERSPECTIVES

ANNEXE

REFERENCES

LISTE DES PUBLICATIONS