Télécharger le fichier pdf d’un mémoire de fin d’études

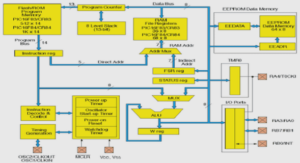

Le procédé SIMOX

Le procédé SIMOX (pourSeparation by IMplantation of OXygen) consiste à effectuer une implantation d’oxygène à haute dose (10 17 à 10 18 cm-2) dans le silicium puis un recuit à haute température pour former la couche d’oxyde enterré [17]. L’épaisseur de la couche d’oxyde ainsi obtenue est d’environ 50 nm, ce qui e st suffisant pour les composants CMOS. Cette technique a l’inconvénient de dégrader le réseau cristallin du silicium à cause de l’implantation d’oxygène, nécessitant donc le recuit à très haute température (1250 à 1400° C) pendant plusieurs heures pour réorganiser le réseaucristallin du silicium. Or, ce recuit à haute température nécessite des fours spécifiques.

Les procédés basés sur le collage de wafers

Les différentes techniques par collage utilisent les forces de Van der Waals pour faire adhérer deux plaquettes. Les atomes des deux surfaces placées très proches l’une de l’autre se lient par interaction électrique. Ensuite, un recuit à haute température (1100 °C) permet de créer le collage des deux plaquettes en augmentant l’énergie de liaison entre les atomes [18]. Les techniques ELTRAN™ et de S mart Cut™, développées par Canon et SOITEC respectivement, utilisent le collage pour réaliserles substrats SOI.

Implantation d’oxygène : procédéSmart Cut™

Le procédé Smart Cut™ fut développé au LETI avant d’être commercialisé[ 19]. Il consiste à implanter, sur une plaquette précédemment oxydée, des ions hydrogène à une dose

16 -2 supérieure à 5 10 cm . Ces ions vont créer des microcavités dans le silicium. Cette plaquette est collée sur une autre, elle aussi oxydée, qui servira de support mécanique. Un premier recuit entre 400 et 600° C va séparer la première plaquette au niveau du maximum de concentration d’hydrogène et un deuxième à plus haute température va renforcer la liaison du collage. Après polissage, la deuxième plaquette devient le substrat SOI. La première est réutilisée pour un nouveau procédé. La figure I-ésume7r ce procédé.

Procédé basé sur le silicium poreuxELTRAN:™

Le procédé ELTRAN™ ( Epitaxial Layer TRANsfer) utilise les propriétés du silicium poreux [20] [21]. Deux couches de silicium poreux sont réalisées urs un premier wafer. Comme le silicium poreux garde ses propriétés cristallines, il est possible de faire croître une couche de silicium épitaxiée sur laquelle est réalisé un oxyde thermique. Cette plaquette est collée sur une deuxième servant de support, qui a préalablement été oxydée. Comme le silicium poreux est mécaniquement plus fragile, lesdeux plaquettes se séparent à l’interface des deux couches de silicium poreux à partir, par e xemple, d’un jet d’eau. Nous obtenons, après retrait de la couche de silicium poreux, un substrat SOI. De plus, la première plaquette peut ensuite être réutilisée pour un nouveau procédELTRAN™. La figure I-8 résume le procédé ELTRAN™.

Ces deux techniques sont assez proches l’une de l’a utre. Le procédé Smart Cut™ , bien que moins coûteux puisqu’il nécessite moins d’étapes, ne permet d’obtenir que des épaisseurs de silicium plus faibles (jusqu’à 2 µm) qu’avec le procédé ELTRAN™ , puisqu’elles sont + limitées par l’énergie d’implantation des protons H (70 keV). Cependant, le contrôle de l’épaisseur est plus précis car cette dernière dépend de l’énergie de l’implantation. Dans le cas du procédé ALTRAN™, l’épaisseur de silicium est conditionnée par l’épaisseur de l’épitaxie. Dans les deux procédés, le wafer sur lequel est réalisée la couche de silicium active est réutilisé pour un autre procédé, ce qui minimise surcoûtle.

La description de ces différentes méthodes de réalisation d’un substrat SOI permet de comprendre le prix plus élevé de ces plaquettes. Cependant, les techniques de réalisation par collage, moins complexes que la technique SIMOX, tendent à faire baisser le prix des wafers, et, au final, celui des composants.

La technologie d’isolation par diélectrique est mieux adaptée pour l’utilisation à haute température [22], et, plus principalement, les transistors MOS totalement dépeuplés (« fully depleted ») qui sont toujours opérationnels à 300° C [16], car elle supprime les courants de fuites inhérents aux technologies d’isolation par jonction et permet une isolation totale entre les dispositifs, ce qui en fait un excellent candidat pour les technologies de circuits intégrés de puissance à hautes performances. Un autre point en faveur de l’isolation par diélectrique est le gain en surface de silicium apporté par les tranchées latérales, contrairement aux puits P qui, eux, nécessitent pour leur réalisation des temps dediffusion longs et donc des diffusions latérales importantes.

Les composants de puissance dans les circuits intégrés

L’utilisation des composants de puissance

En électronique de puissance, les composants de puissance sont destinés à des fonctions d’interrupteurs dans la mise en œuvre de convertisseurs (hacheurs, onduleurs, etc). Nous pouvons citer les principaux montages où ces composants sont utilisés : transistor en configuration basse (Figure I-9 (a)), en configuration haute (Figure I-9 (b)), demi-pont et pont en H.

Dans les circuits intégrés de puissance, il est possible d’intégrer plusieurs composants de puissance isolés les uns des autres pour la réalisation de ces circuits.

Les interrupteurs de puissance fonctionnent entre deux états : l’état passant et l’état bloqué. À l’état bloqué, l’interrupteur est ouvert, la tension supportée à ses bornes est importante et le courant le traversant nul. Le composant est caractérisé par sa tenue en tension (BVds), qui est la tension qu’il peut supporter entre ses bornes avant destruction. À l’inverse, quand l’interrupteur est passant, la chute de tension à ses bornes doit être la plus faible possible quand il est traversé par un courant important. Sachant que certains convertisseurs fonctionnent à des fréquences de plusieurs kHz, il est nécessaire que l’interrupteur change d’état le plus rapidement possible afin de limiter les pertes lors des commutations.

Il existe de nombreuses familles de composants semi-conducteurs pouvant réaliser cette fonction, chacune étant mieux adaptée à certaines applications, comme nous allons le voir par la suite.

Les composants de puissance

Il existe de nombreuses familles de composants à se mi-conducteur pouvant réaliser la fonction d’interrupteur de puissance. Dans les circuits intégrés de puissance, et plus particulièrement en technologie BCD, cette fonction est réalisée par des transistors DMOS en raison de sa compatibilité de fabrication avec les procédés CMOS. Cependant, des composants de type bipolaire ont déjà été utiliséspour réaliser cette fonction, mais ils sont source de perturbations en raison de l’injection de porteurs dans le substrat qu’ils engendrent et qui peut causer des problèmes de latch-up [23].

Le transistor LDMOS

C’est un peu à cause de ces problèmes mais aussi gr âce à leur plus grande vitesse de commutation que les transistors MOS ont fait l’objet de nombreuses attentions. Le transistor LDMOS [24] pour Lateral Double Diffused Metal Oxide Semiconductor, dont une coupe schématique est représentée figure I-11, est communément utilisé dans les circuits intégrés de puissance. La particularité de cette structure provient du chemin latéral qu’emprunte le courant. Une région N, dite de drift, est intercalée entre la grille etle drain.

Les composants de puissance nécessitent une régionpeu dopée permettant de tenir la tension. Cette région étant faiblement dopée, celasignifie que sa résistivité sera importante. Sur le transistor LDMOS de la figure I-11, la région N-drift supporte la tension appliquée entre l’ensemble « source / grille » et le drain. Nous allons maintenant détailler les deux régimes de fonctionnement : bloqué et passant.

Fonctionnement à l’état passant

À l’état passant, le transistor LDMOS est caractérisé par sa résistance passante. Celle-ci se mesure à tension de grille ( VGS) donnée et à faible tension de drain (VDS). La résistance du transistor se décompose en plusieurs résistancesen série correspondant aux résistances des différentes régions. Nous ne retiendrons que les résistances qui pèsent le plus sur la résistance totale : la résistance du canal (Rch), la résistance d’accès R(a) et la résistance de drift (Rd). Les + autres résistances qui sont celles des diffusions N et de métallisation sont négligeables (de l’ordre du m).

La résistance de canal correspond à la zone d’inversion de la région P-well sous la grille. Sa valeur dépend principalement de la tension de grille appliquée, du dopage en surface du P-well, de la longueur Lch du canal et de l’épaisseur de l’oxyde de grille.

La résistance d’accès représente l’accumulation sou la grille en surface de la région de drift. Cette résistance dépend des mêmes paramètres que la résistance Rch qui sont la tension de grille, la longueur du débordement de lagrille sur la région N, du dopage de cette dernière et l’épaisseur de l’oxyde de grille.

La résistance de drift Rd correspond à la zone N – drain N+. Cette résistance peut être considérée située entre la fin de la grille et le comme un rreauba semi-conducteur ( R l ), de résistivité 1 , de longueur Ld et de surface S h Z , où h est la qn N D S profondeur de la section de conduction du courant de drain qui peut être approximée à + l’épaisseur de la région N de drain [25], ce qui donne : Rd Ld Équat ion I-3 qn N D h Z.

Pour réduire la résistance totale, il suffirait d’augmenter en théorie la taille du transistor (la valeur Z) pour obtenir la valeur de résistance voulue. Cependant, le transistor présenterait alors une surface trop importante. Ilest donc plus pertinent de parler de résistance passante spécifique, qui est le produit de la résistance à l’état passant par la surface active : Ron.S ou Ron-sp..

Les protections en fin de grille

Une technique couramment utilisée est l’ajout de plaques de champ qui sont généralement des prolongations du polysilicium de rilleg. Or, dans les composants LDMOS, le claquage peut avoir lieu en fin de grille (Cf. figure I-13) à cause de l’oxyde fin de la grille qui est exposé à une forte différence de potentiel et à un fort champ électrique. Ce point critique doit être protégé afin d’améliorer la tenuen tension. L’ajout d’un oxyde épais est la meilleure protection et la plus utilisée puisque lechamp électrique critique de l’oxyde est très supérieur à celui du silicium. Il existe plusieurs méthodes pour réaliser cette protection.

Protection par oxyde de champ

Les transistors LDMOS discrets, c’est-à-dire non in corporés dans un circuit intégré, sont fabriqués à partir d’un procédé moins contraignant que ceux réalisés dans des circuits intégrés de puissance. Il est donc possible de réaliser la grille après le dépôt de l’oxyde de champ, permettant d’obtenir la structure représenté figure I-22 [33] [40].

Avec cette technique, il est possible d’obtenir des tenues en tension dépassant 1000 V avec des épaisseurs d’oxyde de 3 µm. La prolongation du polysilicium au dessus de la région de drift joue un rôle de plaque de champ, ce qui pe rmet à l’état bloqué de repousser les lignes de potentiel loin de la source, améliorant ainsi latenue en tension.

Oxydation LOCOS

L’oxydation LOCOS (LOCalized OXidation) a longtemps été utilisée comme oxyde de champ dans les circuits intégrés de puissance. Cette étape d’oxydation est utilisée dans les procédés CMOS de résolution supérieure à 0,35 µm pour isoler les composants les uns des autres puisque cet oxyde « pénètre » dans le silicium. Cette oxydation localisée se fait par croissance sélective de l’oxyde dans les zones non protégées par du nitrure de silicium. À la fin du processus, un soulèvement du masque formé par la couche de nitrure est observé : on obtient à cet endroit un oxyde en forme de bec d’oi seau (figure I-23).

Cette méthode a donc été utilisée pour définir l’oxyde de champ des transistors LDMOS compatibles avec les anciennes générations deprocédés CMOS 41[] [42] [43], puisque l’étape d’oxydation LOCOS est réalisée en ébutd de fabrication, ce qui permet de déposer le polysilicium de grille au dessus de l’oxyde LOCOS (figure I-24).

Dans cette structure, si l’oxyde de champ est trop proche du P-well, la résistance passante peut fortement augmenter à cause du resser rement des lignes de courant à la fin du canal. A l’inverse, un trop grand éloignement réduit l’efficacité de la plaque de champ provoquant ainsi la rupture sous la grille.

La réduction de la lithographie dans les technologies CMOS a fait que l’oxydation LOCOS n’était plus adaptée puisqu’elle consommait une surface importante de silicium à cause de l’extension latérale de l’oxyde et créait du stress mécanique au niveau du bec d’oiseau [ 44].

Protection par STI et transistors LUDMOS

Dans les technologies CMOS actuelles, l’oxydation LOCOS a été remplacée par l’isolation par tranchée STI (Shallow Trench Isolation) qui est plus précise et moins consommatrice de surface. Cette technique d’isolation est utilisée pour les technologies CMOS de lithographie de 0,25 µm et inférieures.

Bien avant l’essor des technologies CMOS submicroniques, l’utilisation d’une tranchée en fin de grille dans les transistors LDMOS avait déjà montré son efficacité 45[]. Cette structure, portant le nom de LUDMOS (U pour la forme de la tranchée), est représentée figure I-25.

Dans les technologies de circuits intégrés de puissance utilisant des dernières générations de technologies CMOS, l’oxyde de champest réalisé par STI 46[] [47] [48]. Tout comme pour l’oxydation LOCOS, le bon positionnement du STI est primordial tant au niveau de la résistance passante que de la tenue en tension.

La précision de l’isolation par STI a rendu possible la création de nouvelles structures. Le concept de transistors LDMOS utilisant un diélectrique dans la région de drift, associé à une plaque de champ, qui est une prolongation du polysilicium de grille, est une alternative au 3D RESURF. Dans ce type de structure, l’effet de champ créé par la plaque de champ permet une extension de la charge d’espace dans la région de drift dans la troisième dimension, permettant ainsi d’augmenter le dopage de la région de drift, et donc d’améliorer la résistance à l’état passant (figure I-26) [49] [50].

Contrairement au transistor à superjonction où la b alance des charges entre les piliers est critique, les caractéristiques de cette structure (largeur et dopage) dépendent principalement de la configuration de la région N de drift, mais aussi de celle de la plaque de champ.

Ces techniques de protection de la grille, combinées avec les technologies RESURF ou ses variantes, permettent d’améliorer le compromis entre résistance passante spécifique et tenue en tension tant recherché par les concepteurs.

Les transistors LDMOS sur SOI

Dans les circuits intégrés de puissance, l’isolation par diélectrique est la mieux appropriée pour intégrer sur une même puce des dispositifs de calibres en tension très différents. Les composants de puissance réalisés sur substrat SOI ne s’adaptent pas forcement aux techniques développées sur substrat massif.

Technologie RESURF sur SOI

Sur substrat massif, l’effet RESURF était obtenu grâce à une jonction PN horizontale polarisée en inverse entre le substrat et la régionde drift pour créer la déplétion verticale à l’état bloqué. Dans les transistors LDMOS réaliséssur SOI (figure I-27), l’extension de la charge d’espace est obtenue par l’effet de champ d u substrat [51].

L’oxyde enterré est un paramètre supplémentaire limitant la tenue en tension. En effet, quand le couple épaisseur – dopage de la région dedrift est bien choisi, le champ électrique est uniforme dans cette dernière et le claquage apparaît aux pics de la figure I-15. La tenue en tension est donc proportionnelle à la longueur. On en déduit la relation [52] : BVDS [horizontal] Ec Ld Équation I-14.

Or, du fait de la continuité du déplacement électrique à l’interface entre l’oxyde enterré et le silicium actif, le claquage peut avoir lieu verticalement. Cette tenue en tension est donnée par : BV DS [vertical] E ( TSi Si T ) Équation I-15

Une autre approche utilisant l’intégrale d’ionisation donne une expression différente de la tenue en tension horizontale [53]. BVDS [horizontal] B Ld Équation I-16

Où A et B sont des coefficients constants. La tenue en tension réelle du composant est la plus petite valeur entre les tensions de claquage verticale et horizontale. De ces relations, on déduit que la tenue en tension est limitée par la ongueurl de la région de drift, mais aussi par les épaisseurs de l’oxyde enterré et du silicium.

Pour accroître la tenue en tension, il est possible d’augmenter soit l’épaisseur de l’oxyde enterré, soit celle du silicium actif. Cependant, l’augmentation de l’épaisseur du silicium induit une réduction du dopage de la région de drift puisque la relation T N D 11012 cm2 est toujours valable. RéduireND entrainera donc une augmentation de epi la résistance passante spécifique puisque la surface de conduction ne sera pas forcément supérieure, la conduction se faisant principalement en surface, comme cela l’a déjà été expliqué précédemment.

Les techniques RESURF « améliorées » sont aussi applicables sur SOI. Nous ne développerons pas d’avantage ce sujet puisque le principe est le même.

Superjonctions sur SOI

Le principe des superjonctions est lui aussi applicable sur SOI [54]. Si le substrat est suffisamment fin, il est possible de réaliser les piliers jusqu’à l’oxyde enterré.

Comme pour les structures à superjonction sur subst rat massif, les transistors LDMOS à superjonction sur SOI subissent l’effet du substr at comme ceux réalisés sur substrat massif.

Présentation des différentes structures

Conditions du procédé

L’isolation par diélectrique est la technique choisie pour séparer les différents étages du circuit intégré de puissance, ce qui signifie que les composants seront réalisés sur un substrat de type silicium sur isolant ou SOI. Dans le procédé standard utilisé par ATMEL, les caractéristiques du substrat sont les suivantes :

– Silicium actif dopé bore (type P), de concentration 11015 cm-3 et d’épaisseur TSOI = 1,6 µm.

– Oxyde enterré d’épaisseurTBOX = 1 µm.

– Substrat de support dopé phosphore (type N) de concentration 51016 cm-3.

Les transistors LDMOS développés par la suite seront basés sur ces caractéristiques.

Description des structures étudiées

Dans ce chapitre nous étudierons trois structures LDMOS différentes mais compatibles avec le procédé de fabrication. La première structure est un transistor LDMOS RESURF conventionnel. La seconde est identique à la précédente à l’exception de la présence d’une tranchée peu profonde de type STI en fin de grille. La troisième structure utilise le principe de la superjonction : la région N de driftest remplacée par une alternance de bandes P et N. Les coupes schématiques des trois structure sont représentées figure II-1.

Partant du procédé CMOS 0,18 µm standard d’ATMEL, une partie des dimensions et des dopages fixe. Les dimensions fixées par le procédé sont, en plus des caractéristiques du substrat citées précédemment, les dopages des régions P-well, du N+ de source et de drain, identique pour les deux diffusions, du P+ de source et du polysilicium de grille, mais aussi la profondeur de la tranchée (TSTI), fixée à la valeur de 0,46 µm ainsi que les épaisseurs des oxydes, dont celle de l’oxyde de grille égale à 7 nm car identique à celle des transistors CMOS 3,3 V. Les principaux paramètres du LDMOS RESURF (Figure II-1 (a)) sont la longueur du polysilicium de grille (LPoly), la longueur de la région de drift (LLDD) définie entre la fin du polysilicium et la région N de drain. Dans cette structure en particulier, la métallisation de source a été prolongée au-delà dupolysilicium de grille d’une longueur LSFP, dans le but d’améliorer la répartition du champ électrique en fin de grille [55]. Le transistor LDMOS RESURF avec STI, ou STI-LDMOS, est caractérisé par la position du STI par rapport à la source ( Lc), sa longueur (LSTI), le débordement du polysilicium de grille au dessus de celui-ci (LPoly) et la longueur de la région de drift (LLDD) comprise entre le début du STI + et la région N de drain. Le transistor LDMOS à superjonction ou S J-LDMOS possède les mêmes caractéristiques que la structure STI-LDMOS.Les paramètres supplémentaires de cette structure sont la longueur des piliers de la superjonction non recouverts par le STI (LSJ) et leurs largeurs (YNpi et YPpi).

L’optimisation des transistors LDMOS présentés se eraf par l’étude des paramètres cités précédemment ainsi que par l’étude des dopages des régions N de drift pour le cas des transistors RESURF et des piliers P et N dans le cas du transistor à superjonction, car ces régions seront réalisées par des masques spécialement dédiés aux composants de puissance (Cf. chapitre 4).

Optimisation du compromis « résistance passante spécifique – tenue en tension »

Dans cette partie, nous allons chercher les meilleures combinaisons des paramètres cités précédemment afin d’obtenir, pour une tenue ne tension de 150 V, afin d’assurer les 120 V du cahier des charges, la plus faible résistance passante spécifique. Dans un premier temps, nous travaillerons sur les structures LDMOS RESURF à partir de simulations TCAD en deux dimensions. Nous partirons des valeurs des paramètres obtenues sur ces simulations pour ensuite optimiser le transistor LDMOS à superj onction à partir de simulations en trois dimensions.

Comparaison LDMOS / STI-LDMOS

Dans le chapitre précédent, nous avions vu que la enuet en tension d’un transistor LDMOS sur SOI dépendait à la fois des épaisseurs TSOI et TBOX mais aussi de la longueur LLDD (Équations I-14, I-15 et I-16). En considérant que la tenue en tension est limitée par la tension de claquage horizontale, il est possible d’en déduire la valeur de LLDD à partir de l’équation I-16 qui devra être supérieure à 6 µm.

Dans un premier temps, nous choisirons, pour les deux structures, LLDD égal à 7 µm. Pour le LDMOS RESURF, LPoly prendra comme valeurs 2 et 3 µm et LSFP 1 µm. En ce qui concerne la structure STI-LDMOS, nous choisirons trois valeurs pour LSTI qui sont 2, 4 et 7 µm, alors queLPoly sera fixé à 0,5 µm dans un premier temps.

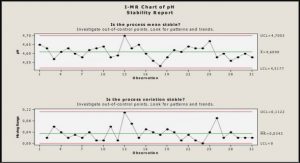

Une comparaison de la tension de claquage et de la résistance passante spécifique des deux structures est représentée figure II-2. Les simulations à l’état bloqué, pour l’extraction la tenue en tension, ont été effectuées en polarisant source, la grille et le substrat à la masse et en appliquant une tension positive sur le drain jusqu’au claquage par avalanche. La résistance passante spécifique est extraite pour VGS et VDS respectivement égales à 10 V et 0,2 V alors que la source et le substrat sont toujours à 0 V.

Toutes les simulations, sauf indication contraire, ont été réalisées en utilisant les modèles physiques standards des semiconducteurs, y compris les modèles de génération par avalanche, car, à l’état bloqué notamment, le claquage a lieu par avalanche. Afin d’accélérer les temps de calcul, nous n’avons pas pris en compte l’effet de la température : les simulations sont donc uniquement électriques.

La résistance passante spécifique des différentestructures décroit logiquement avec l’augmentation du dopage ND de la région de drift. Pour une même valeur deN D, le transistor LDMOS présente une résistance passante beaucoup plus faible que le STI-LDMOS à cause de la présence du STI qui allonge le trajet des porteurs (électrons) de la source vers le drain. Les courbes de tenue en tension sont typiques des composants RESURF [51] : la tenue en tension s’accroit linéairement avec l’augmentation de ND jusqu’à atteindre une valeur maximale au-delà de laquelle la tension de claquage chute rapid ement. La valeur maximale de BVDS de la structure LDMOS est plus faible que celle de la structure avec STI et la tenue tension se dégrade rapidement avec l’augmentation LDMOS en fonction du dopage de la région de drift

L’évolution du champ électrique en surface au moment du claquage (figure II-3) permet de mieux comprendre l’allure de ces courbes. La figure II-3 montre que, pour les faibles valeurs de ND, le pic de champ électrique est situé au niveau dela courbure N+ de drain. À l’inverse, pour les valeurs les plus élevées, ce pic se situe à la fin de la grille à l’interface avec l’oxyde. Entre les deux, pour les valeurs de ND donnant les tensions de claquage les plus élevées, le champ électrique estle plus uniforme avec deux pics de champ électrique aux deux endroits précédemment cités.

|

Table des matières

I Chapitre 1 Les composants dans les circuits intégrés de puissance

I.1 Introduction

I.2 Les technologies en silicium massif et S.O.I.

I.2.1 Intérêt des différentes technologies

I.2.2 Isolation par jonction

I.2.3 Isolation par diélectrique

I.2.3.a Le procédé SIMOX

I.2.3.b Les procédés basés sur le collage de wafers

I.3 Les composants de puissance dans les circuits intégrés

I.3.1 L’utilisation des composants de puissance

I.3.2 Les composants de puissance

I.3.2.a Le transistor LDMOS

I.3.2.b Le transistor LDMOS RESURF

I.3.2.c Améliorations de la technologie RESURF

I.3.2.d Les protections en fin de grille

I.3.2.e Les transistors LDMOS sur SOI

I.4 Conclusion

II Chapitre 2 Développement de transistors LDMOS à canal N

II.1 Introduction

II.2 Présentation des différentes structures

II.2.1 Conditions du procédé

II.2.2 Description des structures étudiées

II.3 Optimisation du compromis « résistance passante spécifique – tenue en tension »

II.3.1 Comparaison LDMOS / STI-LDMOS

II.3.2 Optimisation de transistors LDMOS à superjonction

II.4 Comportement dynamique

II.5 Tenue en tension à l’état passant : aire de sécurité

II.6 Conclusion

III Chapitre 3 Développement de transistors LDMOS à canal P

III.1 Introduction

III.2 Structures étudiées

III.3 Optimisation du compromis « résistance passante spécifique – tenue en tension »

III.3.1 Transistor LDMOS à canal P ou PLDMOS

III.3.2 Transistor PLDMOS à superjonction

III.3.3 Transistor PLDMOS à couche N enterrée

III.3.3.a Étude théorique

III.3.3.b Optimisation à partir des simulations

III.3.4 Comparatif des caractéristiques des structures LDMOS à canal P

III.4 Comportement dynamique

III.5 Aire de sécurité

III.6 Conclusion du chapitre

IV Chapitre 4

IV.1 Introduction

IV.2 Description du procédé technologique

IV.3 Essais expérimentaux

IV.3.1 Tension de claquage en fonction de la polarisation du substrat

IV.3.1.a PLDMOS et NLDMOS

IV.3.1.b Configuration du canal

IV.3.2 Caractéristiques de drain

IV.4 Optimisation du procédé

IV.4.1 Transistors à canal N

IV.4.1.a Transistor STI-LDMOS

IV.4.1.b Transistor SJ-LDMOS

IV.4.2 Transistor à canal P

IV.4.2.a Définition des profils de dopage

IV.4.2.b Simulations électriques

IV.5 Conclusion du chapitre

Conclusion générale

Références bibliographiques

Télécharger le rapport complet