CONCEPTION ET VÉRIFICATION FONCTIONNELLE DE DESIGNS EN ÉLECTRONIQUE NUMÉRIQUE

Vérification fonctionnelle en traitement de signal

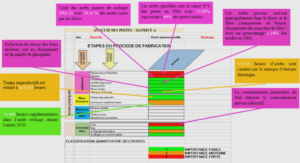

Soit l’exemple de la vérification fonctionnelle en traitement de signal. Historiquement, la conception d’un filtre numérique débute par l’utilisation d’outils algorithmiques tels que Math-Works MATLAB/Simulink. Lorsque le filtre possède les caractéristiques désirées, celui-ci est raffiné à un niveau d’abstraction inférieur se rapprochant de la cible prévue où on vérifie ses caractéristiques de nouveau. Ce processus est répété à plusieurs reprises jusqu’à l’atteinte d’une représentation assez proche de la cible permettant une confiance suffisante dans le modèle pour lancer la première vague de production.

Typiquement, il y a une cassure entre les étapes de raffinage i.e. non seulement on doit réécrire le modèle mais également les artéfacts permettant la vérification et la validation du filtre. Cette cassure est d’autant plus encline à l’introduction d’erreurs lorsque la réécriture des artéfacts ne se limite pas qu’à une simple traduction vers un autre langage.g.il est fréquent d’avoir à changer la représentation des nombres.

Absence d’une horloge globale

L’horloge globale fréquemment appelée l’horloge système n’est pas transmise (par défaut) à travers la dorsale. Comme mentionné ci-haut, ceci a le double avantage de diminuer la fréquence des communications ainsi que de permettre aux simulateurs de se mettrent en veilledans l’attente de nouvelles données.En contrepartie, l’utilisateur de la dorsale doit s’assurer qu’il y a cohérence dans le temps dans le cas où ses préoccupations s’étendent au-delà de la fonctionnalité. Enfin, l’absence d’une horloge globale facilite l’intégration du concept deHardware-in-the-loop(HIL) à cette dorsale. En effet, une carte de prototypage avec un FPGA contient sa proprehorloge et cette dernière n’est pas aussi facilement manipulable qu’en simulation logicielle.Au chapitre 6 on présentera des cas où l’horloge est générée par une enveloppe de composantedu côté du simulateur esclaves. Notez cependant que l’ajout d’une horloge peut se faire en in-cluant un signal d’horloge à l’interface d’une composante. Ainsi, la dorsale de communication a la flexibilité nécessaire pour permettre au maître de simulation de distribuer une horloge aux composantes exécutées sur des simulateurs esclaves.

Exemple de scénario

Pour faciliter la compréhension de ce chapitre, on reprend le flot de vérification traditionnel. Dans ce scénario, une première version algorithmique d’un filtre numérique à réponse impulsionnelle finie est développée à l’aide de MATLAB. Par la suite, une deuxième et une troisième versions du filtre sont conçues au niveau système. La deuxième version est un modèle fonctionnel sans notion de temps utilisant une représentation de nombres à point flottant. La troisième version est également un modèle fonctionnel, mais cette fois avec une notion de temps et une représentation de nombres à point fixe. Enfin, une quatrième version du filtre est conçue au niveau transfert de registres avec une représentation de nombres en point fixe. Le filtre au niveau algorithmique simulé avec MATLAB sert tout au long de la conception comme modèle de référence.

Étant un outil algorithmique avec des boîtes à outils graphiques, MATLAB est un outil de choix pour la génération et la validation des données. C’est donc ce dernier qui est utilisé pour générerles données d’entrées des filtres ainsi que pour comparer les données de sorties des filtres.Puisque MATLAB est au centre de ce scénario, il est utilisé comme maître de simulation.Ainsi, MATLAB a besoin de trois composantes passerelles (clients CORBA) faisant le pontavec les outils simulant les trois autres versions du filtre (serveurs CORBA).

|

Table des matières

INTRODUCTION

CHAPITRE 1 CONCEPTION ET VÉRIFICATION FONCTIONNELLE DE DESIGNS EN ÉLECTRONIQUE NUMÉRIQUE

1.1Historique

1.1.1Vérification fonctionnelle en traitement de signal

1.1.2Support multi niveaux d’abstraction

1.1.3Cosimulation

1.1.4Méthodes de vérification fonctionnelle pour un système hétérogène

1.2Survol des architectures de communication

1.2.1Acceptation ou normalisation

1.2.2Efficacité et performance

1.2.3Support multi environnements ou adaptabilité aux environnements hétérogènes

1.2.4Support de multiples niveaux d’abstraction

1.3Conclusion

CHAPITRE 2 SPÉCIFICATION DE L’ENVIRONNEMENT DE CONCEPTION ET DE VÉRIFICATION FONCTIONNELLE

2.1Spécifications

2.1.1Composantes hétérogènes

2.1.2Simulateurs et outils de conception

2.1.3Communication

2.1.4Adaptation de fonctionnalité et des données

2.1.5Normalisation

2.1.6Simplicité d’utilisation

2.2Hypothèses de travail

2.3Utilisateurs

2.4Conclusion

CHAPITRE 3 ARCHITECTURE DE LA DORSALE DE COMMUNICATION

3.1Modèle d’architecture

3.2Environnement de communication

3.3Composantes passerelles

3.4Adaptateurs d’outil

3.5Enveloppes de composante

3.6Enveloppes de client ou de serveur

3.7Initialisation de la simulation

3.8Conclusion

CHAPITRE 4 IMPLÉMENTATION ET INTÉGRATION DE LA DORSALE

4.1Caractéristiques communes

4.1.1Absence d’une horloge globale

4.1.2Communications bloquantes

4.1.3Mécanismes POSIX

4.2MathWorks MATLAB/Simulink

4.3Simulateur de l’Open SystemC Initiative

4.4Mentor Graphics ModelSim

4.5GHDL

4.6Conclusion

CHAPITRE 5 INTÉGRATION D’UN DESIGN ÉLECTRONIQUE NUMÉRIQUE

5.1Exemple de scénario

5.2Choix du maître de simulation

5.3Stratégie de nomenclature

5.4Description de composantes

5.5Autogénération des artéfacts

5.6Adaptation des artéfacts

5.6.1Composantes passerelles et clients CORBA

5.6.2Simulateurs esclaves ou serveurs CORBA

5.7Compilation

5.8Configuration

5.9Exécution

5.9.1Naming Service CORBA

5.9.2Simulateurs esclaves ou serveurs CORBA

5.9.3Maître de simulation

5.10Conclusion

CHAPITRE 6 EXPÉRIMENTATION

6.1Étude de cas : implémentation d’un filtre

6.1.1Architecture

6.1.2Formats de représentation des nombres

6.1.3Méthodologie de conception et de vérification

6.1.4Résultats

6.2Comparaison avec une solution commerciale

6.2.1Présentation

6.2.2Méthodologie

6.2.3Intégration

6.2.4Performance

6.3Conclusion

CONCLUSION

RECOMMANDATIONS

BIBLIOGRAPHIE

![]() Télécharger le rapport complet

Télécharger le rapport complet