Conception des Systèmes Embarqués

Loi empirique de Moore 1965 « Pour une surface de silicium donnée, la capacité d’intégration (le nombre de transistors dans un processeur) double tous les 18 mois». (Gordon Moore – cofondateur d’Intel) .

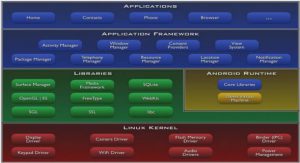

Les ordinateurs et, plus généralement, les systèmes électroniques et informatiques sont désormais devenus omniprésents dans la vie de tous les jours : téléphones portables, baladeurs, PDAs, cartes de paiement, etc., et même dans des applications moins « voyantes » mais pas moins répandues (conduite assistée pour voitures, monitorage du trafic, contrôles d’accès, systèmes de sécurité, etc.). Il est presque impossible de tourner la tête sans voir au moins une application. L’évolution des technologies de fabrication ont permis d’augmenter non seulement la capacité d’intégration, mais aussi la fréquence de fonctionnement des composants. Gordon Moore [1] a prédit dans les années 60 que la croissance de la complexité des circuits intégrés suivrait une courbe exponentielle (voir doubleraient tous les deux ans) alors que la taille des transistors diminuerait dans les mêmes proportions. En pratique, l’architecture interne des processeurs se révèle de plus en plus complexe, de sorte à améliorer et accélérer l’exécution d’un programme, ou d’un ensemble de programmes [2]. Pour répondre aux exigences du marché, avec une diversité d’applications, l’électronique a dû progressivement s’adapter pour devenir portable, puis ultra miniaturisée : c’est la naissance des systèmes (numériques) embarqués. Ces systèmes ont vu leur importance progresser au rythme de l’importance prise par les microprocesseurs. Le marché des microprocesseurs est un marché qui croît de façon exponentielle. Ce marché a aussi tiré le marché des systèmes embarqués (et des télécommunications). En effet, selon quelques statistiques [3], 90% des processeurs sont destinés à l’industrie des systèmes embarqués.

Conception des systèmes numériques

Un calcul numérique est un ensemble de calculs réalisés sur un système informatique, encore appelé système numérique (ou ordinateur). Pendant longtemps, les calculs sont effectués par les ordinateurs et entièrement pris en charge par le processeur central (CPU). Or ce processeur s’avère insuffisant dans un certain nombre de domaines. Des circuits plus efficaces ont été créés et travaillant en parallèle avec le processeur, spécialement pour des tâches bien définies. En plus, les évolutions technologiques acquises dans le monde industriel actuel ont permis l’intégration de plus en plus de fonctions sur le même circuit intégré numérique. Aujourd’hui, on arrive à embarquer plusieurs microprocesseurs, des accélérateurs matériels, des systèmes de communications diverses, des systèmes d’exploitation, etc. Ceci permet donc de réaliser toutes les fonctions nécessaires pour effectuer des traitements informatiques complexes sur la même puce, d’où la naissance de la notion des systèmes sur puce (SoC pour System on Chip), successeurs des circuits spécialisés ASIC (Application Specific Integrated Circuit). Dans cette première partie, nous définissons les différents processeurs et les différents circuits programmables.

Architectures à base d’un processeur

Les GPP (General Purpose Processor) sont des processeurs dont l’image est souvent associée à celle de l’ordinateur personnel (PC). Leur popularité est liée à leur flexibilité, leur simplicité d’utilisation et leur puissance de calcul [2]. L’association processeur-PC n’est toujours vraie, puisque les processeurs destinés aux systèmes embraqués occupent la plus grande partie du marché des processeurs. Par contre, les processeurs destinés aux systèmes embarqués sont différents des processeurs destinés aux ordinateurs grand public. D’abord le concept CISC (Complex Instruction Set Computer) a subi au cours des années une « cure d’amincissement » afin d’arriver à des architectures RISC (Reduced Instruction Set Computer) dans lesquelles les instructions et les modes d’adressage complexes étaient bannis [4]. Des principes de simplification ont été mis en œuvre (comme par exemple le codage uniforme des instructions) afin de permettre notamment d’avoir des compilateurs fournissant de bonnes performances [3].

Les processeurs d’usage général (GPP)

La puissance de calcul et la flexibilité sont les objectifs premiers d’un GPP. Ils sont atteints grâce à une fréquence de fonctionnement élevée et des architectures matérielles et logicielles adaptées : super scalaire, fort pipeline, prédiction de branchement, caches multi-niveaux, instructions spécialisés (par exemple l’instruction multimédia : MMX pour le Pentium et AltiVec pour le PowerPC) et extension SIMD (Single-Instruction Multi-Data) [5]. Cependant, un GPP n’est pas bien adapté aux applications embarquées du traitement du signal et de l’image, et cela à cause de deux principales raisons :

– Dissipation d’énergie généralement élevée dans les GPP ;

– Les GPP ne sont pas adaptés au temps réel pour les applications complexes.

On retrouve dans la plupart des systèmes sur puce des processeurs à usages généraux comme par exemple PowerPC, ARM, MIPS, ST-Microelectronics, etc. Ces processeurs ont des caractéristiques plus ou moins rapprochées. Ils sont destinés à effectuer des traitements ordinaires, sans qu’ils aient des performances optimales. La différence remarquable de ces processeurs utilisés dans les systèmes sur puce par rapport aux processeurs ordinaires, de la famille 80xx d’Intel et des 68xx de Motorola par exemple, réside dans le fait qu’ils utilisent du pipeline et de la mémoire cache afin de limiter le nombre d’accès à la mémoire centrale du système et de minimiser, par conséquent, l’utilisation du bus et de la consommation d’énergie du système [6].

Les processeurs de traitement du signal

Certains systèmes numériques intègrent également des processeurs à usages spécifiques pour des applications de traitement du signal et des images (DSP pour Digital Signal Processors). Ces processeurs spécialisés sont surtout destinés aux traitements d’images de type «bas niveau» pour lesquels les calculs sont réguliers (les traitements sont identiques pour toutes les données d’entrée) et doivent être réalisés à hautes fréquences [7]. Les DSP sont des processeurs simplifiés relativement semblables aux GPP. Leur particularité essentielle est qu’ils sont conçus pour effectuer des calculs en temps réel et intègrent donc de nombreux opérateurs. En effet leur architecture interne est dimensionnée pour le calcul intensif. Suivant les modèles, ils permettent de réaliser des opérations sur des nombres soit à virgule fixe, soit à virgule flottante. Ces processeurs permettent également un accès rapide aux données par des adressages particuliers [8]. Leur jeu d’instructions est souvent plus réduit que celui d’un processeur traditionnel et peut être programmé soit en assembleur, soit avec un compilateur C dédié. Ces processeurs ont la possibilité de réaliser plusieurs instructions en parallèle et possèdent des opérateurs de calculs arithmétiques flottants très performants. Dans un DSP, les transferts entre les périphériques et la mémoire d’une part et entre la mémoire interne et la mémoire externe d’autre part, sont réalisés par le DMA (Direct Memory Access), qui permet de décharger le cœur de calcul, et de paralléliser les deux opérations (accès à la mémoire et le traitement). Des interfaces série, PCI, mémoire sont également intégrées au DSP. Les DSP sont accompagnés d’outils de développement performants. Les débogueurs fournissent des informations de bas niveau pour valider rapidement une application. Les fabricants fournissent en général des compilateurs capables d’optimiser fortement un programme et d’informer le développeur sur le résultat en ajoutant des commentaires dans le programme (boucle optimisée, nombre de cycles, instructions utilisées). Des simulateurs permettent d’obtenir des informations supplémentaires sur l’exécution d’une application (charge de calcul, comportement des mémoires caches, temps d’exécution) [2]. Un DSP est utilisé dans plusieurs domaines d’application qui nécessitent l’utilisation de filtres numériques ou adaptatifs, des FFTs, dans l’instrumentation (analyse transitoire, spectrale), dans le domaine médical (monitoring, échographie, imagerie médicale), dans les applications de contrôle (asservissement, robotique), ainsi que dans le multimédia, l’imagerie, le militaire (radar, guidage de missile), les télécommunications (modems radio, cryptage de données, répéteurs de ligne) et les applications grand public (automobile, électroménager), etc.

|

Table des matières

Introduction générale

Chapitre I : Conception des systèmes embarqués

1. Introduction

2. Conception des systèmes numériques

2.1. Architectures à base d’un processeur

2.1.1. Les processeurs à usage général (GPP)

2.1.2. Les processeurs de traitement du signal

2.1.3. Les processeurs reconfigurables

2.2. Les circuits logiques programmables

2.2.1. Les PLDs et les CPLDs

2.2.2. Les FPGAs

2.2.3. Les ASICs

3. Les systèmes numériques embarqués

3.1. Codesign : Conception conjointe logicielle/matérielle

3.1.1. Flot de la conception conjointe logicielle/matérielle

3.1.2. Les composants virtuels (IPs)

3.1.3. Les accélérateurs matériels

3.2. Les systèmes sur puce (SoC)

3.2.1. Définitions d’un SoC

3.2.2. Les contraintes des systèmes embarqués

3.2.3. Les SoC et les SoPC

3.3.Communications sur puce

3.3.1. Les différents types des communications sur puce

3.3.2. Exemple : Le Bus CoreConnect

4. Plateformes multi-composants

4.1. Les deux grandes familles des FPGA

4.1.1. La famille Xilinx

4.1.2. La famille Altéra

4.2. Les processeurs embarqués

4.2.1. Les processeurs hard (hardcore)

4.2.2. Les processeurs soft (softcore)

4.2.3. Les processeurs softcore open source

Chapitre II : La compression vidéo et la nouvelle norme de compression H.264/AVC

1. Introduction

2. Le codage vidéo

2.1. Définitions

2.1.1. L’espace colorimétrique des pixels

2.1.2. Le format YUV

2.1.3. Format d’image : première idée de compression

2.2. Problématique

2.3. La compression vidéo

2.3.1. Processus de codage vidéo

2.3.2. Processus de décodage

2.3.3. Evaluation de la qualité des images décodées

2.3.4. Types des codeurs vidéo

2.4. L’estimation de mouvement et la compression vidéo

2.4.1. Estimation de mouvement à un nombre entier de pixels

2.4.2. Compression vidéo par estimation et compensation de mouvement

2.4.3. Critères de mesure de distorsions

2.5. Les normes de compression vidéo

2.5.1. Les normes de l’UIT-T

2.5.2. Les normes de l’ISO/MPEG

2.5.3. H.264 ou bien MPEG4 part 10

2.5.4. Evolution des normes de compression vidéo

3. La nouvelle norme de compression H.264/AVC

3.1. Présentation générale

3.1.1. Division des images en blocs et macroblocs

3.1.2. Les types de prédiction dans H.264

3.1.3. Les critères de distorsion dans H.264

3.2. Vue d’ensemble du codec H.264/AVC

3.2.1. Flux de données dans H.264

3.2.2. L’encodeur H.264

3.2.3. Le décodeur H.264

3.2.4. Les profils et les niveaux de H.264/AVC

3.3. Le codage intra-image

3.3.1. Prédiction Intra4×4

3.3.2. Prédiction Intra16×16

3.3.3. Mode de décision et coût de calcul du codage intra-image

3.4. Le codage inter-image

3.4.1. Prédiction à partir des images de référence

3.4.2. Estimation et compensation de mouvement dans H.264

3.4.3. Prédiction inter-image des images B

3.5. La transformation et la quantification directes et inverses

3.5.1. Développement de la transformée et la quantification directes

3.5.2. Développement de la quantification et la transformée inverses

3.5.3. Elaboration des matrices de la transformée directe

3.5.4. Elaboration des matrices de la transformée inverse

3.6. Le filtre anti-blocs

3.6.1. Choix de la force de frontière (Boundary strength)

3.6.2. Implémentation logiciel du filtre

3.6.3. Organigramme du filtre

3.7. Organisation des données à la sortie de la chaine directe

3.7.1. Flux de données de la prédiction Intra

3.7.2. Flux de données de la prédiction Inter

4. Performances et applications

4.1. Applications de H.264/AVC

4.2. Produits et mises en œuvre de H.264/AVC

4.3. Statistiques pour la norme H.264

4.4. H.264/AVC et après ?

5. Conclusion

Chapitre III : Les outils de conception des systèmes et le traitement d’images temps réel

1. Introduction

2. Notion du temps réel

2.1. Définitions

2.1.1. Le temps réel et la vitesse des processeurs

2.1.2. Les deux types des systèmes temps réel

2.1.3. Systèmes embarqués temps réel

2.2. Exemples d’applications des systèmes temps réel

2.3. Temps réel pour la compression vidéo

2.4. Contraintes de conception des systèmes embarqués temps réel

2.4.1. Contraintes liées à l’architecture système

2.4.2. Contraintes liées à l’architecture mémoire

2.5. Les solutions technologiques pour assurer le temps réel

2.5.1. Choix du matériel

2.5.2. Choix de la méthode de gestion de la mémoire

2.5.3. Les solutions technologiques dans les accélérateurs matériels

3. Conception des systèmes temps réel

3.1. Evolution des méthodes de conception

3.2. Les langages de description de matériel

3.2.1. Les HDLs (VHDL et Verilog)

3.2.2. Les langages de simulation de haut niveau

3.2.3. Les langages de spécification de haut niveau

3.2.4. Classification des langages de description de matériel

4. Les outils de conception des systèmes temps réel

4.1. Généralités sur les outils de développement

4.1.1. Les outils de synthèse

4.1.2. Simulation et simulateur numérique

4.1.3. Les outils de codesign

4.2. Flot de prototypage FPGA générique

4.3. Exemples des outils de développements des systèmes embarqués

4.3.1. HDL Designer de Mentor Graphics

4.3.2. Le logiciel Synplify de Cadence

4.3.3. ModelSim de Mentor Graphics

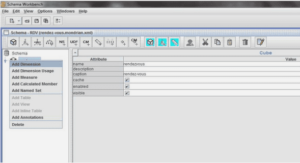

4.3.4. SOPC Builder d’Altera

4.4. Les Outils de développement de Xilinx

4.4.1. Flots de conception Xilinx

4.4.2. Xilinx ISE

4.4.3. Xilinx EDK

4.5. Les outils utilisés

5. Conclusion

Conclusion générale