Télécharger le fichier pdf d’un mémoire de fin d’études

Grandeurs caractéristiques

Un modulateur sigma-delta est caractérisé par :

– le type de réalisation : à temps discret ou à temps continu.

– la fonction du filtre de boucle : passe-bas ou passe-bande.

– l’ordre n qui est défini par l’ordre du filtre de boucle.

– le nombre de niveaux de quantification N qui est le nombre de bits des CAN et CNA.

– le rapport de sur-échantillonnage OSR, dont la définition est donnée ci-dessous.

La définition de l’OSR (OverSampling Rate) pour un modulateur passe-bas s’écrit : OSR = fe2fmax (1.6).

Stabilité du modulateur

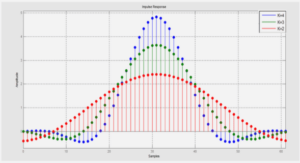

Pour concevoir et analyser un modulateur sigma-delta, on utilise habituellement un modèle sim-plifié du quantificateur : le quantificateur est alors interprété comme un additionneur de bruit blanc non corrélé à son signal d’entrée. Bien que cette modélisation du quantificateur ne représente pas la réalité, elle offre une évaluation suffisante des performances atteintes avec un modulateur sigma-delta d’ordre n en fonction de son rapport de suréchantillonnage. Cependant, elle ne permet pas d’analyser son comportement non-linéaire et interdit toute étude de stabilité satisfaisante. Un modèle enrichi du quantificateur 1 bit est utilisé pour analyser le comportement instable des modulateurs. Le quantifi-cateur est modélisé par un amplificateur ayant un gain variable · suivi d’une source de bruit blanc additif. Ce modèle est basé sur le théorème de Kalman sur la stabilité des systèmes non linéaires [5]. Le domaine de stabilité s’étudie alors sur le plan complexe par l’emplacement des pôles et des zéros [6, 7, 8].

Performances des modulateurs sigma-delta

Les performances d’un modulateur s’évaluent à l’aide de nombreuses grandeurs. Les plus fréquem-ment données dans les publications sont le rapport signal sur bruit (SNR : Signal to Noise Ratio) et la plage d’amplitude permise pour les signaux d’entrée (DR : Dynamic Range). La grandeur permet-tant au mieux de définir les performances d’un modulateur est le facteur de mérite d’un modulateur sigma-delta, car il prend en compte les performances obtenues mais aussi les caractéristiques de la réa-lisation comme la puissance consommée et la surface occupée. Mais le facteur de mérite est rarement annoncé dans les publications.

Rapport signal sur bruit

Le rapport signal sur bruit (SNR : Signal to Noise Ratio) est donné par la relation : SN R(dB) = 10 log µ Psignal ¶ (1.17).

Psignal est la puissance du signal d’entrée et Pbruit est la puissance de bruit sur la bande utile. Le SN R dépend de l’amplitude du signal d’entrée considéré, qui est généralement un signal sinusoïdal. On donne en général pour un modulateur le SN R maximal obtenu.

Résolution

La résolution, ou nombre de bits effectifs (ENOB : Effective Number of Bits) représente le nombre de niveaux de quantification d’un système de conversion classique (de type Nyquist) qui serait équi-valent au convertisseur sigma-delta. L’ENOB est donc calculé directement à partir de l’expression du rapport signal sur bruit d’une conversion classique : SN R(dB) = 6:02N + 1:76 (1.18)

où N est le nombre de bits équivalents d’un convertisseur classique. On note que cette expression est celle du SNR maximal pouvant être atteint, car il est calculé en considérant à l’entrée du CAN un signal sinusoïdal d’amplitude égale à la pleine échelle. La valeur du SNR chute lorsque l’on diminue l’amplitude des signaux d’entrée.

Pour évaluer le nombre minimal de bits effectifs de résolution d’un convertisseur sigma-delta, on utilise l’expression précédente, soit : ENOB = SN R(dB) ¡ 1:76 (1.19).

Choix des paramètres de l’architecture à temps discret Architecture MSCL

Les contraintes liées à la technologie ne permettent pas d’augmenter indéfiniment la fréquence de sur-échantillonnage pour augmenter la résolution. On est alors obligé d’augmenter l’ordre du modulateur. Cependant, les modulateurs d’ordre supérieur à 2 se révèlent instables dans le cas simple boucle et très sensibles aux non-idéalités dans le cas multiboucle. Ainsi pour concevoir des architectures stables d’ordre élevé, le choix se porte sur les architectures cascadées et plus particulièrement sur l’architecture MSCL (Multi Stage Closed Loop) [39], car sa sortie est exploitable sans traitement numérique (voir x 1.4.2). Ainsi, l’architecture de départ pour nos calculs en temps discret est l’architecture MSCL présentée à la figure 2.1.

Calcul des architectures à temps continu

Pour le calcul de l’architecture monoboucle à temps continu à partir de l’expression du filtre de boucle à temps discret, la méthode présentée au x1.5 a été implémentée dans le logiciel ADOC lors de travaux précédents. Ce logiciel utilise entre autre Maple comme outils de calcul formel. Plusieurs possibilités pour l’ordre du filtre de boucle à temps discret et le nombre de bits du CAN ont été déterminées précédemment (figure 2.2). Ces paramètres sont nécessaires pour le calcul, comme le sont les paramètres suivants :

– le facteur de qualité des filtres de boucle à temps continu.

– le retard de boucle dû aux CAN et CNA. Suivant ce retard, la valeur du coefficient de rebouclage rapide (polynôme D(z)) va changer (voir x1.5) et figure 2.5.

Contrairement aux filtres à temps discret, les filtres à temps continu n’ont pas un facteur de qualité infini. Ils ont la forme canonique suivante : G(s) = A0s s2 + !0 Q0 s + !2 0 (2.9) .

Imperfections du CNA

La précision du modulateur dépend de la précision du signal rebouclé et ainsi de la linéarité du CNA dans la chaîne de retour. Classiquement pour un modulateur N bits, le CNA est constitué de 2N ¡ 1 sources de courant commutées dont le courant de sortie est sommé dans une résistance. Les dispersions technologiques sur les sources de courant, les résistances et les phénomènes d’injection de charges sont responsables des non-linéarités du CNA.

Les erreurs liées aux sources du CNA se divisent en deux catégories :

– l’erreur statique est l’erreur sur la valeur nominale des sources.

– l’erreur dynamique dépend de l’état précédent et de la relation qui existe entre des sources voisines.

Architecture proposée

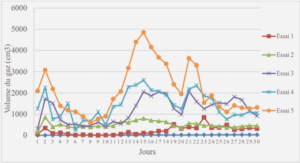

Il est difficile de prendre en compte au niveau système l’impact des erreurs dynamiques. En revanche, il est possible de modéliser au niveau système l’erreur statique sur les sources. Une telle modélisation est disponible dans le logiciel ADOC, ce qui nous a permis de simuler le comportement d’un modulateur avec de telles erreurs. La déviation des niveaux du CNA pour une technologie classique dans un pire cas est évaluée à 10 %. Dans ce cas la résolution obtenue pour un modulateur parallèle d’ordre 6 à niveaux de quantification est présentée dans le tableau 2.5 dans le cas idéal, avec des erreurs statiques sur les sources du CNA et enfin avec un algorithme de brassage de source du type passe-bande [47].

Evolution vers une structure autoadaptative

Afin de rendre le modulateur sigma-delta adaptable automatiquement à plusieurs valeurs de fréquence du signal d’entrée, un asservissement de la fréquence centrale et du facteur de qualité du résonateur d’entrée sur ce signal devrait être envisagé. Un certain nombre de publications [49, 50, 51] traitent de l’asservissement des filtres RF. Un synoptique général simplifié (figure 2.18) montre comment pourrait s’effectuer ces asservissements grâce à un oscillateur contrôlé en tension (VCO). Cet exemple peut s’appliquer aux résonateurs de type Gm-LC dont le facteur de qualité est amélioré par une résistance négative et la fréquence centrale réglable par une tension appliquée sur des varicaps.

Le réglage de la fréquence centrale s’effectuerait par un circuit de type PLL accroché sur le signal d’entrée (partie basse de la figure 2.18).

Le réglage du facteur de qualité (partie haute de la figure 2.18) s’effectuerait par un courant de retour iQ résultant de deux branches : la branche du haut qui tend à régler un facteur de qualité infini et la branche du bas qui fait en sorte que l’enveloppe de sortie du VCO soit proche d’une valeur fixée Vref pour que la résistance négative fonctionne dans sa zone linéaire.

Les différents types de transistors

Le comportement des composants électroniques à semi-conducteurs est conditionné par la nature des interfaces ou jonctions qui en séparent les différentes parties constitutives (métalliques, diélectriques ou semi-conductrices) et par la façon dont les porteurs, électrons ou trous, longent ou traversent ces interfaces. Deux types de jonctions sont à distinguer : les homojonctions et les hétérojonctions.

Les homojonctions semi-conducteur/semi-conducteur sont les plus courantes jusqu’à la fin des années 80. Le semi-conducteur utilisé est alors généralement du silicium à dopage différent suivant l’interface, aussi bien pour les transistors bipolaires que pour les transistors à effet de champ. Ces filières sont aujourd’hui les plus matures (NMOS, CMOS, bipolaires et BiCMOS). L’arséniure de gallium comprend la filière à effet de champ de type MESFET (voir x 3.3.2).

Les hétérojonctions, qui ont vus le jour au milieu des années 80, sont des jonctions où se trouvent juxtaposés deux semi-conducteurs différents. Cette possibilité de combiner, au sein d’un même composant, des semi-conducteurs de structures de bandes différentes, apporte des degrés de liberté supplémentaires (changement de la largeur de gap, accroissement de la mobilité des porteurs) permettant de développer des composants nouveaux à performances améliorées, dont les transistors HEMT (transistor à effet de champs amélioré) et HBT (bipolaire).

Le tableau 3.2 [56] présente les fréquences de transition atteintes par les technologies de type CMOS sur silicium, sur SOI, BiCMOS et GaAs. La fréquence de transition, inversement proportionnelle à la longueur de grille, est la grandeur qui renseigne le mieux sur la vitesse maximale de fonctionnement des circuits.

|

Table des matières

Introduction

1 La modulation sigma-delta passe-bande à temps continu

1.1 Introduction

1.2 Principe de la modulation sigma-delta

1.2.1 Structure du modulateur sigma-delta

1.2.2 Quantification et bruit de quantification

1.2.3 Grandeurs caractéristiques

1.2.4 Modèle linéaire du modulateur sigma-delta

1.2.5 Mise en forme du bruit de quantification

1.2.6 Stabilité du modulateur

1.2.7 Du modulateur passe-bas au modulateur passe-bande

1.2.8 Stabilité d’un modulateur sigma-delta passe-bande

1.3 Performances des modulateurs sigma-delta

1.3.1 Rapport signal sur bruit

1.3.2 Résolution

1.3.3 Rapport signal sur bruit et distorsions

1.3.4 Dynamique libre des raies parasites

1.3.5 Dynamique d’entrée du modulateur

1.3.6 Bande passante à -3 dB

1.3.7 Facteurs de mérite

1.4 Les différentes architectures de modulateurs

1.4.1 Modulateur classique

1.4.2 Modulateur en cascade

1.5 Du modulateur sigma-delta à temps discret au modulateur à temps continu

1.6 Etude de la stabilité d’un modulateur sigma-delta à temps continu

1.6.1 Tracé du lieu des pôles et zéros

1.6.2 Utilisation du critère de Nyquist

1.7 Etat de l’art de la modulation sigma-delta à temps continu

1.8 Conclusion

2 Proposition d’une architecture à fréquence centrale ajustable

2.1 Introduction

2.2 Architectures envisageables

2.2.1 Objectif

2.2.2 Démarche

2.2.3 Choix des paramètres de l’architecture à temps discret

2.2.4 Calcul des architectures à temps continu

2.2.5 Imperfections du CNA

2.3 Architecture proposée

2.4 Stabilité et performances

2.4.1 Choix pour le réglage

2.4.2 Stabilité

2.4.3 Performances

2.5 Evolution vers une structure autoadaptative

2.6 Conclusion

3 La technologie GaAs

3.1 Introduction

3.2 Choix de la technologie

3.2.1 Critères de choix

3.2.2 Les différents types de matériaux pour l’intégration

3.2.3 Les différents types de transistors

3.2.4 Technologie retenue

3.3 Dispositifs disponibles dans la technologie OMMIC

3.3.1 Présentation générale de la technologie OMMIC

3.3.2 Transistor P-HEMT

3.3.3 Diodes

3.3.4 Inductances intégrées

3.3.5 Condensateurs intégrés

3.3.6 Résistances intégrées

3.3.7 Interconnexions

3.4 Montages préférentiels

3.4.1 Structures de base

3.4.2 Montage cascode

3.4.3 Amplificateur différentiel à transconductance

3.4.4 Décaleurs de tension

3.4.5 Source de courant de polarisation

3.4.6 Condensateur de liaison

3.5 Conclusion

4 Conception des blocs du modulateur sigma-delta

4.1 Introduction

4.2 Les résonateurs

4.2.1 Choix d’une structure de résonateurs

4.2.2 Conception des résonateurs Gm-LC

4.2.3 Caractéristiques des circuits résonateurs

4.2.4 Robustesse des résonateurs

4.2.5 Conclusion

4.3 Le sommateur

4.3.1 Spécifications attendues

4.3.2 Circuit sommateur et résultats de simulations

4.3.3 Robustesse du sommateur

4.3.4 Conclusion

4.4 Le comparateur

4.4.1 Spécifications attendues

4.4.2 Choix d’une structure de comparateur

4.4.3 Circuit comparateur et résultats de simulation

4.4.4 Robustesse du comparateur

4.4.5 Conclusion

4.5 Conclusion

5 Le modulateur complet

5.1 Introduction

5.2 Simulation du modulateur au niveau transistor

5.2.1 Cas nominal

5.2.2 Situation par rapport à l’état de l’art

5.3 Testabilité

5.3.1 Objectifs du test

5.3.2 Conception et testabilité

5.3.3 Test du circuit

5.4 Dessin du masque du modulateur et rétrosimulation

5.4.1 Règles d’implantation

5.4.2 Rétrosimulations

5.5 Robustesse du modulateur

5.5.1 Méthodologie

5.5.2 Comparateur

5.5.3 Résonateurs

5.5.4 Sommateur

5.5.5 Simulation globale

5.5.6 Augmentation de la fréquence centrale du modulateur

5.6 Conclusion

6 Conclusion

A Brassage de source passe-bande

A.1 Introduction

A.2 Principe du brassage de source passe bande

A.3 Architecture proposée

B Compléments sur la technologie

B.1 Introduction

B.2 Composants

B.2.1 Diodes

B.2.2 Bobines

B.3 Les différents niveaux de matériaux

B.4 Les paramètres de simulations statistiques

C Dimensionnement d’un résonateur Gm-C à 1 GHz

C.1 Introduction

C.2 Le principe de la simulation d’inductance

C.3 Dimensionnement du circuit

D Résultats de mesures sur les résonateurs

D.1 Introduction

D.2 Caractéristiques des circuits

D.3 Préparation des mesures

D.3.1 Circuit imprimé

D.3.2 Ajouts

D.4 Mesures sur CIR2

D.4.1 Résultats attendus

D.4.2 Résultats obtenus

D.4.3 Commentaires

D.5 Mesures sur CIR3

D.5.1 Résultats attendus

D.5.2 Résultats obtenus

D.5.3 Commentaires

D.6 Masques des résonateurs

E Calcul des performances

Télécharger le rapport complet