Architectures d’émission pour les applications multi-radio

Critères d’évaluation d’une architecture d’émission

Notre travail s’inscrit dans le domaine des architectures reconfigurables pour l’émission de standards cellulaires. Afin de pouvoir comparer différentes solutions pour la conception d’une architecture multi-radio, nous allons nous intéresser à deux grandes catégories de critères de jugements : celle liée au standard et à la qualité du signal généré (performance électriques incluses), et celle liée à l’implantation (limites technologiques). La prise en compte des avantages et des inconvénients sur ces des différents critères et figures de mérite de chacune de ces catégories nous permettra d’appréhender une difficile sélection des architectures candidates (sélection partielle éventuellement).. En fonction du standard, des capacités d’implémentation liées à la technologie et des performances visées, chaque type d’architecture présente un intérêt.

Critères liés au standard

• Dynamique de contrôle en puissance

Le contrôle de la puissance d’émission permet de gérer les émetteurs mobiles dans une cellule afin d’éviter des phénomènes de masquage et de saturation à la réception. Les différents standards à émettre ont chacun leurs spécifications (gamme de puissance et pas) pour le contrôle de puissance. Dans un système multistandards, en fonction du standard à émettre, l’architecture doit être capable de contrôler la dynamique du signal. Cette dynamique peut atteindre en valeur pic les 90dB lorsque l’on émet des signaux de type W-CDMA.

• Gestion du PAPR (Peak to Average Power Ratio)

Ce paramètre caractérise la façon dont l’architecture gère l’émission en puissance des signaux à forte dynamique d’enveloppe et les problèmes de linéarité et de rendement qui lui sont associés. Il traduit la capacité de l’architecture à générer, et le plus souvent amplifier en puissance jusqu’à l’antenne, la forme temporelle du signal, tout en limitant les effets de non linéarités introduits (par exemple lors de l’amplification). Pour un standard tel que le LTE, on peut avoir des valeurs de PAPR moyen de l’ordre de 9 dB. En effet celui-ci est lié à la statistique du signal.

• Bruit et émissions parasites

Le bruit est un critère très contraignant dans la conception d’une architecture. Il est essentiellement issu de la synthèse de fréquence mais à la méthode de quantification du signal (bruit de quantification), au bruit thermique et au bruit des composants actifs. Plus haut en fréquence on parlera d’émissions parasites, qui elles sont plus dues à des phénomènes tels que les raies de suréchantillonnage ou la fuite OL.

• Largeur de bande

Elle caractérise la capacité de l’architecture à émettre des signaux « large bande ». Les standards récents, qu’ils soient de connectivité (WiMAX) ou cellulaires (LTE), ont des largeurs de bande pouvant atteindre les 20 MHz. Chaque élément de l’architecture doit donc être en mesure de travailler avec une telle largeur de bande. C’est un des paramètres les plus contraignants car il demande une conception plus complexe des blocs fonctionnels (optimisation de l’adaptation en fréquence) et est souvent la cause d’une augmentation de la consommation de la partie « numérique / bande de base ».

• Fréquence d’étude du système

Ce paramètre défini la fréquence centrale pour laquelle l’architecture a été conçue. Une montée en fréquence complique fortement la conception d’une architecture et impose une prise en compte précise des défauts liés à la technologie d’implantation. La conception d’un DAC peut être fortement impactée par la fréquence de travail (ex.Sigma Delta). Des performances optimales de l’architecture sont alors attendues aux différentes fréquences de fonctionnement, dans le cadre de la multi-radio.

• Gestion du Multi-standards

L’émetteur multi-radio doit pouvoir s’adapter dynamiquement à l’environnement radio, et donc gérer un changement de standard d’émission. Cette gestion implique une reconfiguration/compatibilité « software » amont que nous ne développerons pas par la suite car nous nous concentrerons, dans cette thèse, sur les difficultés de la reconfigurabilité/compatibilité « hardware ». Pour être multi-standards, ce dernier doit couvrir des fréquences allant de 824 MHz (GSM850) à 2.62 GHz (LTE). Il faut limiter au maximum la parallélisassions des architectures, ce qui reviendrait en fait à commander plusieurs emetteurs-recepteurs. L’intérêt d’un paramétrage des blocs fonctionnels est alors évident (selon ce critère). Les architectures basées sur une approche « tout numérique » se positionnent alors en favoris d’après ce point de vue, comme nous le développerons par la suite.

• Reconfigurabilité en bande

La reconfigurabilité en bande caractérise l’agilité de l’architecture à adresser le signal en fréquence, dans les différentes sous bandes d’un standard. Ce critère est particulièrement lié aux éléments de synthèse de fréquence, de mélange mais aussi de filtrage. La sélectivité, la sensibilité et les pertes de ces différents éléments sont alors des considérations omniprésentes car fortement liées à la fréquence des différentes gammes voulues.

Critères liés à l’implémentation

• Linéarité

Ce paramètre est essentiellement lié aux éléments non linéaires d’une chaine d’émission, que sont principalement les mélangeurs et les amplificateurs. Il est donc nécessaire de quantifier la distortion du signal induite par les différents éléments de l’architecture. On peut définir deux type de distorsion ; une distorsion en phase ou conversion (AM / PM) qui entraine une rotation de la constellation et une distorsion en amplitude (AM /AM) qui entraine une compression de la constellation. Une distorsion du signal à l’émission entraîne une augmentation de l’EVM (Error Vector Magnitude), donc une mauvaise démodulation à la réception et donc un risque accru d’erreurs symboles et binaire (risque de perte de données). Il existe par exemple des techniques extérieures de linéarisation numériques DPD (Digital Predistorsion), mais on peut également concevoir l’architecture de façon à limiter les effets non linéaires plutôt que de les corriger.

• Imperfections

Le terme imperfection désigne ici les effets de non-idéalité de traitement du signal à émettre (gain, déphasage, retard…), du à de multiples causes technologiques : sensibilité dans la réalisation des éléments, désappariement, erreur de phase, coefficient de qualité…. Par exemple, un déséquilibre entre les voies des composantes I et Q du signal bande de base ou bien une désynchronisation des voies de phase et d’enveloppe dans le cas d’une architecture polaire (EER) entraine une modification du signal à émettre que l’on peut difficilement corriger car due à l’information elle-même (signal image par exemple ou présence du signal OL dans la bande utile). Là encore l’effet est vite perceptible sur le signal et entraine des remontées spectrales et un bruitage des points de la constellation. Une procédure de calibration spécifique est souvent nécessaire pour minimiser ces effets.

• Complexité de la conversion D/A

Elle caractérise la facilité d’implémentation et l’intégration des étages de conversion numériqueanalogique. Certaines architectures sont amenées à utiliser plusieurs DAC dans un but de traitement du signal (création de notches en décalant deux DACs) là où certaines n’en utilisent qu’un seul. Il faut également prendre en compte la vitesse d’horloge nécessaire à chacun des DACs. Il est difficile d’avoir des vitesses d’horloge de l’ordre de plusieurs centaines de MHz (du GHz) avec un bruit de phase ne détériorant pas l’EVM. Il faut aussi garantir une homogénéité dans le plan des fréquences utilisées (on préféra des multiples de la porteuse par exemple). Le but étant de disposer de plusieurs horloges différentes dans le circuit à partir d’une seule fréquence de référence.

• Puissance maximum obtenue en sortie

Ce paramètre peut être lié également aux critères du standard, puisque chaque standard défini une puissance maximale à ne pas dépasser à l’émission. En LTE, la puissance maximum à respecter est de 25dBm à titre d’exemple. Ce critère est également lié à l’implémentation de l’étage d’amplification dans ou hors de l’architecture. Quelle puissance l’architecture est elle capable de générer à sa sortie? Quel sera alors l’étage d’amplification qui devra être associé ? Ce critère est souvent lié à la technologie utilisée et donc à la façon d’intégrer l’amplificateur dans l’architecture. Dans le cadre des architectures « tout numérique » on aura une intégration maximale du système si même l’étage d’amplification est conçu en technologie CMOS. Les performances de cette technologie ne sont pas orientées vers la génération de signaux de puissance pourtant nous verrons des exemples de réalisation et d’intégration d’amplificateurs en CMOS fournissant des puissances de l’ordre de 26dBm.

• Consommation

La consommation peut être rédhibitoire lors de la conception d’un circuit. Certains éléments de l’architecture, pour fonctionner, doivent avoir une tension de polarisation et drainent un courant qui va directement impacter la consommation du circuit. Dans l’hypothèse où l’étage d’amplification est compris dans la conception de l’architecture, il faut également pendre en compte le rendement de l’amplificateur, fonction de la classe d’amplification, car la part de puissance consommée par cet élément est non-négligeable dans le bilan global. Il y a souvent un compromis multi critères lié à la puissance de sortie, la linéarité et la consommation du PA.

• Dimension du circuit

Les dimensions du circuit dépendent de deux facteurs. Le premier est la taille de gravure utilisée (130nm, 90nm, 65nm) en technologie CMOS. Le second est le nombre d’éléments actifs ou passifs que contient l’architecture. Si l’on prend l’exemple d’un étage de filtrage, il se peut que l’intégration des inductances pose problème. De même une architecture qui utiliserait trop d’éléments malgré une faible taille de gravure, verrait son avantage réduit, en raison de la place occupée et du faible coefficient de qualité.

• Nombre d’éléments externes à rapporter

Ce critère permet de voir si l’intégration n’est pas obtenue au détriment de l’ajout d’éléments extérieurs tels que des amplificateurs, ou des bancs de filtre. Par exemple si un système a un étage de filtrage peu reconfigurable, alors il faudra plusieurs filtres à des fréquences différentes. Suivant l’architecture utilisée, on peut être amené à utiliser différentes topologies d’étage d’amplification.

• Mise en forme du bruit et contraintes sur le filtrage

La limitation des émissions de bruit parasite hors bande afin de respecter les caractéristiques imposées par le standard, conduit à utiliser un ou plusieurs étages de filtrage. La contrainte imposée sur le ou les étages de filtrage dépend essentiellement du niveau de bruit mais également de la façon dont il est mis en forme par l’architecture (bruit proche et bruit lointain). Les DACs entrainent des remontées spectrales du fait du bruit de quantification. On peut donner l’exemple du modulateur Sigma Delta qui suivant la façon dont il est conçu, rejette plus ou moins loin ce bruit de quantification loin de la bande utile (noise shaping) [Stew, 1998]. Les caractéristiques du filtrage, essentiellement la sélectivité, s’en trouvent alors fortement modifiées. Les considérations des différentes technologies de filtrage possibles sont alors liées à cette mise en forme du bruit par l’architecture d’émetteur (rejection, pertes, compromis sensibilité/sélectivité). Le besoin de reconfigurabilité, lié au contexte de la multi-radio, vient alors complexifier le problème et définir un verrou technologique.

• Méthode de calibration

Il est important de connaitre la méthode de calibration de l’architecture. En fonction de la fréquence, de la puissance, voire même de la température, l’architecture a besoin d’être calibrée. D’un point de vue industriel il vaut mieux éviter d’avoir à faire une calibration en usine à la fois coûteuse et systématique, ne permettant pas d’adapter la calibration à chaque circuit. Cependant une autocalibration du système entraine l’ajout d’éléments supplémentaires dans l’architecture tels que des comparateurs ou des boucles de contre réaction apportant une complexité supplémentaire. Il y a un compromis à faire entre performances, coût et intégration.

|

Table des matières

Introduction

Chapitre I. Spécifications des émetteurs cellulaires dans le contexte de la radio reconfigurable

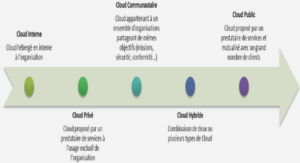

I.1. Concept de la radio cognitive

I.2. Intérêt de la multi-radio

I.3. Principaux standards de communication visés

I.3.1. Critères génériques de qualification des standards

I.3.2. GSM, EDGE et e-EDGE

I.3.3. UTRA FDD : W-CDMA, HSUPA et HSDPA

I.3.4. LTE FDD et TDD

I.4. Coexistences à prendre en compte dans la conception

I.5. Conclusion

Chapitre II. Architectures d’émission pour les applications multi-radio

II.1. Critères d’évaluation d’une architecture d’émission

II.1.1. Critères liés au standard

II.1.2. Critères liés à l’implémentation

II.2. Blocs dimensionnant une architecture d’émission

II.2.1. Conversion Numérique-Analogique

II.2.2. Modulateur IQ et transposition

II.2.3. Synthèse de fréquence

II.2.4. Filtrage RF

II.2.5. Amplification

II.3. Etude des architectures d’émission

II.3.1. Architectures d’émetteurs classiques

II.3.2. Architectures à techniques de linéarisation

II.4. Conclusion

Chapitre III. Dimensionnement d’émetteurs « tout numérique » pour des applications cellulaires

III.1. Des architectures analogiques aux architectures « tout numérique »

III.1.1. Evolution des blocs de mélange et de synthèse

III.1.2. Intégration de la transposition et de la pré-amplification

III.2. Contraintes liées à l’utilisation d’architectures « tout numérique »

III.2.1. Identification des contraintes

III.2.2. Identification des besoins en filtrage TX et des solutions possibles

III.2.3. Solution proposée et dimensionnement de l’architecture

Chapitre IV. Conception et réalisation d’un filtre RF passe bande reconfigurable à inductances actives en technologie CMOS 65nm

IV.1. Définition de la topologie du filtre

IV.1.1. Conception du filtre passe bande RF non reconfigurable à 1.95GHz

IV.1.2. Simplification de la structure

IV.1.3. Définition d’une loi de reconfigurabilité du filtre

IV.2. Conception d’une inductance active en technologie CMOS avancée

IV.2.1. Principe de fonctionnement d’une inductance active

IV.2.2. Choix de la topologie d’inductance active

IV.2.3. Conception et simulation de deux inductances actives

IV.2.4. Amélioration de la linéarité

Chapitre V. Implémentation et caractérisation du filtre à inductances actives en technologie CMOS 65nm

V.1. Implémentation du filtre à inductances actives

V.1.1. Plateforme technologique CMOS 65nm

V.1.2. Layout des inductances actives

V.1.3. Layout du filtre passe bande à inductances actives

V.2. Caractérisation des inductances actives sous pointes

V.2.1. Méthode de mesure

V.2.2. Performances mesurées de l’inductance active

V.2.3. Comportement en reconfigurabilité

V.3. Caractérisation du filtre passe bande

V.3.1. Mesure en socket de test

V.3.2. Extraction des phénomènes parasites

V.4. Comparaison à l’état de l’art et conclusion

Conclusion