Télécharger le fichier pdf d’un mémoire de fin d’études

Structures de composants MOS de puissance et principe de fonctionnement

Il existe deux types de transistors DMOS de puissance : les transistors discrets (structures verticales) et les transistors intégrés (structureslatérales en général). Les structures latérales LDMOS (latéral DMOS) sont utilisées pour des applications de puissance basses tensions radio fréquences [5] ne dépassant pas des tensionsde 100 Volts

Composants discrets

Le transistor VDMOS

La figure I.1 montre une cellule élémentaire du transistor VDMOS. Ce transistor est fabriqué en utilisant le processus de double diffusion MOS. La source et la grille sont localisées à la surface de la puce alors que le drain se situe à l’ arrière de la puce. À l’état passant, la tension grille-source Vgs est supérieure à la tension de seuil VT et un canal d’inversion de type N est ainsi formé en surface de la zone du canal permettant le passage du courant entre le drain et la source. Ce courant passe, en grande partie, dans le volume de la structure à travers la zone de drift N-. Une partie de ce courant passe en surface dans le canal et dépend de la mobilité des électrons dans la couche inversée.

La résistance du canal d’inversion est une limitation supplémentaire dans le cas des transistors VDMOS basse tension et elle est aussi importante dans le cas des nouveaux MOS de puissance fabriqués à base de carbure de silicium, à cause de la faible mobilité dans la couche inversée [6]. La zone de drift N- assure au transistor VDMOS la faculté de bloquer la tension à l’état bloqué. Pour une structure VDMOS bien optimisée [7,8], la tension de claquage dépend du dopage et de l’épaisseur de la zone de drift. En effet, pour bloquer des tensions très élevées, la zone de drift doit être faiblement dopée et suffisamment large pour permettre à la zone de charge d’espace de s’étendre. Par conséquent, cettezone large et faiblement dopée devient, à l’état passant, une résistance très grande que l’onne peut réduire que par augmentation de la surface active du composant ou par utilisation de nouveaux concepts comme le concept de la superjonction par exemple. L’utilisation de matériaux de forte énergie d’ionisation peut aussi être une très bonne solution à ce problème.

Il existe donc un compromis entre la résistance à l’état passant et la tension de claquage des transistors VDMOS de puissance.

Composants intégrés

L’intérêt de ces structures coplanaires est qu’elles peuvent être intégrées avec la partie traitement du signal analogique ou numérique pour le développement du système sur une puce (System-on-Chip : SoC). L’avantage de cette intégration réside dans l’élimination des éléments parasites dus aux fils de liaison dans lescircuits discrets, suppression de circuits d’interface entre la puissance et le contrôle et la réduction du poids et du coût de la fonction électronique de puissance réalisée sur une puce. Les technologies les plus connues sont : ‘‘SmartMOS’’ utilisée par Freescale et ‘‘BCD’’ util isée par ST Microelectronics. Le composant intégré le plus utilisé est le LDMOS caril est capable de fonctionner à des fréquences très élevées [5] et parce que ses troisélectrodes sont en surface, ce qui facilite son intégration.

Le transistor LDMOS

La figure I.3 montre une coupe schématique du transistor LDMOS classique. La tension de claquage est limitée dans cette structure à des tensions de l’ordre de 250 Volts. En effet, le claquage dans cette structure se produit généralement à la fin de la métallisation de grille (à cause de la faible épaisseur de l’oxyde de grille) ou à la jonction cylindrique PN -. Il dépend principalement du dopage de la zone de drift et de la distance Ld entre la fin de la métallisation de grille et le début de l’ouverturede la diffusion de drain [12, 13]. La couche enterrée N permet de limiter l’extension de la zone de charge d’espace dans la région N et d’éviter le perçage du substrat P. Elle peut permettre aussi d’annuler le gain du transistor parasite PN-P entre le substrat et la diffusion P source du transistor MOS de puissance.

Le courant électrique passe en surface de la structure et dépend de la distance L ; cette distance est appelée aussi longueur de la zone de drift. Plus cette distance est faible et plus la résistance à l’état passant du composant est faible. Malheureusement, la tension de claquage diminue quand Ld diminue et il a été démontré par des simulations umériquesn bidimensionnelles [13] qu’il existait une distance de drift optimale assurant une tension de claquage maximale pour un dopage de drift donné.

Ceci limite donc la densité d’intégration car le choix de la distance de drift, qui se trouve en surface de la structure, sera imposé par le compromis entre la tension de claquage et la résistance passante spécifique.

De plus, la présence des trois électrodes sur la face supérieure de la puce ne facilite pas la densification des cellules mises en parallèle pour former le transistor LDMOS de puissance. La source et le drain se présentent le plus souvent sous forme de bandes parallèles interdigitées.

Le transistor LUDMOS

Afin d’améliorer la tension de claquage des structures MOS latérales, M. Zitouni [13] a proposé une structure LDMOS intégrant une tranchéed’oxyde dans la zone de drift à la fin de métallisation de grille. Cette structure (figure I6),. appelée LUDMOS, permet de réduire le champ électrique en surface. Zitouni a ensuite proposé, en essayant de réduire la résistance passante spécifique, plusieurs variantes [13] de cette structure en éliminant la distance entre la tranchée et le drain (structure 2), puis en remplissant la tranchée par le polysilicium de grille (structure 3) et, enfin, en surdopant la surface de la zone de drift (structure 4).

Malgré l’allongement du trajet du passage du courant cette structure permet d’obtenir un meilleur compromis entre la résistance passante spécifique et la tension de claquage comparée à une structure LDMOS conventionnelle de même tension de claquage. À l’aide de simulations bidimensionnelles, il a été montré [13]que pour une tension de claquage de 60 Volts, la résistance passante spécifique n’est quede 0,6 m .cm2 contre 1,57 m .cm2 pour une structure LDMOS conventionnelle 60 Volts, soit une réduction de plus de 60%.

|

Table des matières

Évolution des composants de puissance

Objectif de ce travail

CHAPITRE I : ÉTAT DE L’ART DES COMPOSANTS MOS DE PUISSANCE

I.1. Introduction

I.2. Structures de composants MOS de puissance et principe de fonctionnement

I.2.1. Composants discrets

I.2.1.1. Le transistor VDMOS

I.2.1.2. Le transistor MOS à tranchées

I.2.2. Composants intégrés

I.2.2.1. Le transistor LDMOS

I.2.2.2. Le transistor VDMOS up-drain

I.2.2.3. Le transistor LUDMOS

I.3. Caractéristiques statiques d’un transistor VDMOS de puissance

I.3.1. Tension de claquage

I.3.1.1. Cas d’une jonction plane infinie en non limitation ‘‘Non Punch Through’’ (NPT)

I.3.1.2. Cas d’une jonction plane en limitation ‘‘Punch Through’’ (PT)

I.3.2. Résistance à l’état passant

I.3.2.1. Résistance du canal

I.3.2.2. Résistance d’accès

I.3.2.3. Résistance de drift

I.3.2.4. Les autres résistances

I.3.3. Limite du silicium des transistors DMOS verticaux

I.3.4. Limite du silicium des transistors DMOS latéraux

I.4. Quelques solutions pour dépasser (ou « briser ») la limite dite du silicium

I.4.1. Transistors MOS de puissance à Superjonction

I.4.2. Composants MOS à îlots flottants : le transistor FLIMOS

I.5. Matériaux semi-conducteurs à grand gap pour l’électronique de puissance

I.5.1. Introduction

I.5.2. Compromis « résistance passante spécifique / tension de claquage »

I.6. Conclusion

CHAPITRE II : ANALYSE STATIQUE ET DYNAMIQUE DU TRANSISTOR FLIMOS DE PUISSANCE

II.1. Introduction

II.2. Approche analytique unidimensionnelle

II.2.1. Tension de claquage

II.2.2. Résistance à l’état passant

II.2.2.1. Résistance du canal

II.2.2.2. Résistance d’accès

II.2.2.3. Résistance de drift

II.2.2.4. Limite du silicium des structures FLIMOS verticales

II.2.3. Optimisation des structures FLIMOS verticales

II.2.4. Capacité grille-source Cgs

II.2.5. Capacité drain-source Cds

II.2.6. Capacité grille-drain Cgd

II.3. Simulation 2D et interprétation des résultats

II.3.1. Outil de simulation bidimensionnelle PISCES

II.3.2. Structure DMOS verticale

II.3.2.1. Structure FLIMOS 900 Volts

II.3.2.1.1. Simulation de la tenue en tension et de la résistance passante spécifique de la structure VDMOS 900 Volts

II.3.2.1.2. Structure FLIMOS 900 Volts à trois îlots flottants

II.3.2.2. Structure FLIMOS 73 Volts

II.3.2.3. Conclusion

II.3.3. Structure latérale

II.3.3.1. Structure LDMOS conventionnelle

II.3.3.2. Structure FLIMOS latérale 60 Volts à deux îlots flottants

II.3.3.3. Paramètres de la structure FLIMOS

II.3.3.4. Simulation de la structure FLIMOS latérale en coupe

II.3.3.5. Simulation de la partie supérieure de la structure en surface

II.3.3.6. Résistance passante spécifique

II.3.3.7. Conclusion

II.3.4. Impact des îlots sur les performances dynamiques

II.3.4.1. Capacité grille-source

II.3.4.2. Capacité drain-source

II.3.4.2.1. Structure FLIMOS verticale à un îlot flottant 73 Volts

II.3.4.2.2. Structure FLIMOS verticale à 9 îlots flottants 900 Volts

II.3.4.3. Capacité grille-drain

II.3.4.3.1. Structure FLIMOS verticale à un îlot flottant 73 Volts

II.3.4.3.2. Structure FLIMOS verticale à 9 îlots flottants 900 Volts

II.3.5. Conclusion

II.4. Conclusion

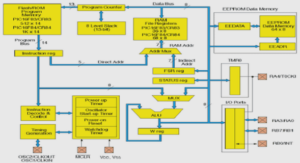

CHAPITRE III : MODÉLISATION SPICE DU TRANSISTOR FLIMOS VERTICAL

III.1. Introduction

III.2. Approche physique de la modélisation

III.2.1. Modèle statique

III.2.1.1. Zone du canal

III.2.1.2. Nouveau modèle SPICE du générateur de courant

III.2.1.3. Zone d’accès

III.2.1.4. Zone de drift

III.2.1.5. Diode Dbody

III.2.1.6. Extraction des paramètres statiques

III.2.1.6.1. Tension de seuil VT0 et facteur de transconductance KP

III.2.1.6.2. Paramètres θ, VMAX et ETA

III.2.1.6.3. Résistances Ra et Rbulk

III.2.1.7. Validation du modèle statique

III.2.2. Modèle dynamique

III.2.2.1. Capacité grille-source Cgs

III.2.2.2. Capacité grille-drain Cgd

III.2.2.3. Capacité drain-source Cds

III.2.2.4. Extraction des paramètres dynamiques

III.2.2.4.1. Mesures des capacités inter-électrodes Ciss, Crss et Coss

III.2.2.4.2. Détermination des paramètres Cj0, Vj et m

III.2.2.5. Validation du modèle dynamique

III.2.2.6. Simulation du ‘‘gate charge’’

III.3. Conclusion

CONCLUSION GÉNÉRALE

BIBLIOGRAPHIE

Télécharger le rapport complet