Télécharger le fichier pdf d’un mémoire de fin d’études

Architectures des émetteurs

Le synoptique simplifié d’un émetteur radio est proposé Figure 1.3.

La structure d’un émetteur radio peut être découpée selon les blocs suivants :

• Bloc numérique : c’est le bloc qui gère toute la partie « traitement bande de base des signaux » de l’équipement.

Dans ce bloc, différentes fonctions sont réalisées pour la mise en forme du signal avant qu’il ne soit émis :

• Le codeur

Le bloc numérique ne traite que des signaux binaires. Le codeur permet éventuellement de supprimer des éléments binaires non significatifs (compression de données ou codage de source), ou au contraire d’introduire de la redondance dans l’information en vue de la protéger contre le bruit et les perturbations présentes sur le canal de transmission (codage de canal).

• Le modulateur numérique

La modulation a pour rôle d’adapter le spectre du signal au canal (milieu physique) dans lequel il est émis. Eventuellement, le signal peut être généré autour d’une fréquence porteuse, si la plateforme de traitement numérique peut la fournir.

• Le filtrage

Le filtrage permet de mettre en forme les signaux traités. Certains filtres présents dans le bloc numérique tel que le filtre de Nyquist sont nécessaires pour limiter la bande des signaux à émettre tout en évitant les phénomènes d’interférences inter-symboles qui peuvent dégrader de manière significative la qualité du signal à la réception. Il s’agit bien souvent du filtre en cosinus surélevé (Root Raised Cosine, RRC) qui permet de réduire la bande du signal numérique à un signal numérique de bande , où est le coefficient de retombée appelé aussi roll-off et , la durée d’un symbole.

• Bloc analogique BF

Dans ce bloc sont réalisés certaines opérations telles que la conversion numérique analogique et éventuellement une transposition de fréquence en bande intermédiaire.

• Bloc RF

Le rôle de ce bloc est principalement la conversion du signal sur une porteuse RF ainsi que l’amplification du signal à émettre.

L’architecture, ainsi décrite Figure 1.3 n’est qu’une vue simpliste de la réalité. Dans ce chapitre, les principaux types d’architectures qui peuvent être rencontrés dans la littérature sont exposés brièvement ainsi qu’une présentation de ce qu’est la radio logicielle qui représente les futurs équipements de radiocommunication. Les émetteurs UHF/VHF actuellement commercialisés et utilisés comme référence sont présentés pour mettre en évidence les difficultés de conception et ainsi proposer une nouvelle architecture d’émetteur aussi robuste que flexible pour prendre en compte l’évolution éventuelle des normes.

Emetteur hétérodyne ou superhétérodyne

L’architecture de l’émetteur hétérodyne est présentée sur la Figure 1.4.

Ce type d’émetteur possède un changement de fréquence. Les signaux analogiques en bande de base I et Q sont transposés à une fréquence intermédiaire grâce à deux mélangeurs en quadrature et recombinés. Le signal ainsi obtenu est filtré pour supprimer les harmoniques de avant d’être transposé à la fréquence mais aussi . Ces deux fréquences sont le résultat du mélange avec l’oscillateur local . Un filtre passe-bande est ensuite utilisé pour filtrer la bande indésirable . L’intérêt de ce principe basé sur une fréquence intermédiaire fixe , réside dans le fait qu’il diminue les contraintes de filtrage. Il s’agit d’une architecture qui convient autant aux modulations à enveloppe non constante qu’aux modulations à enveloppe constante. La modulation en quadrature étant effectuée à une fréquence relativement faible par rapport à la fréquence RF, le désaccord de phase entre les voies I et Q est beaucoup plus faible comparé à une architecture homodyne [7].

Les fréquences image et utile sont de même puissance. Une atténuation de la fréquence image d’environ 50 à 60 dB est généralement suffisante pour éviter toute interférence. Le second filtre passe bande d’un ordre élevé, reste difficile à réaliser en termes d’encombrement et de coût (il induit une surconsommation non négligeable). De plus, il est passif et ne peut pas être intégré sur une puce avec les autres composants de la chaîne RF [7].

Emetteur à conversion directe ou homodyne

Dans les émetteurs homodynes, un seul étage de conversion en fréquence est présent comme illustré sur la Figure 1.5.

Le signal bande de base est directement modulé à la fréquence RF d’émission sans passer par une fréquence intermédiaire FI. Cette architecture, aussi appelée architecture zéro-FI en raison de l’absence de fréquence intermédiaire, est très compacte (peu de composants) et peut être facilement intégrée. Elle convient aux applications de type WCDMA où la surface et la consommation de courant sont des critères déterminants [8]. Toutefois, cette architecture souffre d’un important handicap : les phénomènes d’ « injection pulling » et « injection locking » [9] [10]. Ces phénomènes interviennent en raison de la proximité entre l’oscillateur local et l’amplificateur de puissance. Lorsque deux systèmes oscillants se trouvent proches l’un de l’autre, ils ont tendance à s’accorder à la même pulsation par couplage. La puissance du signal modulé en sortie de l’amplificateur de puissance étant bien supérieure à celle de l’OL, le spectre de l’OL est dégradé par le bruit généré en sortie de l’amplificateur de puissance. On parle alors d’ « injection pulling » lorsque l’amplitude du signal RF change et « injection locking » lorsque la pulsation de l’OL varie [7]. Une bonne isolation entre l’étage de transposition et l’étage d’amplification permet d’atténuer le phénomène.

Emetteur Low-IF (faible fréquence intermédiaire)

L’émetteur Low-IF repose sur le même principe que l’émetteur hétérodyne à la différence que la fréquence d’OL est beaucoup plus basse. Le premier étage de mélange à la fréquence FI peut éventuellement être réalisé dans un circuit numérique. Cette architecture présente les mêmes avantages que l’émetteur à conversion directe. De plus, l’émetteur à faible fréquence intermédiaire permet de s’affranchir des problèmes d’offset de l’architecture homodyne. Une mauvaise sélection des fréquences d’OL produit des harmoniques en sortie [8]. Le filtre passe-bas qui suit le VCO doit être sélectif afin de garantir la qualité du signal de sortie.

Phase Lock Loop (PLL) à modulation directe

Le schéma de cette architecture extrait de [11] est proposé Figure 1.6. Il s’agit d’une architecture qui ne convient qu’aux modulations à enveloppe constante. Elle a été inventée pour répondre aux fortes contraintes de la norme GSM concernant le bruit dans la bande de réception [8] [9]. Le signal RF à amplifier est généré en sortie du VCO de la PLL. La sortie du VCO est injectée dans un comparateur de phase pour fournir un signal d’erreur qui, après filtrage, pilote le VCO.

Cette architecture souffre aussi du phénomène de « pulling » décrit précédemment. Une bonne isolation entre l’étage d’amplification et le VCO est nécessaire.

Conclusion

Les architectures présentées dans cette section sont des architectures qui peuvent être qualifiées de « traditionnelles ». Compte tenu de la multiplication des standards de communication, des besoins de débit de données de plus en plus élevés qui nécessitent l’utilisation de modulations de plus en plus complexes, de la volonté d’avoir des équipements « multi-standards » ou « multi-normes » que ce soit pour la navigation aérienne, la téléphonie mobile ou encore pour une utilisation militaire, la radio-logicielle est un concept de plus en plus développée même si à l’étape actuelle, une architecture radio logicielle idéale pour les fréquences porteuses visées est impossible en raison des différents verrous technologiques. Le paragraphe suivant détaillera les apports de la radio logicielle ainsi que ses avantages dans la conception des équipements de communications modernes.

Radio Logicielle

Le Dr. Joseph Mitola est à l’origine du concept de Radio Logicielle (RL). Le terme « Software Radio » n’a pas plus d’une quinzaine d’années [12]. Le principe de la RL est d’obtenir qu’un système matériel puisse être reconfiguré pour exécuter plusieurs fonctions radios différentes. Il existe plusieurs définitions de ce qu’est la RL dans la littérature. Toutes ces définitions renvoient au même objectif : la possibilité de reconfigurer le matériel sans intervention « physique » ou changement matériel. L’objectif de la radio logicielle est de réaliser en numérique ce qui auparavant était analogique afin d’être le plus reprogrammable possible. La RL doit apporter une uniformisation (architecture générique) et une simplification du matériel en permettant une reconfiguration (téléchargement) de tout ou partie des fonctions de l’appareil. Un système basé sur la RL doit être capable de se reconfigurer selon les paramètres de son environnement et peut être mis à jour facilement et rapidement. La Figure 1.7 extraite de [13] présente une architecture radio logicielle idéale.

Les conversions analogique/numérique ou numérique/analogique s’effectuent tout de suite après l’antenne et l’architecture est entièrement reprogrammable car le processeur de signaux est directement relié aux convertisseurs. Une radio logicielle met en œuvre deux notions fondamentales :

• La plate-forme « matérielle »

Une plate-forme est l’ensemble des matériels radios et des systèmes de traitement qui hébergent une ou plusieurs formes d’onde.

• Le logiciel

Une forme d’onde est l’ensemble des transformations algorithmiques appliquées à l’information pour la convertir en signal radio. Une forme d’onde est entièrement logicielle et définit les caractéristiques du signal RF, dont la fréquence, la modulation et le format. Les radios logicielles permettent l’utilisation de multiples formes d’ondes, éventuellement dans différentes bandes spectrales, pour différents usages, voire même de façon simultanée.

Néanmoins, la RL décrite ci-dessus n’est pas réalisable. La limitation est essentiellement liée aux performances des convertisseurs analogiques numériques (CAN) ou numériques analogiques (CNA). Ceci oblige à se tourner vers des solutions intermédiaires, d’où l’intérêt de la SDR (Software Defined Radio) ou RLR (Radio Logicielle Restreinte).

Différence entre « Software Radio » et « Software Defined Radio »

Il s’agit d’une architecture qui peut être qualifiée de pragmatique [13] (Figure 1.8).

L’architecture idéale n’étant pas réalisable à l’heure actuelle, les nombreux travaux existants sont orientés vers une solution intermédiaire. Il s’agit de la RLR ou SDR. Contrairement à la radio logicielle idéale dans laquelle la conversion analogique numérique est réalisée au niveau de la RF, la conversion se fait au niveau de la FI pour la SDR. Il s’agit donc d’une solution composée nécessairement d’une partie analogique et d’une autre numérique.

Dans cette configuration, la partie analogique est divisée en deux nouvelles parties séparées par le convertisseur AN ou NA : la première (Analog Front End, AFE) qui reste analogique car non réalisable en numérique actuellement et la seconde (Digital Front End, DFE) numérique qui réalise certaines anciennes fonctions analogiques.

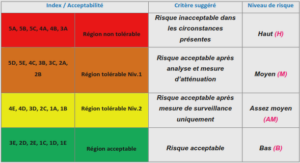

Il est possible d’effectuer une classification du type de radio en fonction de l’endroit où l’on fixe la limite entre le sous-système matériel et le sous-système logiciel, et incidemment en fonction de son degré de reconfiguration. La Wireless Innovation Forum (WIF) propose une classification (Tableau 1.2) des systèmes radio logicielles en fonction du degré de reconfiguration.

Avancées dans la Radio logicielle

Les dernières évolutions dans l’aéronautique en matière de RL concernent les radios interopérables dans le cadre de la mise en réseaux des unités sur le terrain. Celles-ci s’appuient sur le standard SCA (Software Control Architecture) et offrent une capacité haut débit sécurisé permettant des échanges de données, de phonie et de vidéo en réseau. Dans le domaine de l’ATC (Air Trafic Control), les RLs mises en œuvre pour assurer le contrôle des aéronefs militaires et civils sont de technologie duale. Leur moteur logiciel permet un choix de forme d’onde multiples mais n’est utilisé que pour des échanges de phonie et de données. Les travaux menés dans le cadre de la mise en œuvre du ciel unique européen au travers du programme SESAR [14] [15] et aux Etats Unis aux travers du programme NextGen [16] [17] tendent vers une gestion dynamique des bandes spectrales, de la forme d’onde, de la puissance émise en émission ou de la marge de sensibilité en réception [18].

Emetteurs UHF Telerad : défis de conception

Telerad développe, conçoit et fabrique entre autres des équipements radio dans les deux bandes (UHF et VHF). Les études menées dans le cadre de cette thèse ont été développées essentiellement sur des émetteurs UHF en mode VDL2. Ce mode se caractérise principalement par la modulation D8PSK. Précisons toutefois qu’il n’existe pas de spécifications de l’ETSI pour les émetteurs UHF avec une modulation D8PSK. Ce mode a été privilégié en raison de toutes les difficultés qu’il concentre dans la conception d’émetteur radio RF (UHF et VHF confondus). Les spécifications seront dès lors celles de l’EN 301 841-1 pour la VHF VDL en mode 2 à l’exception de la bande de fréquence qui sera celle de l’UHF (225 MHz – 400 MHz).

Les classes d’amplificateur de puissance

La définition d’une classe d’amplification est directement liée à l’angle de conduction du courant de drain de l’amplificateur de puissance.

L’angle de conduction peut être défini par la portion du cycle du signal d’entrée RF pendant lequel le transistor génère du courant. Pour plus de détail, le lecteur pourra se référer aux documents de [21], [22] et [23] qui décrivent en détail le principe des différentes classes d’amplificateur de puissance en fonction de la polarisation du transistor. Ainsi les classes A, AB, B et C. sont parmi les classes les plus utilisées. Il existe d’autre classes d’amplificateurs appelées classes commutées. Dans ces classes, le transistor est adapté de manière spécifique pour lui permettre de travailler en mode commuté garantissant de grands niveaux d’efficacité énergétique [21]. Ce sont les classes D, E et F.

Classes A, AB, B et C

• L’amplificateur de classe A possède une caractéristique linéaire et les signaux amplifiés subissent des distorsions faibles au prix d’un rendement également faible. En effet, le rendement maximal théorique d’un amplificateur de classe A est de 50% [24] [19] mais en raison des exigences de linéarité des applications,

le rendement est plutôt limité à 25%. L’angle de conduction vaut , c’est-à-dire que le transistor conduit tout le temps. Cette classe d’amplificateur est utilisée pour l’étage de pré-amplification où une forte efficacité n’est pas requise, efficacité qui est assurée par le dernier étage d’amplification. Pour des applications dont la durée de vie de la batterie (donc efficacité énergétique importante) est un enjeu important, l’utilisation de cette classe d’amplificateur ne convient pas.

• Le rendement d’un amplificateur de classe B est sensiblement meilleur que celle d’un amplificateur de classe A. Il atteint 78% [24] [19] tout en fournissant un certain niveau de linéarité. L’angle de conduction pour cette classe est égal

• La classe AB offre un bon compromis entre linéarité et efficacité énergétique.

L’angle de conduction est compris entre et . C’est la classe la plus exploitée.

• L’amplificateur de classe C a une caractéristique non linéaire très prononcée.

L’angle de conduction est inférieur à . Il en résulte de tels niveaux de distorsions des signaux amplifiés que ces amplificateurs ne conviennent pas aux applications nécessitant un niveau de linéarité élevé.

Le Tableau 2.1 extrait de [19] et [25] résume les caractéristiques des classes d’amplificateurs les plus couramment utilisées.

|

Table des matières

Chapitre 1. Normes et architectures d’émetteurs

1.1. Normes : évolutions et contraintes

1.2. Architectures des émetteurs

1.2.1. Emetteur hétérodyne ou superhétérodyne

1.2.2. Emetteur à conversion directe ou homodyne

1.2.3. Emetteur Low-IF (faible fréquence intermédiaire)

1.2.4. Phase Lock Loop (PLL) à modulation directe

1.2.5. Conclusion

1.3. Radio Logicielle

1.3.1. Différence entre « Software Radio » et « Software Defined Radio »

1.3.2. Objectifs de la SDR

1.3.3. Avancées dans la Radio logicielle

1.3.4. Emetteurs UHF Telerad : défis de conception

1.4. Conclusion

Chapitre 2. Amplificateur de puissance et linéarisation des émetteurs

2.1. L’amplificateur de puissance

2.1.1. Les classes d’amplificateur de puissance

2.1.2. Caractéristiques AM/AM et AM/PM

2.1.3. Modélisation d’un amplificateur de puissance

2.1.4. Quantification des distorsions : ACPR, EVM et RSB

2.1.5. Amplificateur de puissance : compromis entre rendement et linéarité

2.2. Les techniques de linéarisation et d’amélioration de rendement

2.2.1. Techniques de contre réaction ou feedback

2.2.2. La prédistorsion

2.2.3. La feedforward

2.2.4. Techniques d’amélioration du rendement

2.3. Conclusion

Chapitre 3. Etude comparative de quelques architectures d’émetteurs radio

3.1. Méthodologie de travail

3.2. Etat de l’art des convertisseurs

3.2.1. Principes de bases

3.2.2. Les différents types d’architectures de CANs et CNAs

3.3. Architecture 1 : Architecture boucle cartésienne idéale

3.3.1. Limites technologiques : les CANs et CNAs

3.3.2. Limites technologiques : le filtre passe-bande

3.4. Architecture 2 : architecture boucle cartésienne réalisable

3.5. Architecture 3 : l’EER

3.6. Architecture 4 : Architecture EER associée à une boucle de retour

3.7. Conclusion

3.8. Etude des deux architectures retenues

3.8.1. Etude quantitative et qualitative : Dimensionnement des deux architectures

3.9. Conclusion

Chapitre 4. Modélisation et optimisation de l’EER

4.1. Délai entre les voies d’amplitude et de phase

4.2. Commande du gain de l’AP

4.2.1. Etat de l’art de la correction de la commande de gain

4.2.2. L’étage d’amplification

4.2.3. Commande du gain de l’AP : mise en évidence des non-linéarités

4.2.4. Modélisation et correction de la commande de gain

4.3. Génération du signal RF à enveloppe constante

4.3.1. Déphaseur commandé en tension

4.3.2. Le synthétiseur de fréquence

4.3.3. Le modulateur IQ

4.4. Simulation de la chaîne complète

4.4.1. Méthode EER sans boucle

4.4.2. Chaîne complète avec la boucle de retour

4.5. Conclusion

Chapitre 5. Validation expérimentale

5.1. Partie Numérique

5.1.1. Plateforme FPGA et carte convertisseurs

5.1.2. Implémentation VHDL – format et opération

5.1.3. Traitement « bande de base » : les blocs numériques

5.2. Partie RF : modulateur IQ + étage d’amplification

5.2.1. Réalisation

5.2.2. Résultats

Télécharger le rapport complet